| ATM-757 |     | 7    | . NO. | SISTER |

|---------|-----|------|-------|--------|

| PAGE _  | i   | OF _ | 62    |        |

| DATE    | 5/7 | '/68 |       |        |

No FURTHER WORK AS OF 9 JULY 65 - R.W.

FINAL REPORT

OF STUDY EFFORT AUTHORIZED UNDER

ALSEP CCP 90

Prepared by: W. Tosh

Approved by: Approved by:

| ATM-757 |      | 7   |    |   |

|---------|------|-----|----|---|

| PAGE .  | ii   | OF. | 62 | • |

| DATE    | 5/7, | /68 |    | _ |

Page

### CONTENTS

| 1.0 | INTRO | DUCTION                   |                                                                                             |

|-----|-------|---------------------------|---------------------------------------------------------------------------------------------|

| 2.0 | A REV | TEW OF P                  | ERTINENT SYSTEM DEVELOPMENT                                                                 |

| 3.0 | STUDY | OBJECTI                   | IVES                                                                                        |

| 4.0 | 4.1   | CONCEPT<br>4.1.1<br>4.1.2 | Description System Performance Reliability Considerations - Thermal Differential Controller |

|     | 4.3   | 4. 2. 2<br>CONCEPT        | Description Packaging of the External Regulator Thermal Control Performance                 |

|     |       |                           | Description                                                                                 |

### 5.0 SUMMARY EVALUATION

| ATM  | ATM-757 |      | . NO. |

|------|---------|------|-------|

| PAGE | iii     | 0F _ | 62    |

| DATE | 5/7,    | /68  |       |

### LIST OF FIGURES

| 2.1  | Variation of Lunar Surface Temperature                     |

|------|------------------------------------------------------------|

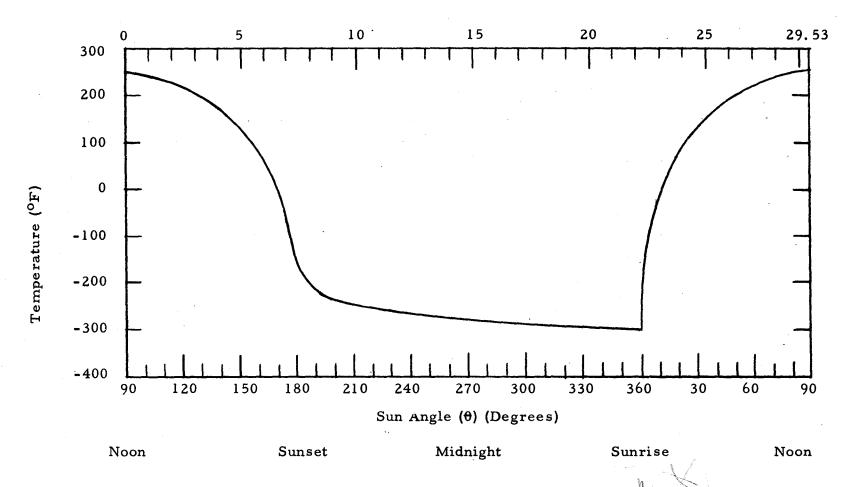

| 2.2  | PCU Dissipation vs. PCU Output                             |

| 4.1  | Present ALSEP Configuration                                |

| 4.2  | Functional Diagram - Concepts I and II                     |

| 4.3  | Functional Diagram - Concept III                           |

| 4.4  | Functional Diagram - Concept IV                            |

| 4.5  | Thermal Differential Controller                            |

| 4.6  | Power Dissipation in Shunt Regulator                       |

| 4.7  | Thermal Proportional Controller                            |

| 4.8  | PCU Circuit Diagram                                        |

| 4.9  | Regulator Module                                           |

| 4.10 | Regulator Electrical Interface                             |

| 4.11 | Thermal Control - Heat Pipe Configuration                  |

| 4.12 | Heat Pipe, Configuration & Performance                     |

| 4.13 | Thermal Control - Thermal Switch Configuration             |

| 4.14 | Hughes Thermal Switch                                      |

| 4.15 | Regulator Temperature for Various Thermal Control Concepts |

| 4.16 | Concept IV - Functional Flow Diagram                       |

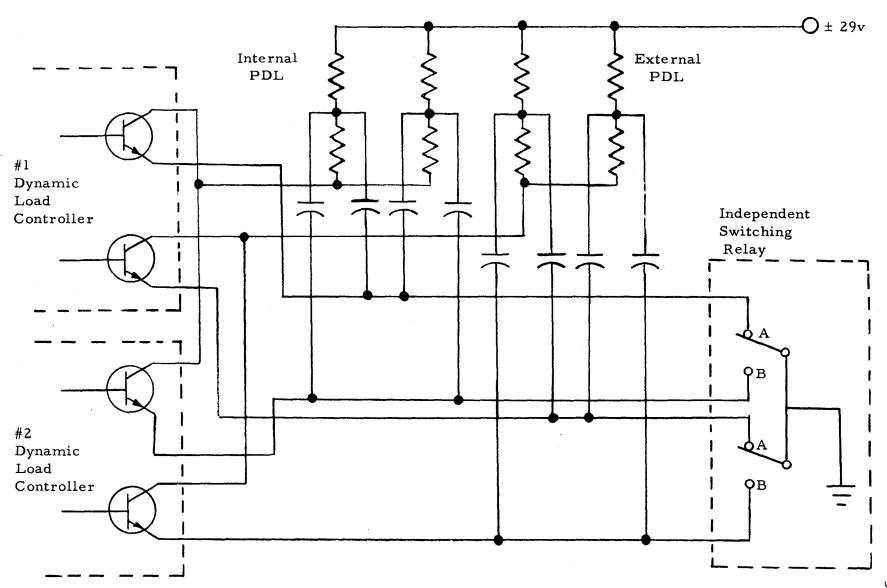

| 4.17 | Dynamic Load Controller                                    |

| 4.18 | Dynamic Load Timing Diagram                                |

| 4.19 | Redundant Mechanization - Method A                         |

| 4.20 | Redundant Mechanization - Method B                         |

|      |                                                            |

### TABLES

| I    | RANGE OF OPERATIONAL POWER DEMANDS                    |

|------|-------------------------------------------------------|

| II   | CENTRAL STATION THERMAL CONTROL - PRESENT PERFORMANCE |

| III  | FAILURE MODES ANALYSIS OF CONCEPT I                   |

| IV   | FAILURE MODES ANALYSIS OF CONCEPT II                  |

| V    | POWER DISSIPATION IN REGULATOR PACKAGE                |

| VI   | PCU REGULATOR PACKAGE THERMAL PERFORMANCE             |

| VII  | SUNSHIELD CONFIGURATION THERMAL PERFORMANCE           |

| VIII | DRT CONFIGURATION THERMAL PERFORMANCE                 |

| IX   | FAILURE MODES ANALYSIS - CONCEPT IV                   |

| X    | THERMAL PLATE TEMPERATURE VS INPUT POWER              |

| XI   | CENTRAL STATION DISSIPATION                           |

| XII  | EVALUATION OF SELECTED CONCEPTS                       |

|      |                                                       |

| NU.    |              | KEV    | . NU. |  |

|--------|--------------|--------|-------|--|

| ATN    | <b>1-</b> 75 | 7      |       |  |

| PAGE _ | 1            | _ OF _ | 62    |  |

| DATE   | 5/           | 7/68   |       |  |

#### 1.0 INTRODUCTION

At the request of NASA-MSC, a study was undertaken to investigate the use of the excess power from the RTG to provide positive assistance to the thermal control of the ALSEP central station which is presently maintained by completely passive means. This report presents descriptions of four concepts which, to varying degrees, might reduce the range of temperature swing during the lunar diurnal cycle. These concepts are also compared on the basis of thermal support effectiveness against the cost in terms of complexity, weight, and the feasibility of integrating into the existing hardware.

### 2.0 A REVIEW OF PERTINENT SYSTEM DEVELOPMENT

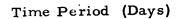

The temperature of the electronic equipment mounted in the ALSEP central station is constrained to acceptable limits during the changes of lunar surface temperature (Figure 2.1) by suitable use of surface finishes and coatings, special insulation materials and physical configurations. This concept of "static" thermal control was originally proposed when the electrical power being dissipated within the electronics items was essentially constant. This was valid until the regulator for the RTG output was transferred from pallet 2 to within the electronics bay of pallet 1. The net result of this action was to make the dissipation of the central station dependent on the amount of reserve power in the system. Since the reserve power varies as a function of both RTG output and equipment power demand, the electrical dissipation within the central station became a complex function of system operation. Thus, the mechanical design of the central station for its thermal control and the electrical design of the regulator controlling both RTG temperature and all the system voltages became tightly coupled, imposing severe constraints on each other.

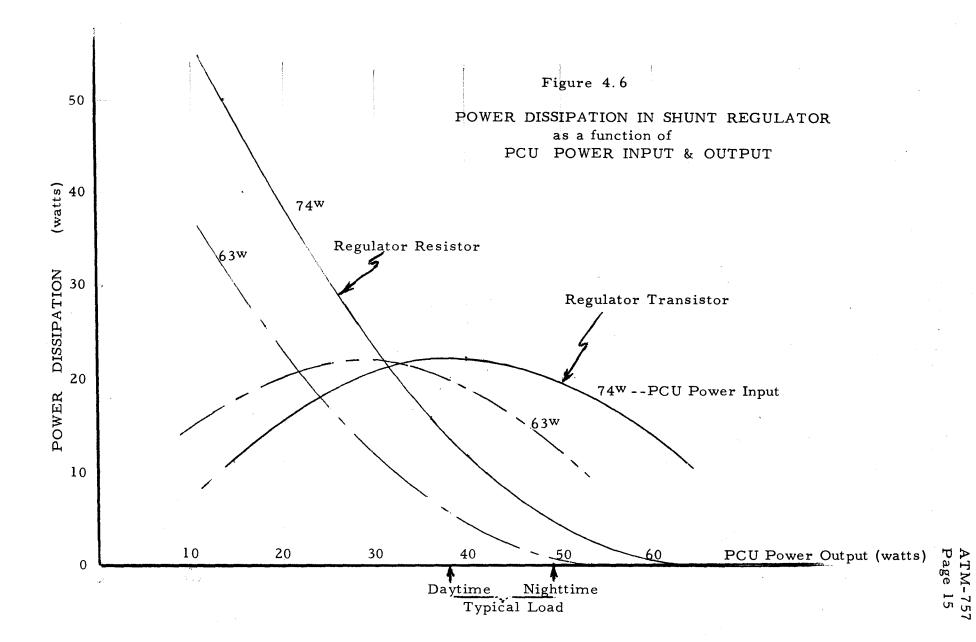

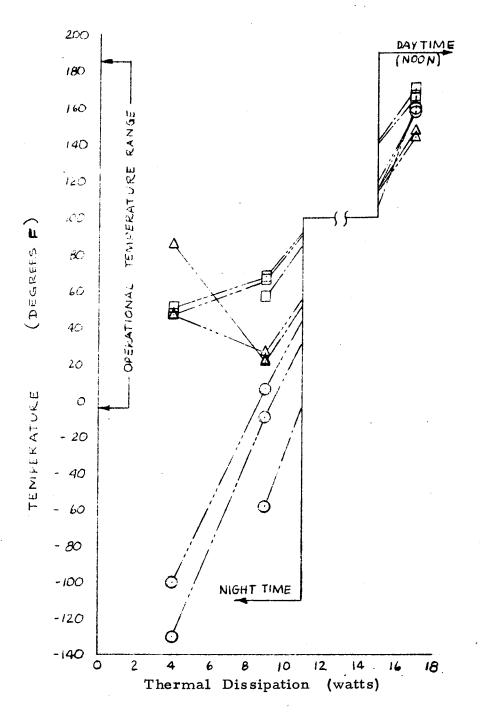

In the early days of ALSEP design the dynamic range of the electrical regulator (located partly in the PCU and partly external to the temperature-controlled area) was restricted to 30 watts because of the limitations imposed by stated variations in central station dissipation. As the design of the RTG and the experiments progressed it became evident that this regulator range was inadequate to cope with expected operational conditions. As confidence in the ALSEP thermal design was gained this regulator range was increased first to 40 watts and then to 55 watts. As illustrated in Figure 2.2 each increase in the dynamic control range of the regulator increased the range of variation of PCU internal dissipation for given variations in PCU output power.

Figure 2.1 Variation of Lunar Surface Temperature (Subsolar Point) During a Complete Lunation

ATM-75

Page 2

5/7/68

on

### Thermal Support of ALSEP Central Station Using Reserve Power

| NO.  |       | REV. | NO. |

|------|-------|------|-----|

| ATM  | [-757 |      |     |

| PAGE | 4     | 0F   | 62  |

| DATE | 5/7/  | 68   |     |

Because of the large number of possible operational configurations of an ALSEP system attainable either by command or by equipment failure (an example is given in Table I) it is not possible to precisely forecast the load on the PCU at any particular time during the year's mission. As further illustrated by Table I each configuration has a different (higher) load demand during lunar night than during lunar day. Similarly the RTG output is sensitive to ambient temperature.

To relieve the impact on the central station thermal control of this wide range of unschedulable loads on the PCU a number of emergency features have been incorporated into the system design. These are:

- a) 2 commandable resistive loads connected to the 29V line but physically dissipating electrical energy outside the thermally-controlled area. By suitable use of ON/OFF commands for each resistor load, increments of 7, 14 or 21 watts (nominal) may be added to the PCU output.

- b) a commandable resistive load connected to the 29V line and dissipating electrical energy into the thermal plate to which all electronic units are mounted. This resistive circuit is provided with a series-connected thermostat (sensing thermal plate temperature) which closes at about -10°F. These resistors will dissipate nominally 10 watts.

- c) 2 commandable resistive loads connected to the 29V line which will dissipate into the thermal plate (upon suitable commands) zero, 5 or 10 watts.

These facilities make it possible for the controller at MCC to make gross incremental changes (increases) in the load on the PCU in reaction to those contingent situations, such as failure of one or more experiments, in which the dissipation of excess power within the central station temperature-controlled area threatens to raise the thermal plate temperature above its design maximum.

It is apparent that the effectiveness of this control feature depends

- -continuous monitoring of central station temperatures and available reserve power

- -continuous availability of the MSFN and monitoring personnel

| NO.    |      | REV.   | NO. |

|--------|------|--------|-----|

| ATM.   | -757 |        |     |

| PAGE _ | 5    | _ OF _ | 62  |

| DATE   | 5/8  | 3/68   |     |

## TABLE I RANGE OF OPERATIONAL POWER DEMANDS

| F | EXPERIMENT |   |   | LOAD ON PCU (WATTS) |       |

|---|------------|---|---|---------------------|-------|

|   | STATUS     |   |   | LUNAR               | LUNAR |

| 1 | 2          | 3 | 4 | DAY                 | NIGHT |

|   |            |   |   | 16.0                | 13.5  |

| x |            |   |   | 21.1                | 21.3  |

| х |            | х |   | 25.4                | 27.8  |

| x | S          | S | S | 26.1                | 30.3  |

| x | Х          |   |   | 25.1                | 30,3  |

| х |            |   | X | 27.1                | 31.3  |

| х | S          | х | S | 27.4                | 33.8  |

| х | S          | S | Х | 30.1                | 34.3  |

| х | х          | X |   | 29.4                | 36.9  |

| х |            | X | х | 31.4                | 37.8  |

| х | S          | х | X | 31.4                | 37.8  |

| х | х          | S | S | 30.1                | 39.3  |

| х | х          |   | х | 31.1                | 40.3  |

| х | х          | х | S | 31.4                | 42.9  |

| х | х          | S | Х | 34.1                | 43.9  |

| X | х          | х | х | 35.4                | 46.8  |

### LEGEND

| SYMBOL | STATUS      |

|--------|-------------|

| Blank  | OFF         |

| S      | Standby     |

| X      | Operational |

| NO.     | REV. NO.     |

|---------|--------------|

| ATM-757 |              |

| PAGE 6  | of <u>62</u> |

| DATE    |              |

-a power management computer program available to the controller to permit him to take proper corrective action in any situation using the various commandable loads. (Both central station and lunar surface temperatures and gradients will determine whether the power should be dissipated in-board or outboard). Since it is very possible to overload the power source with these commandable loads, and hence put the system voltages out-of-regulation, considerable discretion must precede their usage.

### 3.0 STUDY OBJECTIVES

In the context of this present status of dependence of central station electronics thermal control on the system electrical operation, a study was undertaken at the request of NASA-MSC to investigate alternate methods of using the available excess power, under any and all conditions of operation, to assist in the temperature control of the central station electronics units. The following objectives were established to guide in the selection and evaluation of alternate concepts:

- a) maximum improvement in mission operation reliability

- b) reduced range of temperatures of central station electronics during lunar diurnal cycle.

- c) reduced dependency of central station performance (under contingency conditions) on MSFN availability.

- d) reduction or elimination of the dependency of central station electronics temperature on system operational mode.

- e) minimum impact on central station design to integrate a given concept into the system.

Four concepts were devised which were considered feasible and showed promise of meeting some or all of these objectives. The suggested concepts are:

Concept I - An additional set of voltage regulator resistors physically mounted within the thermally-controlled area and electrically selected (in place of the external resistors) at a pre-set temperature of the thermal plate.

| NO.    |      | REV  | . NO. |

|--------|------|------|-------|

| ATM    | -757 |      |       |

| PAGE _ | 7    | . 0F | 62    |

| DATE   |      |      |       |

Concept II-

Similar to concept I but with proportioning of the power fed into the external and internal regulator resistors as a function of thermal plate temperature.

Concept III-

Removal of the active element of the voltage regulator from the thermally-controlled area of the central station, to make the power dissipated within that area less variable.

Concept IV-

Incorporation of a load on the 29V output of the PCU which varies dynamically in such a manner as to maintain a constant current in the PCU regulator and which dissipates its energy inside or outside the thermally-controlled area as a function of the temperature of the thermal plate.

These concepts are described and evaluated in the following sections.

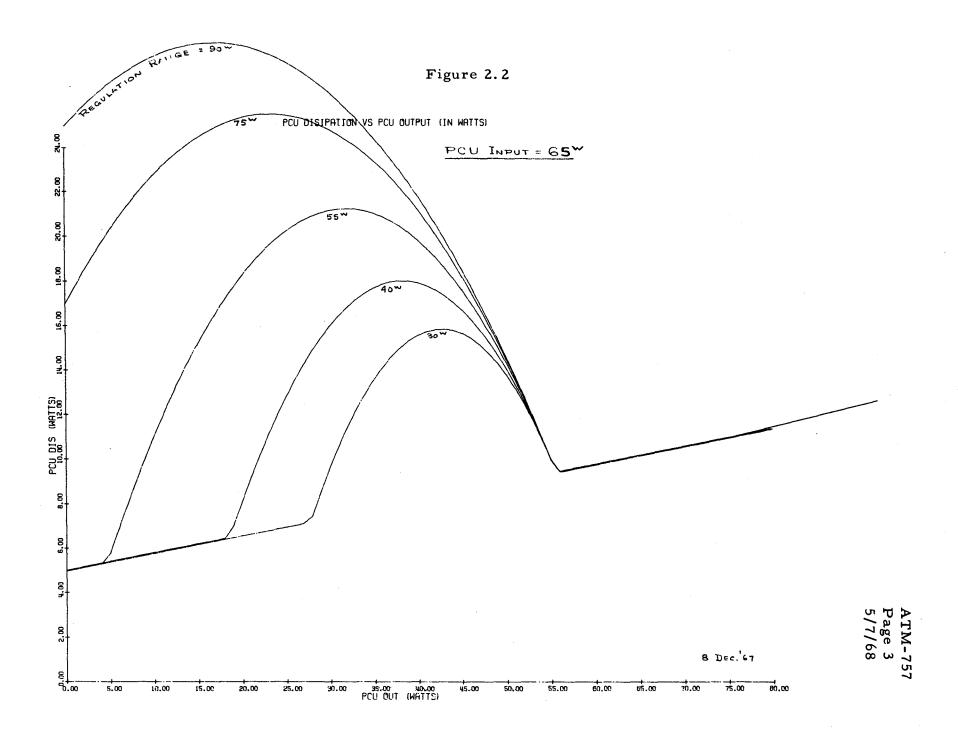

### 4.0 DESCRIPTION OF SELECTED CONCEPTS

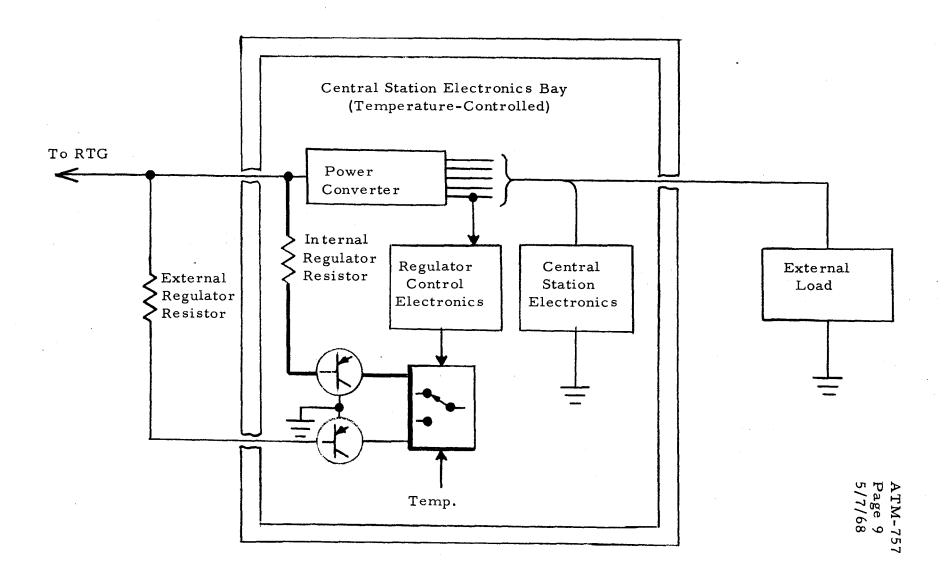

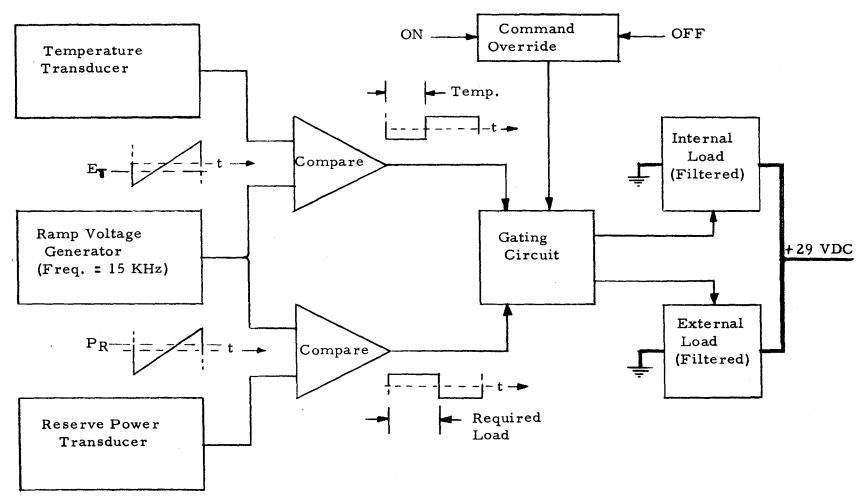

The scope of this study was established to investigate three alternate approaches to the usage of available reserve power to support the temperature control of the central station electronics. The most obvious fund of available reserve power is that dissipated in the externally mounted resistor element of the regulator circuit. (See Figure 4.1.) It is evident that it would be a help to dissipate this power inside the temperature-controlled area during lunar night. So the first concepts investigated (I and II) looked into the feasibility and impact of adding this particular increment of reserve power to the central station thermal plate upon demand (see Figure 4.2).

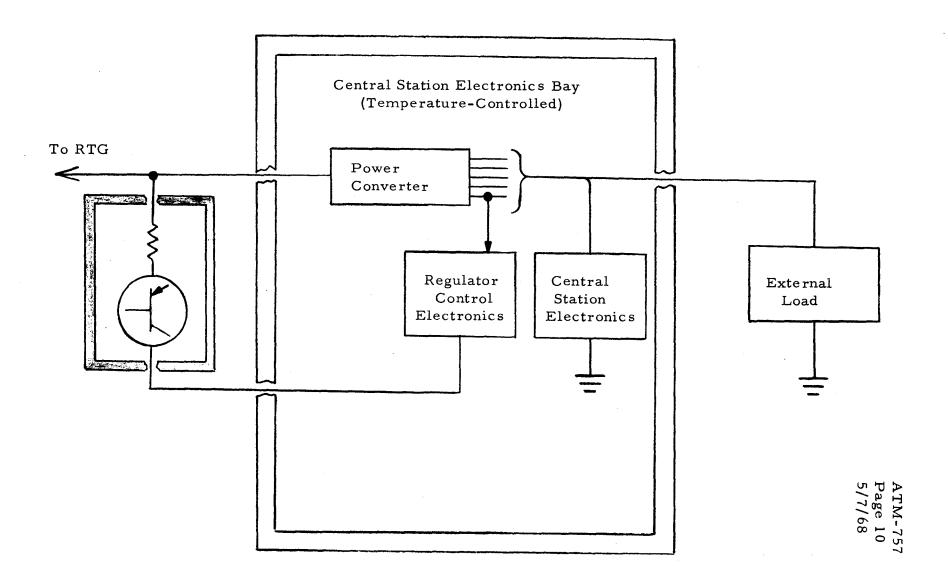

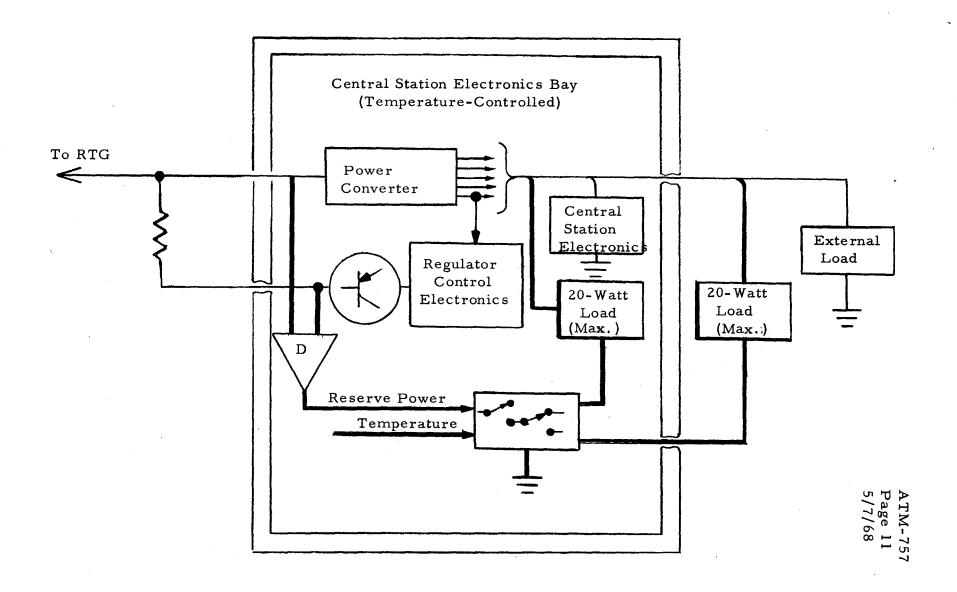

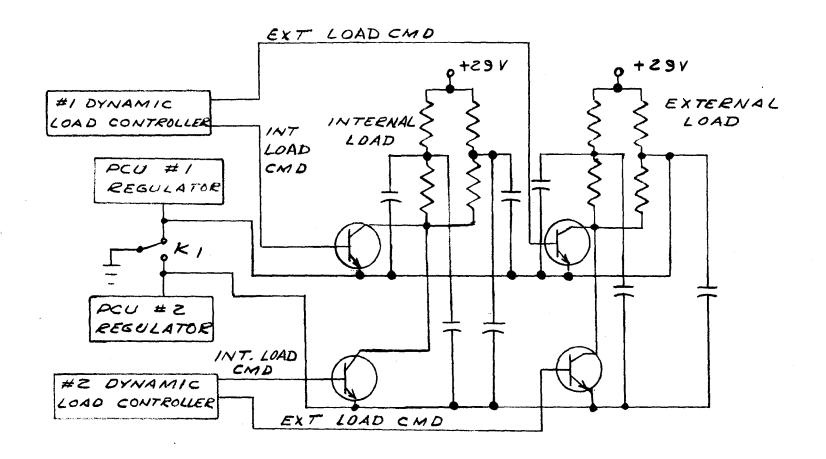

To investigate the feasibility of reducing the dissipation in the central station electronics during lunar daytime, two different concepts were studied, (a) Concept III, which proposed the removal of the reserve power dissipation from the PCU and from the electronics bay (i.e., from the thermally controlled area) of the central station (Figure 4.3), and (b) Concept IV, which proposes adding to the present central station design a dynamic load which stabilizes the PCU dissipation and places the available reserve power inboard or outboard as required by temperature, (see Figure 4.4).

Figure 4.1

Present ALSEP Configuration

Figure 4.2

Functional Diagram - Concepts I & II

Figure 4.3

Functional Diagram - Concept III

Figure 4.4

Functional Diagram - Concept IV

| NÓ.    | REV. NO. |

|--------|----------|

| ATM-7  | 57       |

| PAGE   | of 62    |

| DATE 5 | /7/68    |

### 4.1 CONCEPT I

### 4.1.1 Description

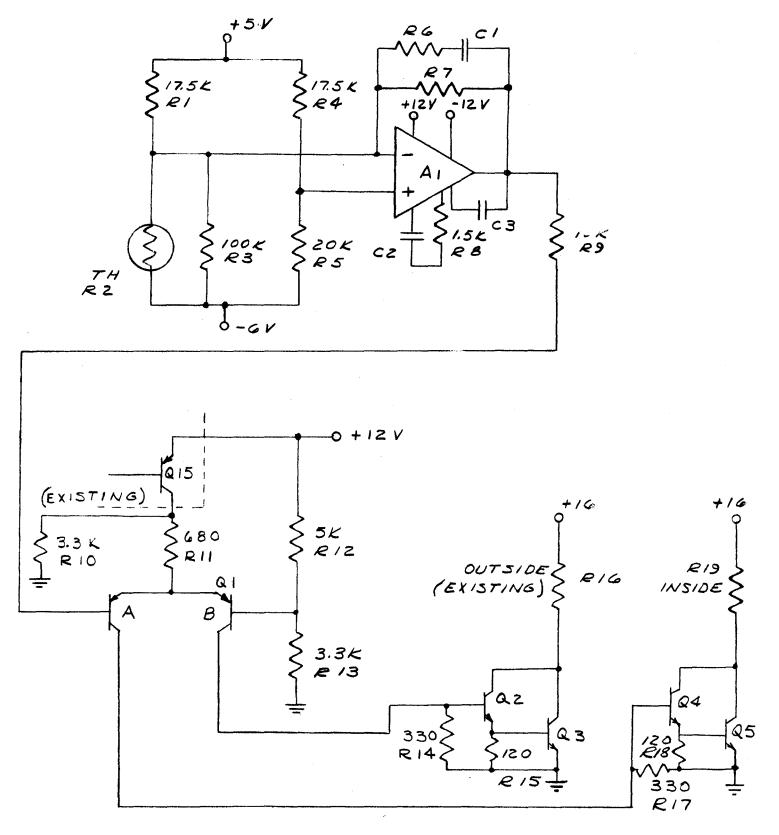

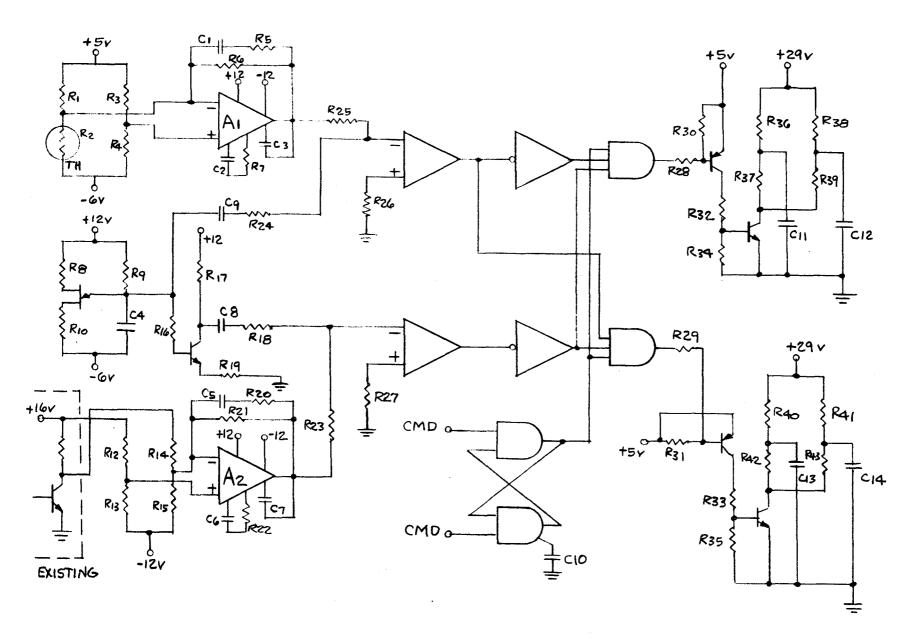

This concept can be implemented by a circuit such as that shown in Figure 4.5. The thermal plate temperature is sensed by the thermistor (R4) and converted to an ON/OFF signal by the bridge network and amplifier. Each of the present regulator shunt networks is replaced by two such networks, one with an externally-mounted resistor, and one with an internallymounted resistor (i.e. mounted on the thermal plate). The appropriate regulator network is selected by the temperature-dependent signal from the bridge amplifier. The temperatures at which transition from IN to OUT and OUT to IN are made can be independently set. With the circuit values shown the IN/OUT transfer is made at a thermal plate temperature of 75°F and the OUT/IN transfer at 25°F. The transfer rate between regulators is slow relative to the regulator time constant and at no time during switchover are both regulators open. This feature ensures that the effect of transfer on system voltage regulation is negligible. For compatibility with the present "ripple-off" circuit, a resistor/diode network is required to add in a measure of the current in the new regulator.

All the necessary control circuits for concept I can be packaged very compactly either in the form of a card similar to the dust detector electronics in the PDU or in a module form for mounting separately to the thermal plate. If the dust detector electronics were eliminated this control circuit could be integrated into the PDU by replacing the dust detector electronics printed circuit assembly with a new assembly. The central station harness would require modification to accommodate the circuit changes, and in addition, the new regulator resistors must be mounted to the thermal plate in appropriate locations. The PDU mother board and connectors would not require change since elimination of the dust detector would provide adequate input/output capability as presently designed.

If the controller were packaged in a separate module it could be mounted in the active seismic electronics location on ALSEP Flight Systems 1, 2, and 3. For Flight System 4, no space is available without reasignment of equipment locations. The central station harness would require modification and the thermal plate would require mounting holes for the control module and the regulator resistors.

Figure 4.5

-/2 V

120

R14

335

R16

120 I R17 =

| NO.    |       | REV  | . NO. |

|--------|-------|------|-------|

| ATM    | 1-757 | ·    |       |

| PAGE _ | 14    | OF _ | 62    |

| TAUE - |       | _ Or |       |

| DATE   | 5/7   | /68  |       |

### 4.1.2 System Performance

The thermal support provided to the electronics bay by concept I is limited to the increment of thermal dissipation that is contained in the regulator resistor added to the thermal plate when the internal regulator network is selected. The power dissipated in the regulator resistor is a non-linear function of PCU output for any given input power, as shown in Figure 4.6. Unfortunately, when this dissipation is added to the thermal plate (during lunar night) the power level is low, i.e. from 1 to 5 watts. The transfer temperatures established for concept I are as follows:

-central station temperature decreasing (transfer from external to internal regulator) 25°F.

-central station temperature increasing (transfer from internal to external regulator) 75°F.

The present design of ALSEP, as stated in section 2, has a number of commandable inboard (heater) and outboard loads which can be used to alter the central station power dissipation within the constraints of operational power requirements. Table II lists the ranges of temperature swing of the central station electronics for three values of input power and optimum usage of the various commandable loads.

TABLE II

CENTRAL STATION THERMAL CONTROL-PRESENT PERFORMANCE

|                |                        |                        | C/S     | 5 Temperate              | ıre Range,                | , <sup>o</sup> F                         |  |  |

|----------------|------------------------|------------------------|---------|--------------------------|---------------------------|------------------------------------------|--|--|

| ALSEP<br>Model | RTG<br>Power,<br>Watts | PCU<br>Loads,<br>Watts | Passive | With 21-<br>Watt<br>Dump | With<br>10-watt<br>Heater | With 21-watt<br>dump & 10-watt<br>Heater |  |  |

|                |                        |                        |         |                          | 1100001                   | Trouber                                  |  |  |

| Flights 1, 2   | 63                     | 38/49                  | 148     | 133*                     | 146**                     | 131                                      |  |  |

|                | 68                     |                        | 139     | 128*                     | 135**                     | 124                                      |  |  |

| Flight 3       | 63                     | 32/44                  | 142     | 121                      | 131                       | 110                                      |  |  |

|                | 68                     |                        | 134     | 120                      | 115                       | 101                                      |  |  |

| Flight 4       | 63                     | 36/42                  | 136     | 121                      | 122                       | 107                                      |  |  |

|                | 68                     |                        | 130     | 110                      | 111                       | 91                                       |  |  |

\*14 watt daytime commandable dump load. Ripple off of Experiment 4 occurs with 21 watt dump load.

\*\*5 watt nighttime heater. Ripple off of Experiment 4 occurs with 10 watt heater.

| NU.    |      | KEV    | . NO. |   |

|--------|------|--------|-------|---|

| ATM    | -757 |        |       |   |

| PAGE _ | 16   | . OF _ | 62    | _ |

| DATE   | 5/   | 7/68   |       | _ |

|        |      |        |       |   |

An analysis was performed of the impact of adding this increment of power dissipation to the central station. A set of typical operating conditions were assumed as follows:

- -ALSEP 1 equipment array

- -RTG power at central station input: 68 watts

- -PCU regulator range: 55 watts (nominal)

- -PCU output (functional) loads -during daytime: 38 watts -during nighttime: 49 watts

It was determined that the extra power dissipated inside the temperature-controlled area would raise the nighttime temperature by approximately 8°F. That is the temperature range for the passive thermal control method would be reduced from 139°F (Table II) to 131°F.

### 4.1.3 Reliability Considerations - Thermal Differential Controller

Table III provides a failure mode summary of the electronics associated with concept I. Although this concept is an integral part of the PCU regulator, the failure mode analysis is confined to the thermal controller. The effects of these failures are considered in their relation to the PCU regulator and ALSEP system.

The failure modes of the differential controller circuit can be categorized into three general classifications, and are summarized in the following paragraphs.

1. Degradation of the temperature sensing function, causing the differential temperature set-point levels to shift. Refer to paragraphs 1.1, 1.2, 1.3, 2.2, and 2.3 of Table III. This will cause the shunt regulator reserve power dissipation to be switched from internal to external (or vise versa) loads at different temperature limits. Aside from some deterioration in Central Station thermal control, the failure mode is not catastrophic in nature. This degraded mode of operation represents approximately 34% (Q1 = .00094692) of the failure probability of the Regulator/Differential controller circuit.

#### TABLE III FAILURE MODES ANALYSIS OF CONCEPT I

|      | ponent/                           |                                |                                                                                              | · · · · · · |                                                                                                     | Probability of |      | Failure Effect                                                                                                                                                                         |       |                                                                                                                                                            |         |

|------|-----------------------------------|--------------------------------|----------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Part |                                   | Failure M                      | ode                                                                                          | Failu       | re Cause                                                                                            | Occurrance     | Asse | embly                                                                                                                                                                                  | Syste | em                                                                                                                                                         | Remarks |

| 1.0  | Temperature<br>Sensing<br>Circuit | erro<br>indic<br>Cent          | sing circuit<br>oneously<br>cates high<br>tral Station<br>perature                           | 1.1         | Part failure causing<br>the Op-Amp output<br>voltage to swing<br>negative                           | .00010182      | 1.1  | If error signal is<br>greater than differ-<br>ential range ( 75°F)<br>the regulator will<br>switch to the External                                                                     | 1.1   | The C/S will operate cooler during the lunar night.                                                                                                        |         |

|      |                                   | erro<br>indic<br>Cent          | sing circuit<br>oneously<br>cates Low<br>tral Station<br>perature                            | 1.2         | Part failure causing<br>the Op-Amp output<br>voltage to swing<br>positive                           | . 00036463     | 1.2  | Shunt Resistor/Xstr. If error signal is greater than differential range (below 25°F set-point) the reg. will dissipate the reserve pwr. through the internal shunt resistor/transistor | 1.2   | The C/S temperature will increase during the lunar day.                                                                                                    |         |

|      |                                   | beco<br>Op- <i>l</i>           | sing circuit<br>omes unstable.<br>Amp goes into<br>Ilation.                                  | 1.3         | Failure within Op-<br>Amp's frequency<br>compensation and/<br>or feedback circuit.                  | .00013155      | 1.3  | The control loop<br>switching hysteresis<br>and/or slow switching<br>rate will be affected.                                                                                            | 1.3   | Negligible effect on the system.                                                                                                                           |         |

| 2.0  | Level Shifting<br>Circuits        | ing o<br>neou<br>and/<br>a hig | rnal level shift-<br>circuit erro-<br>usly defects<br>or simulates<br>gh Central<br>on temp. | 2.1         | The P-Channel FET Q4 is either biased off and/or failed source-to-drain infinite impedance.         | .00015483      | 2.1  | PCU Regulator will function normally during the lunar Day. When the C/S temp. drops below 25°F, the level shifter will not be able to switch to internal shunt regulator transistor.   | 2.1   | PCU will go out of regulation during Lunar Night. If failure is in PCU #1 automatic switchover will occur.                                                 |         |

|      |                                   | ing c<br>neou<br>or si         | rnal level shift-<br>circuit erro-<br>sly defects and<br>imulates a low<br>temperature.      |             | The P-Channel FET,<br>Q4 is either biased<br>on and/or failed low<br>impedance source-<br>to-drain. | . 00019017     | 2.2  | PCU Regulator will function normally during the lunar night.                                                                                                                           | 2.2   | During the lunar day the C/S will operate hotter since reserve pwr. cannot be completely switched outside the C/S. However, regulation will be maintained. |         |

#### TABLE III (Continued)

|                                                         |                                                                                                  |                                                                                                                   |                |                                                                                                                                                                                        |                                                                                                                                                                                                                                                                  | 5/7/68  |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Component/                                              |                                                                                                  |                                                                                                                   | Probability of | Failure Effect                                                                                                                                                                         |                                                                                                                                                                                                                                                                  |         |

| Part                                                    | Failure Mode                                                                                     | Failure Cause                                                                                                     | Occurrance     | Assembly                                                                                                                                                                               | System                                                                                                                                                                                                                                                           | Remarks |

| Level Shifting<br>Circuits (cont.)                      | 2.3 External level shifting circuit erroneously detects and/or simulates a high C/S temperature. | 2.3 The N-Channel FET, Q3, is either biased ON, and/or failed/ON impedance source-to-drain.                       | .00015876      | 2.3 PCU will function normally during the lunar day.                                                                                                                                   | 2.3 During the lunar night, the C/S will operate cooler because the reserve power cannot be switched completely into the C/S. Regulation will be maintained.                                                                                                     |         |

|                                                         | 2.4 External level shifting circuit erroneously detects and/or simulates a low C/S temperature.  | 2.4 The N-Channel FET, Q3, is either biased OFF, and/or failed infinite impedance source-to-drain.                | 4              | 2.4 PCU will function normally during the lunar night. When the C/S temp. increases above 75°F, the level shifter will be unable to switch to the External Shunt regulator transistor. | 2.4 PCU will go out-<br>of-regulation during the<br>lunar day. If the fail-<br>ure is in PCU #1<br>automatic switchover<br>will occur.                                                                                                                           |         |

| 3.0 Shunt Regula-<br>tor Transistor<br>Stage (Internal) | 3.1 Internal Shunt Regulator transistor fails in the cut-off mode.                               | 3.1 Shunt transistor Q5 fails open ce or drive circuit fails such that Q5 is biased OFF.                          | .00023589      | 3.1 PCU regulator will be controlled via the External Shunt Regulator Transistor during the lunar day.                                                                                 | 3.1 Above the set- point temperature of 75°F, the PCU regulator will function as the existing design do Between 25°- 75°F the External Shunt Regulator Transistor will absorb reserve power for the Internal Shunt Reg. Trans. Below 25°F PCU will not regulate. | 1       |

|                                                         | 3.2 Internal Shunt<br>Regulator Transistor<br>fails in the ON mode,                              | 3.2 Shunt Transistor Q5 fails short c <sub>e</sub> , or drive fails such that Q5 is biased on or into saturation. | .00024795      | 3.2 The PCU will probably go out-of-regulation. In addition the shunt regulator will dissipate more power.                                                                             | 3.2 If PCU goes out- of-regulation, automa- tic switchover to PCU #2 will occur. If regulation is main- tained but reserve power depleted, the Exp. Ripple-Off function will occur.                                                                              |         |

| NÓ.  |       | RE     | /. NO. |

|------|-------|--------|--------|

| ATM  | 1-757 |        |        |

| PAGE | 19    | . OF . | 62     |

| DATE |       |        |        |

- 2. If either the internal or the external shunt regulator transistor is inhibited (e.g. biased off), the PCU output voltages will remain in regulation during the time the "off" mode represents the normal operating state. (See Table III, para. 2.1, 2.4, and 3.1.) However, when the lunar environment requires a transition to the converse state (e.g. lunar day to lunar night), the PCU will not be able to maintain regulation. This failure mode represents approximately 28% (Q2 = .00077695) of the Regulator/Differential failure probability.

- 3. The third failure classification is excessive power dissipation in the regulator shunt loads. (See Table III, para. 3.2.) If the power dissipation becomes too excessive the PCU will go out-of-regulation. If operating on PCU #2 switching PCU's would probably be required via ground command. The PCU regulator would be expected to fail in this manner approximately 18% (or Q<sub>3</sub> = .0004959).

If the reliability objectives for ALSEP are to be retained, it is essential that the thermal Differential controller be redundant. That is, each PCU regulator be designed to operate with its own independent thermal control circuit. This is essential since the second failure category would constitute a single point failure source.

### 4.2 CONCEPT II

This concept is very similar to concept I in that an inside/outside shunt regulator is employed. In place of IN/OUT switching of the regulator resistor power, the amount of power in each regulator is proportionately controlled according to the central station thermal plate temperature.

This proportional control is accomplished by sensing the thermoplate temperature with a thermistor/amplifier combination and using this signal to control the dissipation in each regulator. Since the thermal time constant is very large, the response of this closed loop system will be very slow, and therefore will cause negligible effect on the output voltages. The

| NO.    |      | REV    | . NO. |  |

|--------|------|--------|-------|--|

| AT     | M-75 | 57     |       |  |

| PAGE . | 20   | _ OF _ | 62    |  |

| DATE   |      |        | •     |  |

I NÒ.

circuit constants shown in Figure 4.7 provide this proportional control feature between the limit temperatures of 40° F and 60° F. That is, all reserve power is dissipated internally at thermal plate temperatures lower than 40°F and the resisistor dissipation is all external to the central station at temperatures higher than 60° F. The thermal support of the central station with this concept is the same as with concept I when the thermal plate temperature is outside the proportional control limits. The smoother control of resistor power inboard and outboard provides a more favorable temperature inside the electronics bay during the transitional period.

#### 4.2.1 Description

Referring to Fig 4.7, the thermal plate temperature is sensed by the thermister bridge network. At the center temperature (50° F), the output of amplifier Al is biased to equal approximately +4 Volts by resistor R3 in the bridge network. This balances the differential pair; Q1, such that both of the shunt regulators are operating. The reserve power is then proportionally controlled inside and outside depending on the temperature of the Central Station Thermal plate.

The differential pair  $(Q_1)$  is added to the second last stage of the regulator  $Q_{15}$  (See Figure 4.7) as shown.  $Q_{1}B$  is based at 4VDC. The current to the shunt transistor can be directed to either shunt regulator dependent upon the voltage at the ouput of amplifier Al and hence the temperature. The loop gain of this controller is set by the feedback element of Al, and must take into account the slow thermal time constant and the gain in Al and Pl.

The packaging requirements of the thermal proportional controller are identical to concept I. This circuit can also be located in the PDU with little impact to that unit or in a module on the thermal plate. The same trade-offs exist with both concepts I and II.

#### Reliability Considerations 4.2.2

A failure mode summary of the thermal Proportional Controller circuit design is provided in table IV. Like concept I, the Proportional Controller design also becomes an integral part of the PCU regulator. comparative reliabilities of the two concepts indicates the proportional controller has a slight edge. An approximate reduction of 7% to the probability of failure (Q) would be realized using this concept. The general

Figure 4.7

THERMAL PROPORTIONAL CONTROLLER

| Component/                          | 77.00.00                                                                                              |                                                                                       | Probability of<br>Occurrance | Failure Effect                                                                                                                               |                                                                                                                                                                             |                                                                     |

|-------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Part                                | Failure Mode                                                                                          | Failure Cause                                                                         |                              | Assembly                                                                                                                                     | System                                                                                                                                                                      | Remarks                                                             |

| 1.0 Temperature<br>Sensing Circuit  | 1.1 Sensing circuit<br>erroneously indicates<br>high C/S temperature.                                 | 1.1 Part failure causing<br>the Op-Amp output voltage<br>to swing positive.           | .00010155                    | l, l Proportional to the signal error, the PCU Reg. will dissipate the reserve power primarily through the External Shunt Resistor.          | 1.1 Degradation of C/S thermal control during the Lunar Night causing the C/S temp. to decrease.                                                                            |                                                                     |

|                                     | 1.2 Sensing circuit erroneously indicates low C/S temperature.                                        | 1.2 Part failure causing the Op-Amp output voltage to swing negative.                 | .0003646                     | 1.2 Proportional to the signal error, the PCU Reg. will dissipate the reserve power primarily through the Internal Shunt Resistor/Transistor | 1.2 During the Lunar Day, the C/S thermal control system cannot minimize the Reserve Power Dissipation in the C/S, thus causing a high er operating temp.                   |                                                                     |

|                                     | 1.3 Sensing circuit<br>becomes unstable<br>Op-Amp goes into<br>oscillation.                           | 1.3 Failure within Op-Amps' frequency compensation and/or feedback circuit.           | .00013139                    | 1.3 Regulator will switch shunt regulators in and out. similar to a differential control system.                                             | 1.3 Negligible                                                                                                                                                              |                                                                     |

| 2.0 Differential<br>Amplifier Stage | 2.1 Differential Amp. erroneously responds to a high C/S temperature condition.                       | 2.1 Part failure or parameter shift causing a bias offset or hard-over output signal. | .00024367                    | 2.1 Proportional to the signal error, the differential stage will drive the External shunt reg. transistor harder.                           | 2.1 The C/S will operate cooler during the Lunar Night. If the error signal is "hard over" the PCU will function similar to present design capability.                      |                                                                     |

|                                     | 2.2 Differential Amp. erroneously responds to a Low C/S temperature condition.                        | 2.2 Same as 2.1 except in reverse direction.                                          | .00023137                    | 2.2 Proportional to the signal error the differential stage will drive the Internal shunt reg. transistor harder.                            | 2. 2 The C/S will operate hotter during the Lunar Day. If error signal is hard-over! the PCU will go out-of-regulation if C/S temp. increase above set-point level of 50°F. | 2.2 Automatic switch-<br>over will occur if<br>operating on PCU #1. |

|                                     | 2.3 Differential Amp, fails to provide sufficient drive signal to either shunt regulator transistors. | 2.3 The diffpair transistors fail in cut-off mode, or the emitter resistor opens.     | . 00002093                   | 2.3 PCU regulator becomes inoperative.                                                                                                       | 2.3 Loss of PCU regulation. Automatic switchover will occur if failure is in PCU #1.                                                                                        |                                                                     |

#### TABLE IV (Continued)

| Component/                                              |                                                                                                            |                                                                                                                          | Probability of | Failure Effect                                                                                                                                                                                                                         |                                                                                                                                                                                                                                      | I                                                                           |

|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| Part                                                    | Failure Mode                                                                                               | Failure Cause                                                                                                            | Occurrance     | Assembly                                                                                                                                                                                                                               | System                                                                                                                                                                                                                               | Remarks                                                                     |

| Differential<br>Amplifier<br>Stage (cont.)              | 2.4 Differential Amp. provides too much drive signal to both shunt regu- lator transistors simultaneously. | 2.4 Resistor fails open or diff-pair transistor are simultaneously driven into saturation.                               |                | 2.4 Both the Internal and External shunt regulator transistors will be "tracking" on and off together. As the drive from the diff. stage increases the reserve power decreases proportionately. PCU will probably go outof-regulation. | 2.4 If the reserve power is depleted, the Exp. Ripple-off function will occur. The C/S thermal control capabilit will become erratic. Th PCU will probably go out-of-regulation. Auto switchover will occur if failure is in PCU #1. |                                                                             |

| 3.0 Shunt Regula-<br>tor Transistor<br>Stage (Internal) | 3.1 Internal shunt regulator transistor fails in the cut-off mode.                                         | 3, 1 Shunt transistor<br>Q8 fails open c <sub>e</sub> , or<br>drive circuit part<br>fails such that Q8<br>is biased off. | .00023582      | 3.1 PCU Regulation will be controlled via the External Shunt reg. transistor.                                                                                                                                                          | 1. 8                                                                                                                                                                                                                                 | 3.1 Automatic switch-<br>over will occur if<br>failure occurs in<br>PCU #1. |

|                                                         | 3.2 Internal Shunt regulator transistor fails in the "on" mode.                                            | 3. 2 Shunt transistor Q8 fails short ce, or drive circuit fails such that Q8 is biased on or into saturation.            | .00024812      | 3.3 The PCU will probably go out-of-regulation. In addition the shunt regulator will dissipate more power.                                                                                                                             | 3.3 If PCU goes out- of-regulation auto- matic switchover to PCU #2 will occur. If regulation is maintained but reserve power depleted, the Exp. ripple-off function will occur.                                                     |                                                                             |

| NO.     | REV. NO. |

|---------|----------|

| ATM-757 |          |

| PAGE 24 | of62     |

| DATE    |          |

|         |          |

categories of failure for the proportional controller break down as follows.

- Degredation of thermal control capability. The maximum utilization of the PCU reserve power cannot be effected so as to minimize the central station thermal swing. However, PCU regulation will be maintained, hence this failure category is not catastrophic in nature. This degraded mode of operation represents approximately 27% (Q1 .00070982) of the failure probability of the Regulator/proportional Controller.

- 2. Similar to the second failure classification of the differential control of the proportional controller fails in a manner such that power dissipation through either shunt regulator transistor is preclude the PCU will go out of regulation as the C/S temperature swings past the set-point level of of the failed shunt transistor. Refer to failure modes 21, 2.2 & 3.1 of table IV. This failure mode renders the PCU regulator inoperative effectively 50% of the time. The probability of this failure mode occuring is Q<sub>2</sub>.00070310 or approximately 28% of the Regulator/Proportional Controller total probability of failure.

- 3. If both shunt transistors are biased off simultaneously, the PCU regulator becomes inoperable. Refer to 2.3 of table IV. The probability of failure, Q<sub>3</sub> .00002093 or less than 1% of the Reg/Prop. Cont probability of failure.

- 4. The fourth failure category will cause the depletion of the available reserve power, thus causing the experiment ripple-off function to occur. This failure mode is similar to thd third category of failure documented for the Differential Controller. The probability of occurrance is Q4 .00049624 of 18% of the total Q for the regulator.

Failure categories 2 and 3, above represent potential single point potential failure sources to the system if no redundancy were to be employed. Consequently, implementation of this thermal control concept would necessitate the utilization of redundancy.

| NO.   |               | REV    | REV. NO. |   |

|-------|---------------|--------|----------|---|

| ATM   | <b>1-</b> 757 |        |          |   |

| PAGE. | 25            | _ OF . | 62       | _ |

| DATE  |               |        |          | _ |

#### 4.3 CONCEPT III

When the dynamic regulator was originally incorporated in the PCU design an effort was made to minimize the dissipation within that unit by physically mounting the resistor elements outside the temperature-controlled area. The power transistor and control electronics were left in the controlled environment for reliability reasons. To determine the impact of removing the remaining portion of reserve power dissipation from within the central station concept III was postulated. This concept required, in its simplest form, that the power transistor in each shunt regulator be removed from the temperature-controlled area (see Figure 4.3). In practice, two configurations were considered but, because of shortcomings that became evident in the preliminary analysis, the integration requirements of these configurations were not analyzed in detail. This section describes methods of implementing this concept and the resultant impact on the temperature control of the central station.

### 4.3.1 Description

The major constraints on implementing this concept are

- -selection of a suitable portion of the regulator circuit which could operate on the outside of the thermal barrier. The selected configurations must have minimum impact on both performance and mechanical design of the PCU and the central station.

- -thermal control of the externally-mounted regulator.

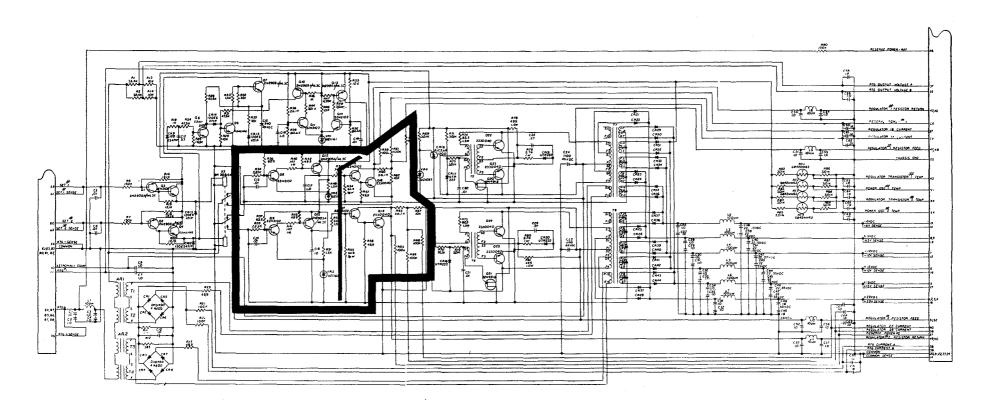

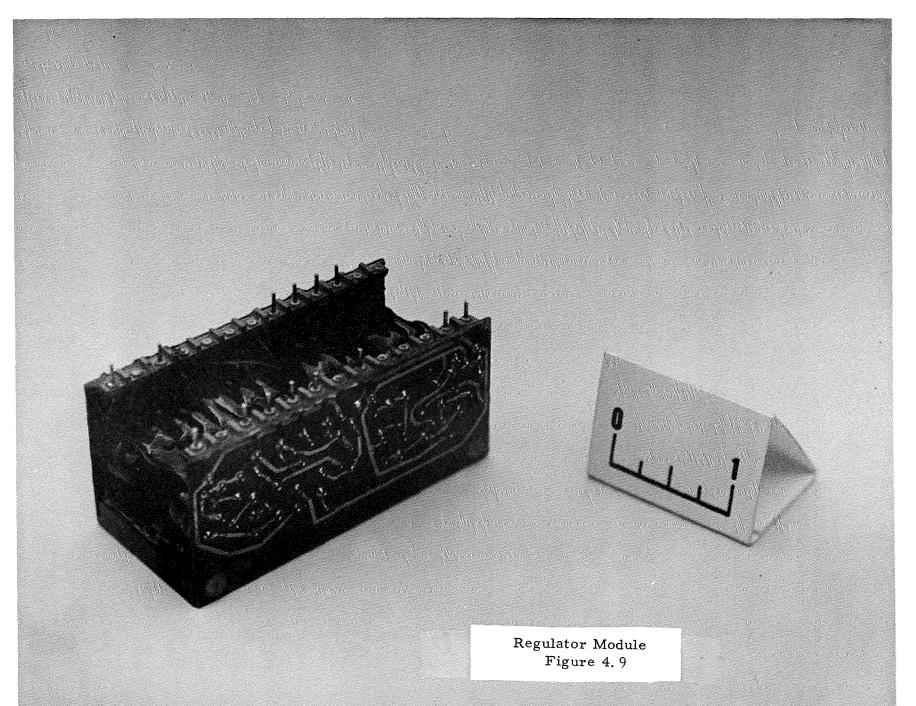

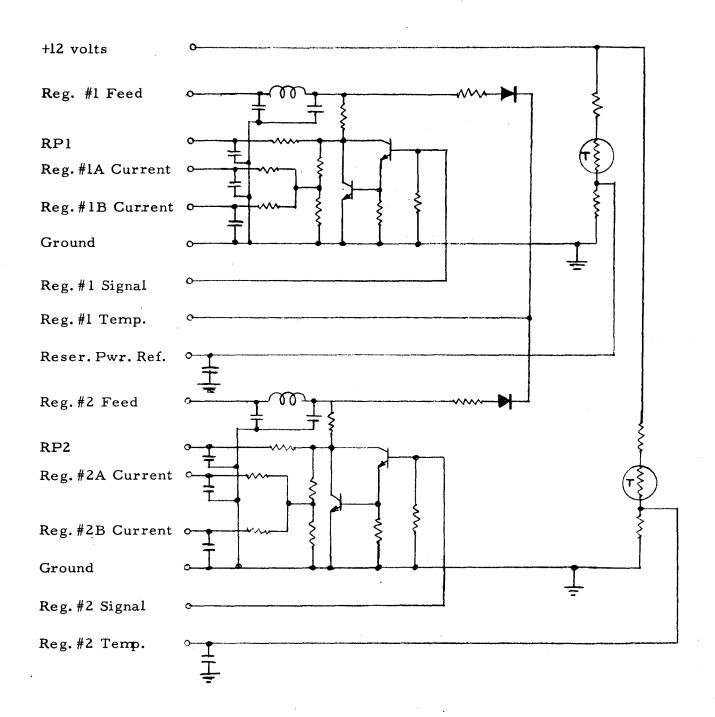

Figure 4.8 shows the complete circuit of the PCU. That portion of the circuit enclosed in the (solid) outline indicates the components packaged together in the regulator module (Figure 4.9). The portion of the regulator module which is outlined represents the smallest group of components which could be segregated from the main unit within the constraints listed above. Either the complete module package or this subgroup of components form a feasible configuration to implement this concept. Both approaches require the use of interconnecting wires which may carry a current of up to 3.5 amps with a 700 milliamp, 10 KHz ripple. Therefore, considerable caution must be exercised to prevent the electrical noise on these lines, which pass through the central station, from interfering with the operation of the central station electronics. Figure 4.10 shows the subgroup of components in an isolated form complete with interference filters.

Figure 4.8 PCU Circuit Diagram

REGULATOR ELECTRICAL INTERFACE Figure 4.10

| NO.    |      | REV | REV. NO. |  |

|--------|------|-----|----------|--|

| ATM    | -757 |     |          |  |

| PAGE . | 29   | OF_ | 62       |  |

| DATE   | 5/7  | /68 |          |  |

The thermally decoupled regulator concept requires redesign of the power conditioning unit. The extent of that redesign depends on which of two configurations are implemented. In Case No. 1, only the regulator transistors and associated circuits are moved to an isolated location. The redesign for this configuration consists of: -removing the transistors and resistors, -jumpering several points in the regulator module, and -adding a connector (or connectors) to accommodate four shielded cables. In addition to PCU redesign, the central station harness must be revised to accommodate wiring changes. Additionally a connector must be added to Sub Package I structure for the regulator interconnections with the PCU. It is estimated that there will be some loss of accuracy on the reserve power sensing for the "ripple-off" circuit due to the long leads and manganin wire required for interconnection.

In Case No. 2, the entire regulator circuit is thermally isolated from the central station. The PCU redesign for this configuration consists of: removing the regulator circuit, adding a connector (or connectors), and possibly changing the over-all package to eliminate unnecessary weight and volume resulting from the removal of the regulator circuit. The same changes to the central station harness and Sub Package I structure are required with this scheme as with the transistors only scheme.

The packaging of the externally-mounted regulator to ensure proper thermal control is described below. The size of this package, approximately 350 cubic inches, dictates a drastic redesign of the mounting provisions of at least one of the ALSEP subpackages to accommodate such a unit. It is proposed that the regulator package could be deployed on the lunar surface near pallet 1 or could remain on the sunshield in the manner of the dust detector. The only constraints on deployed location are that the package have a completely unobstructed view of space and that it be thermally isolated from the structure. Permitting it to remain on the structure has the obvious advantage of not requiring the astronaut to deploy it.

When evaluating the circuit reliability of this concept it is assumed that the electrical circuit is functionally unchanged, although physically redistributed. Since the temperature environment of the components would also be unchanged, it can be stated that the reliability is unchanged from that of the present design.

### 4.3.2 Packaging of the External Regulator

Unique to this concept is the necessity to provide a mounting for those electronic components outside of the central station electronics bay. A primary requirement of this new mounting is the maintenance of the temperature of the regulator elements within a range compatible with reliable operation for

| NO.    |     | REV      | REV. NO. |  |

|--------|-----|----------|----------|--|

| ATM-   | 757 | <u> </u> |          |  |

| PAGE _ | 30  | _ OF _   | 62       |  |

| DATE   | 5/  | 7/68     |          |  |

|        |     |          |          |  |

a 1-year mission. This range has been selected as -4°F to +185°F at the case of the power transistor during the ambient temperature conditions shown in Figure 2.1. Two designs are presented, either of which will meet this requirement over the full range of possible conditions of electrical dissipation within the components. One of these designs makes use of a heat pipe, the other uses thermal switches to control the heat flow out of the electronic units.

### 4.3.2.1 Heat Pipe Configuration

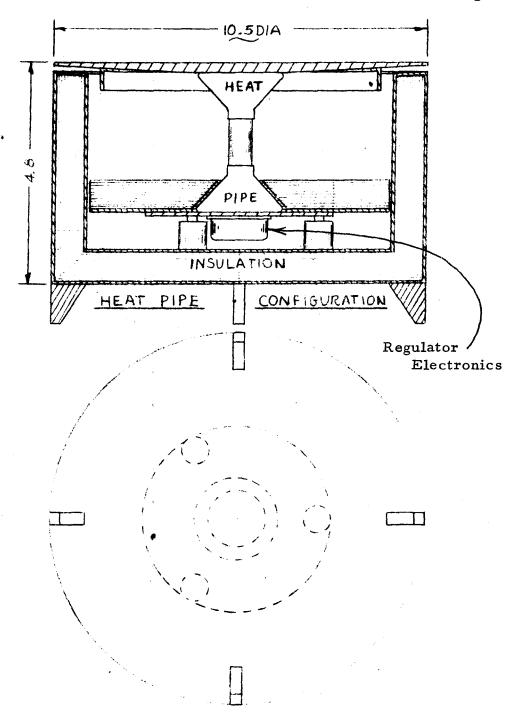

The thermal design of the heat pipe configuration is shown diagramatically in Figure 4.11. The regulator transistor is mounted on an isolated baseplate which is thermally coupled to the radiator by the heat pipe. The end of the heat pipe in direct contact with the radiator is the condensor end and the other, in contact with the baseplate, is the evaporator end.

The basic principle governing the operation of the heat pipe is vaporization of a liquid from a heat source and the condensation of the vapor and deposition of its latent heat of vaporization upon a heat sink. The entire process is one of mass transfer in which the vapor carries with it relatively large quantities of heat per unit mass. The vaporization and condensation occur under very small temperature differentials existing between the heat sink and heat source. Control of the process is inherent from the temperature-pressure laws governing the interaction between a pure liquid and its vapor.

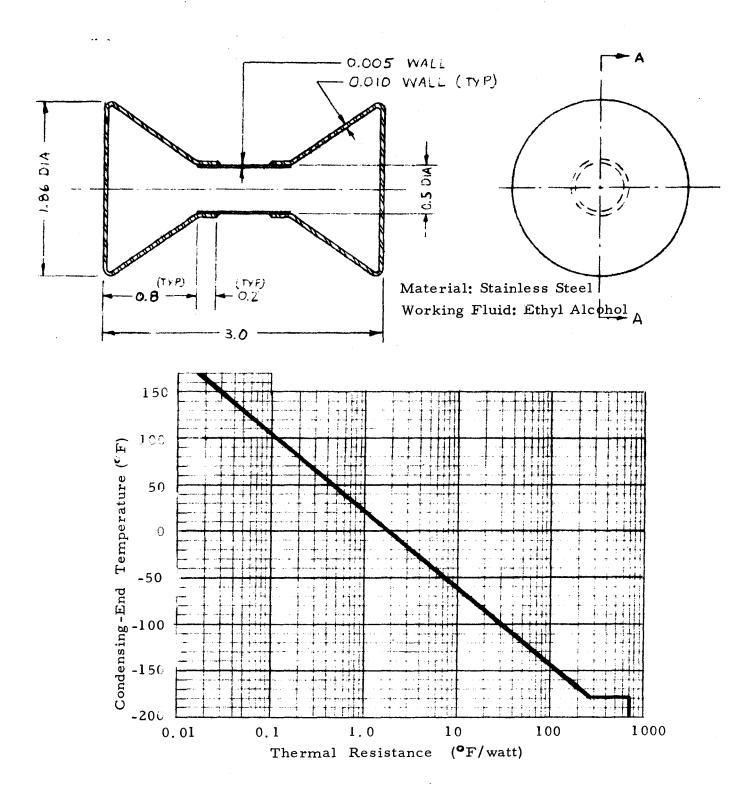

During the night, when the thermal dissipation is at a minimum, the radiator temperature drops to a very low value. The low radiator temperature increases the viscocity of the condensate which reduces its return rate, thereby increasing the thermal resistance of the heat pipe as shown in Figure 4.12. During this time, then, the transistor is thermally isolated from the lunar environment except for the heat leaks through the multilayer insulation, any structural penetrations required, and the heat pipe. Thus, in order to maintain the transistor at or above its minimum operating temperature during this period of minimum thermal dissipation the internal electrical dissipation must be equal to or greater than the total heat leak out of the package.

During the day the temperature of the lunar environment and the internal electrical dissipation both increase to their maximum values. This results in an increase in the radiator temperature. As the temperature of the radiator increases, the resistance of the heat pipe decreases, thus providing a compensating control over the extremely wide variations of lunar environmental temperatures.

Figure 4.11: THERMAL CONTROL--HEAT PIPE CONFIGURATION

Figure 4.12: HEAT PIPE, CONFIGURATION & PERFORMANCE

| <b>NO.</b><br>ATM-757 |     | REV. | REV. NO. |  |

|-----------------------|-----|------|----------|--|

| PAGE _                | 33  | _ OF | 62       |  |

| DATE                  | 5/7 | /68  |          |  |

A preliminary design for the heat pipe is shown in Figure 4.12. It consists of two flared ends joined by a very thin-walled tube of stainless steel. The purpose of the flared ends is to provide relatively large areas for heat transfer between the baseplate and the heat pipe and between the radiator and the heat pipe. The interconnecting tube is thin-walled in order to provide a high thermal resistance to heat conduction through the heat pipe structure. Since the heat pipe will be operated far below its capability 1, and in a 1/6 g environment the inside walls of the heat pipe may or may not be grooved to provide capillary channels for condensate return.

### 4.3.2.2 Thermal Switch Configuration

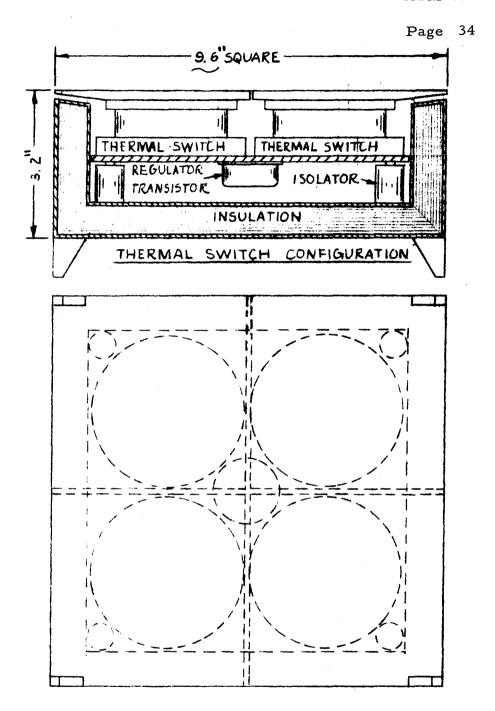

The thermal design of the thermal switch configuration is shown diagramatically in Figure 4.13. The design is essentially the same as the heat pipe configuration except that four thermal switch devices are required.

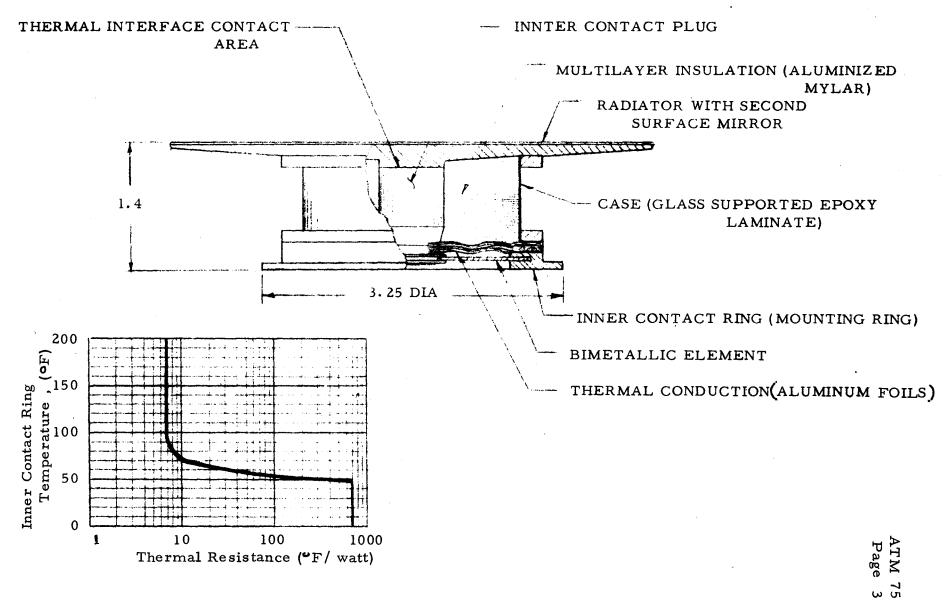

The thermal switch, shown in Figure 4.14 was developed by Hughes Aircraft Company for use on Surveyor. The switch design is held, under patent No. 3,177,933, by NASA. J. M. Bozajian of Hughes Aircraft is the inventor. The switch is capable of providing a resistance ratio of approximately 100 to 1 between the open condition and the fully closed condition, as shown in Figure 4.14. The contact surfaces, one being an integral part of the aluminum radiator substructure and the other a cylindrical aluminum plug, are forced together by four bimetallic elements which are attached to the base of the switch and engaged in a circumferential groove in the plug.

The plug contact surface is thinly coated with RTV-11 which in turn is charged with molybdenum disulfide (MoS<sub>2</sub>) powder. The contact surfaces are lapped flat to within one light band and exhibit a mirror finish prior to coating. The total coating thickness is less than  $3 \times 10^{-4}$  in. A cruciform bundle of thin aluminum foils provide a lateral thermal conduction tie between the inner contact ring (mounting ring) and the inner contact plug. Hence, the bimetal beams are free to move the inner contact in response to changes in the mounting ring temperature.

<sup>&</sup>lt;sup>1</sup>See The Heat Pipe by G. Yale Eastman in Scientific American Volume 218, No. 5, May 1968.

Figure 4.13: THERMAL CONTROL -- THERMAL SWITCH CONFIGURATION

Figure 4.14: HUGHES THERMAL SWITCH -- CONFIGURATION & PERFORMANCE

| NO.         |      | REV. | REV. NO. |  |  |  |  |  |  |

|-------------|------|------|----------|--|--|--|--|--|--|

| ATM.        | -757 |      |          |  |  |  |  |  |  |

| PAGE _      | 36   | . OF | 62       |  |  |  |  |  |  |

| DATE 5/7/68 |      |      |          |  |  |  |  |  |  |

The bimetal system provides a deflection rate of 0.001 in. for each 3°F temperature change and a buildup of pressure in the closed position of 1 lb/in² for each 5°F temperature increase. The closing point can be controlled by adjusting the position of the inner contact with respect to the bimetals by means of a threaded adjustment nut.

The switch attains its maximum thermal resistance very shortly after opening of the contacts if the ambient pressure within the switch is  $10^{-4}$  torr or less. The open resistance, approximately  $700^{\circ}\text{F/Watt}$  has been maximized by the following features:

- a. Utilization of the thinnest wall epoxy-glass laminated case consistent with the load carrying requirements imposed on it.

- b. Blockage of radiant interchange in the case body with multilayer aluminized mylar insulation.

- c. Sufficient venting to ensure that the pressure within the cask will not exceed 10<sup>-4</sup> torr.

As the mounting surface temperature rises above the switch closure temperature, the contact load increases linearly with the temperature and, in turn, the contact resistance decreases. Thus, as the demand for energy dissipation increases, the switch resistance decreases, providing a measure of self compensation for varying rates of internal electrical dissipation.

Problems have been encountered with sticking contacts after being assembled in the closed position for several months. The sticking is thought to be caused by a migration of the MoS<sub>2</sub> into the RTV-11 coating on the contact. The resulting condition, then, would be that of RTV-11 being exposed directly to the mating aluminum contact surface on the radiator without the intended MoS<sub>2</sub> interface material. Pressure exerted on the contacts over a long time interval could result in adhesion.

Due to the tight schedules imposed upon the now closed-out Surveyor program, a permanent solution to the problem has never been found.

| NO.<br>ATM- | 757 | REV. | NO. |  |  |  |  |  |

|-------------|-----|------|-----|--|--|--|--|--|

| PAGE _      | 37  | 0F _ | 62  |  |  |  |  |  |

| DATE 5/7/68 |     |      |     |  |  |  |  |  |

#### 4.3.3 Thermal Control Performance

#### 4.3.3.1 Externally-Mounted Regulator

Insulation: The high degree of thermal isolation required by the regulator makes it necessary to study in detail the insulation requirements and limitations. The multilayer insulation bag will be constructed of 1/4 mil mylar (60 layers/in.) with vapor deposited aluminum on both sides. Paper or nylon separators are included. The external layer of the bag will be protected from solar deterioration by the structure. Estimates have been made regarding the degrading effects of actual construction techniques (corners, bends, etc.) and penetrations through the bag. A bag with no penetrations or end effects has been estimated to have a thermal conductivity of 1.75 x  $10^{-5}$  (Btu/hr)/ftF (0.513 x  $10^{-5}$ w/ftF). The effect of the penetrations and construction techniques tend to increase this value and it is estimated that the theoretical value will be increased from 25 to 50 times. Thus, a carefully made bag using the best construction techniques is expected to possess a thermal conductivity of  $25 \times 0.513 \times 10^{-5} \text{w/ftF}$  or  $12.8 \times 10^{-5}$  w/ftF. However, it is expected that a less precise bag will exhibit a value up to  $25.7 \times 10^{-5} \text{w/ftF}$ .

As the degree of thermal isolation changes, the amount of heat available for thermal control also changes. The electrical dissipation of the regulator transistor varies from 4 to 17w. The heat leak has been estimated as a function of the insulation degrading factor ( $\beta$  = 25 and 50) and the number of layers (20, 40 and 60) of insulation. The heat leak is appropriately combined with the electrical dissipation in Table V to determine the total thermal dissipation of the package (qt). Examination of the data shows that the degrading factor can not be allowed to exceed 25. The effect that the thermal dissipation has on the size of the radiator is examined next.

Radiator: The selection of a radiator as to area and surface properties is discussed in this section. In the present application the requirement for maximum power dissipation during periods of direct sun load requires that the surface exhibit as low an  $\alpha/\epsilon$  ratio as possible. Second surface Vycor glass mirrors were selected since they afford a low  $\alpha/\epsilon$  ratio of 0.11/0.79 and possess good stability under ultraviolet solar load. The size of the radiator is a function of the properties of its thermal coating, the quantity of heat to be dissipated and the temperature at which

| NO.    |      | REV  | . NO. |

|--------|------|------|-------|

| ATM-   | -757 |      |       |

| PAGE _ | 38   | 0F _ | 62    |

| DATE   | 5/7  | /68  |       |

# TABLE V POWER DISSIPATED IN REGULATOR PACKAGE FOR REPRESENTATIVE CONDITIONS

Nighttime/Minimum Case

| Insulation             |           | /3 <b>=</b> 25 |           |           | /3 <b>=</b> 50 |           |  |  |  |  |

|------------------------|-----------|----------------|-----------|-----------|----------------|-----------|--|--|--|--|

| Dissipated In          | 20 Layers | 40 Layers      | 60 Layers | 20 Layers | 40 Layers      | 60 Layers |  |  |  |  |

| Transistor             | 4.0       | 4.0            | 4.0       | 4.0       | 4.0            | 4.0       |  |  |  |  |

| Heat Leak *            | -4.2      | -1.7           | -0.8      | -8.9      | -4.6           | 25        |  |  |  |  |

| Total Package          | -0.2      | + 2.3          | + 3.2     | -4.9      | -0.6           | +1.5      |  |  |  |  |

| Nighttime/Nominal Case |           |                |           |           |                |           |  |  |  |  |

| Transistor             | 9.0       | 9.0            | 9.0       | 9.0       | 9.0            | 9.0       |  |  |  |  |

| Heat Leak *            | -4.2      | -1.7           | -0.8      | -8.9      | -4.6           | -2.5      |  |  |  |  |

| Total Package          | + 4.8     | + 7.3          | + 8.2     | + 0.1     | + 4.4          | +6.5      |  |  |  |  |

| Daytime                |           |                |           |           |                |           |  |  |  |  |

| Transistor             | 17.0      | 17.0           | 17.0      | 17.0      | 17.0           | 17.0      |  |  |  |  |

| Heat Leak *            | + 0.6     | + 0.3          | +0.2      | +1.3      | + 0.6          | +0.4      |  |  |  |  |

| Total Package          | +17.6     | +17.3          | +17.2     | +18.3     | +17.6          | 17.4      |  |  |  |  |

<sup>\*</sup>Heat leak out is negative; heat leak in is positive

| NO. ATM | [ <b>-</b> 757 | REV. NO.     |   |

|---------|----------------|--------------|---|

| PAGE _  | 39             | of <u>62</u> | _ |

| DATE    | 5/             | 77/68        | _ |

the heat is to be rejected. As discussed above the quantity of heat to be rejected is a function of the internal thermal dissipation and the effectiveness of the insulation. The temperature at which the heat is to be rejected is a function of the operating temperature of the transistor, the quantity of heat to be rejected and the thermal resistance between the transistor case and the radiator surface.

Using the parameters for  $\beta$  = 25 as discussed above, the radiator size has been calculated for each of the thermal control configurations. These are 0.605 ft<sup>2</sup> (10.5 in. dia or 9.4 in. square) for the heat pipe configuration and 0.638 ft<sup>2</sup> (9.6 in. square) for the thermal switch configuration as shown in Figure 4.14.

Summary: The performance of each of the thermal control configurations plus a completely passive system have been calculated on the basis of worst case lunar surface operating conditions or lunar noon and predawn. At noon the lunar surface temperature is taken as 250°F and the solar load at 130 w/ft². At predawn, the lunar surface temperature is assumed to be -300°F and the solar load is zero. The thermal control system performance summary is presented in Table VI and Figure 4.15.

#### 4.3.3.2 Central Station Thermal Control

Mounting the regulator transistor externally to the Central Station, changes the operational temperature range of the radiator to the extent that a new mask size must be determined. On the other hand, it is also possible to consider a completely different thermal control system - namely - DRT. The following is a discussion of the central station electronics temperatures for both techniques under conditions imposed by concept III.

The electrical power dissipation within the electronics bay is essentially constant, varying between 24.5 watts at night to 26.0 watts during daytime. This change in dissipation requires a change in the unmasked area of the radiator surface. The computed results are shown in Table VII for three sizes of radiator mask.

TABLE VII SUNSHIELD CONFIGURATION THERMAL PERFORMANCE

| RADIATOR TEMPERATURES IN <sup>O</sup> F |      |       |     |         |       |             |      |       |  |  |  |

|-----------------------------------------|------|-------|-----|---------|-------|-------------|------|-------|--|--|--|

| 8'' Ma                                  | ask  |       | 8   | 1/4" Ma | ask   | 8 1/2" Mask |      |       |  |  |  |

| Day                                     | Nite | Swing | Day | Nite    | Swing | Day         | Nite | Swing |  |  |  |

| 122                                     | -24  | 146   | 127 | -16     | 143   | 134         | -8   | 142   |  |  |  |

Bendix Aerospace

Systems Division

Thermal Support of ALSEP Central Station Using Reserve Power

NO. ATM-757

REV.NO.

PAGE \_\_\_\_\_\_\_ OF \_\_\_\_\_\_\_62\_\_

### TABLE VI PCU REGULATOR PACKAGE THERMAL PERFORMANCE SUMMARY

| Perfor-                        |      |     |      |      |             |             | THERMAL CONTROL SYSTEM CONFIGURATION |      |      |      |  |     |      |      |             |     |     |      |      |      |        |      |      |     |     |      |       |      |      |

|--------------------------------|------|-----|------|------|-------------|-------------|--------------------------------------|------|------|------|--|-----|------|------|-------------|-----|-----|------|------|------|--------|------|------|-----|-----|------|-------|------|------|

| mance                          | ion  | CC  | MP   | LE   | rel         | ΥF          | AS                                   | SIVI | Ξ    |      |  |     | I    | ΙEΑ  | T F         | IPI | Ē   |      |      |      |        | THI  | ERN  | MAI | SW  | ITC  | CH    |      |      |

| Parameter                      | ulat | Nit | e/N  | lin. | Nit         | te/N        | lom                                  | . Da | ytir | ne   |  | Nit | e/N  | lin. | Nit         | e/N | om. | Da   | ytir | ne   | Nit    | e/M  | lin. | Nit | e/N | om.  | Da    | ytir | ne   |

|                                | Ins  | 20  | 40   | 60   | 20          | 40          | 60                                   | 20   | 40   | 60   |  | 20  | 40   | 60   | 20          | 40  | 60  | 20   | 40   | 60   | <br>20 | 40   | 60   | 20  | 40  | 60   | 20    | 40   | 60   |

| Trans Dis                      | ss.  | 4.0 | 4.0  | 4.0  | 9.0         | 9.0         | 9.0                                  | 17.0 | 17.0 | 17.0 |  | 4.0 | 4.0  | 4.0  | 9.0         | 9.0 | 9.0 | 17.0 | 17.0 | 17.0 | 4.0    | 4.0  | 4.0  | 9.0 | 9.0 | 9.0  | 17.0  | 17.0 | 17.0 |

| Total Rad                      |      | -   | 2.3  | 3.2  | 4.8         | 7.3         | 8.2                                  | 17.6 | 17.3 | 17.2 |  | -   | 2.3  | 3.2  | 4.8         | 7.3 | 8.2 | 17.6 | 17.3 | 17.2 | -      | 2.3  | 3.2  | 4.8 | 7.3 | 8.2  | 1 7.6 | 17.3 | 17.  |

| Rad. Ten                       |      | -   | -135 | -107 | <b>-</b> 69 | <b>-2</b> 6 | -12                                  | 121  | 1 19 | 1 19 |  | -   | -147 | -120 | <b>-</b> 84 | 43  | -30 | 1 05 | 103  | 103  | -      | -151 | -125 | -89 | -48 | -36  | 100   | 98   | 97   |

| Switch Re                      | es.  | -   | 0    | 0    | 0           | 0           | 0                                    | 0    | 0    | 0    |  | -   | 99   | 50   | 20          | 6.4 | 4.5 | 0.11 | 0.12 | 0.12 | -      | 84   | 53   | 28  | 133 | 10.4 | 1.7   | 1.7  | 1.7  |

| ∆T, Rad. t<br>Baseplate (      |      | -   | 0    | 0    | 0           | 0           | 0                                    | 0    | 0    | 0    |  | -   | 22.7 | 160  | 95          | 47  | 37  | 1.9  | 2.0  | 2.0  | -      | 193  | 169  | 135 | 97  | 85   | 30    | 29   | 29   |

| $\Delta$ T, Baser<br>to Trans. |      | -   | 5    | 7    | 11          | 17          | 19                                   | 40   | 39   | 39   |  | -   | 5    | 7    | 11          | 17  | 19  | 40   | 39   | 39   | -      | 5    | 7    | 11  | 17  | 19   | 40    | 39   | 39   |

| Trans. Ter<br>(F)              | mp.  | -   | -130 | -100 | <b>-</b> 58 | <b>-</b> 9  | 7                                    | 161  | 158  | 158  |  | -   | 85   | 47   | 22          | 21  | 26  | 147  | 144  | 144  | -      | 47   | 51   | 57  | 66  | 68   | 170   | 166  | 165  |