| endix                      | ALSEP Array E - Command Decoder<br>Failure Modes, Effects &<br>Criticality Analysis | ATM 949     |

|----------------------------|-------------------------------------------------------------------------------------|-------------|

| erospace<br>stems Division |                                                                                     | DATE 6-1-71 |

This ATM documents the Failure Modes, Effects and Criticality Analysis on the Bendix designed Command Decoder for the Array E ALSEP System. The analysis reflects analysis on those parts which are presently planned to be used in final flight configuration.

This document is prepared in accordance with the requirements of Section 5.2 of the Reliability Program Plan for Array E, ALSEP-RA-08, Bendix document number BSR 3024 dated 11-30-70.

Reliability prediction data are also documented herein in accordance with Section 5.5 of the Array E Reliability Program Plan.

Prepared by M. Tanacoan)

M. Papaioan ALSEP Reliability Department

Approved by

S.J. Ellison, Manager ALSEP Reliability

| Aerospace<br>Systems Division |                                                                               | PAGE    |  |

|-------------------------------|-------------------------------------------------------------------------------|---------|--|

| Bendix                        | ALSEP E Command Decoder<br>Failure Modes, Effects and<br>Criticality Analysis | ATM 949 |  |

#### 1.0 Introduction

The results of the Reliability Prediction and the Failure Mode, Effects, and Criticality Analysis for ALSEP E Command Decoder are documented in this report. This Command Decoder represents the Bendix Designed unit which makes extensive use of low power TTL integrated circuits.

The reliability prediction for the Command Decoder is .99928 which exceeds the specified goal of .99000.

### 2.0 Circuit Description

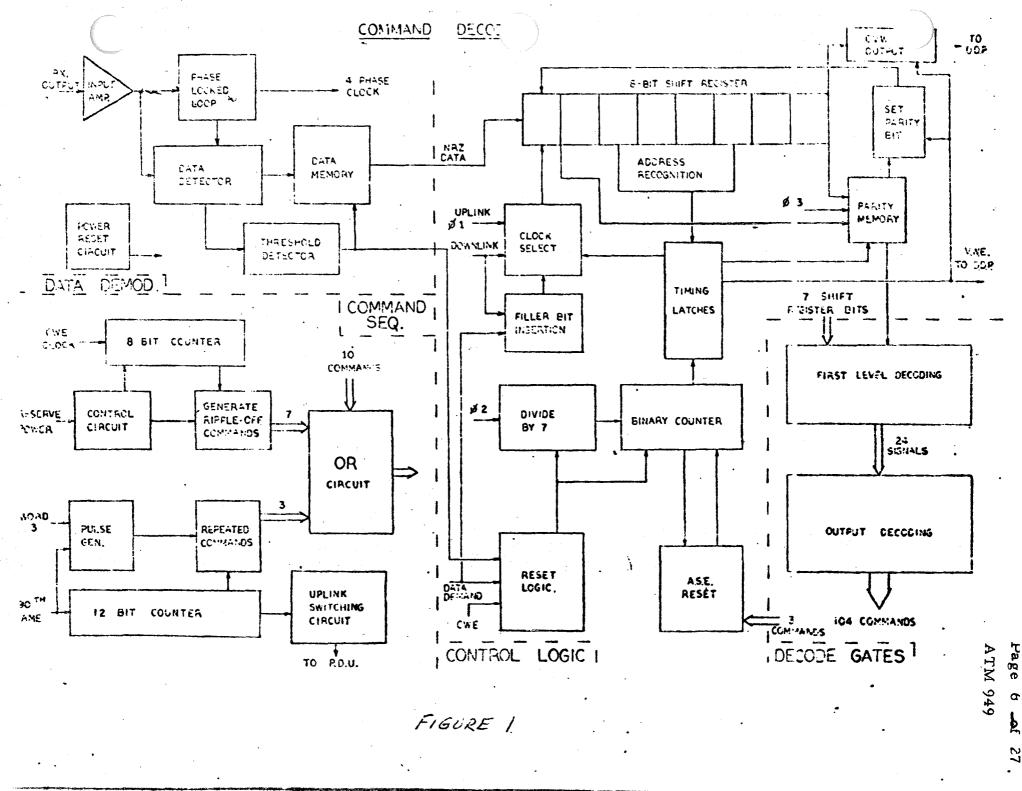

Figure 1 shows the block diagram of one side of the redundant portion of the Command Decoder, and also of the non-redundant (back-up) functions on the Command Sequencer board. This diagram is included to clarify the terms and descriptions given in the Failure Mode, Effects, and Criticality Analysis portion of this ATM (Table II).

The logical flow of a ground command is from the receiver to the Data Demodulator, where it is converted into digital form and passed to the Control Logic and then to the Decode Gate board. The form of this data is three seven bit words, the first being the ALSEP address, the second the command complement for parity checking purposes, and the third word is the command. The Command Sequencer board provides the back-up functions of generating the repeated commands, the uplink switch-over circuit, and the ripple-off circuit.

#### 2.1 Data Demodulator

The Data Demodulator circuit converts biphase baseband data from the Command Receiver into "Non Return to Zero" (NRZ) digital data and also provides uplink clock and threshold signals for the control logic portion of the Command Decoder. The unit is designed to accept a composite waveform which is the sum of a 1 KHz clock and a 2 KHz data subcarrier. The 2 KHz subcarrier is phase modulated by a 1000 bit/second data stream. The Phase Lock Loop (PLL) section provides the signals both to detect the data and clock it out to the Command Register in the Control Logic Section by locking to the 1 KHz uplink clock generated at the ground station. The phase lock loop contains circuitry which generates 4 phases of a 1 KHz square wave. One

| Bendix           | ALSEP E Command Decoder<br>Failure Modes, Effects and | ATM 949     |

|------------------|-------------------------------------------------------|-------------|

| Aerospace        | Criticality Analysis                                  | PAGE OF     |

| Systems Division |                                                       | DATE 6-1-71 |

phase is used to drive the VCO to the phase lock condition while the other phases of the 1 KHz clock are gated together to produce the control logic clocks and provide 2 KHz signals for the data detector. The data detector consists of two detection chains, one to detect "1" bits and the other to detect "0" bits. The outputs of the two detection chains are connected to give a logic "1" output when a valid bit one is detected in the "1" chain and when a good bit zero is detected in the "0" chain. The outputs are clocked into the data flip flop by a short pulse generated near the end of each bit. Thus, NRZ data is obtained from the data flip flop, delayed by one bit from the baseband data. The threshold circuits are in two sections. Firstly, the analog threshold, described above, which ensures that output of the integrate and dump circuit is large enough before the comparators can produce data. Secondly, the digital threshold circuit which ensures that at least four valid data bits must be produced before the NRZ data is allowed into the Command Register in the Control Logic. The gate output of this circuitry is the digital threshold signal, and it is used to inhibit the data flip flop and also to reset the control logic, should a data dropout occur.

## 2.2 Control Logic

The Control Logic consists of an eight bit shift register, two counters, and reset circuitry. The shift register (Command Register) has the NRZ data passing through it at the rate of 1 KHz. A gate constantly samples the first seven bits of the shift register for the address of the particular ALSEP. Once an address is recognized, a timing sequence is initiated. After address recognition, the next seven pulses shift the command complement into the last seven bits of the shift register. The binary counter, ensures that the next seven bits of data (the command) clocked in are checked for parity. An exclusive OR gate sensing the first and last bits of the shift register performs a parity check on each bit of the command complement and the corresponding bit of the command. The command sequence pulse is gated with the parity flip flop to produce a command execute pulse. After command has been executed, a logical signal VWEZP is sent to the Data Processor and causes a data demand signal DDIZP to be sent back to the command decoder.

## 2.3 Decode Gates

The decode gate matrix decodes a seven bit binary command into individual command lines. A command execute pulse, CEXAN, is used Bendix ospace .tems Division

ALSEP E Command Decoder Failure Modes, Effects and Criticality Analysis

| 1 10 | ٥.    |     | REV   | . NO. |   |

|------|-------|-----|-------|-------|---|

| А    | ТM    | 949 |       |       |   |

| P    | AGE _ | 4   | . OF. | 27    | - |

| 0,   | ATE   | 6-1 | -71   |       |   |

to create the correct command pulse length. The decoding takes place in two levels. The first level creates outputs from all combinations of the first four bits (16) and from all combinations of the remaining three bits (8). This is accomplished with four-input gates, with the fourth input of the group of eight used for the command execute pulse. The output decoding is carried out with two input gates, all having inputs associated with each of the two groups of first level gates. One hundred and four commands of a possible 128 are decoded, with resistors provided in 53 outputs for rise time control. The capacitors for this control are provided on the Control Logic board.

## 2.4 Command Sequencer

The Command Sequencer consists of a free running binary counter with decoding logic wired to Experiment Calibrate command lines. The sequencer also functions as an uplink switch-over timer to ensure a switch from one uplink chain to the other in case of an uplink failure. The clock for the counter is the 90th frame mark, NFIZP, a 118 us pulse appearing every 54 seconds, generated within the Data Processor. Once the commands are generated, they are "OR'd" with the experiment calibrate command lines in the redundant section of the command sequencer. Also, within this redundant section is an "enable/inhibit repeated commands" flip flop which, by means of two commands, lets the ground user of ALSEP decide whether the repeated calibrate commands should be provided to the experiments or not. This inhibit feature also permits the repeated command sequencer to be disabled in case of a failure in any of the non-redundant circuitry. The Ripple-off circuit consists of an 8-bit binary counter and decoding gates producing the commands. The counter is clocked by the CWE clock, a 1060 Hz clock generated within the Data Processor. The loss of a "Reserve Power" signal from the PCU causes seven power loads to be switched sequentially to standby after a predetermined length of time.

#### 3.0 Reliability Prediction

The reliability prediction for the Command Decoder operating in standby redundant configuration is calculated to be .99928 for launch, deployment and two years of lunar operation. The predicted reliability exceeds the specified goal of .99000 as stated in ATM 889, Section 4.2.

| Bendix 4       | ALSEP E Command Decoder                            | ATM 949     |  |  |

|----------------|----------------------------------------------------|-------------|--|--|

|                | Failure Modes, Effects and<br>Criticality Analysis | PAGE OF     |  |  |

| Stems Division | v                                                  | PATE 6-1-71 |  |  |

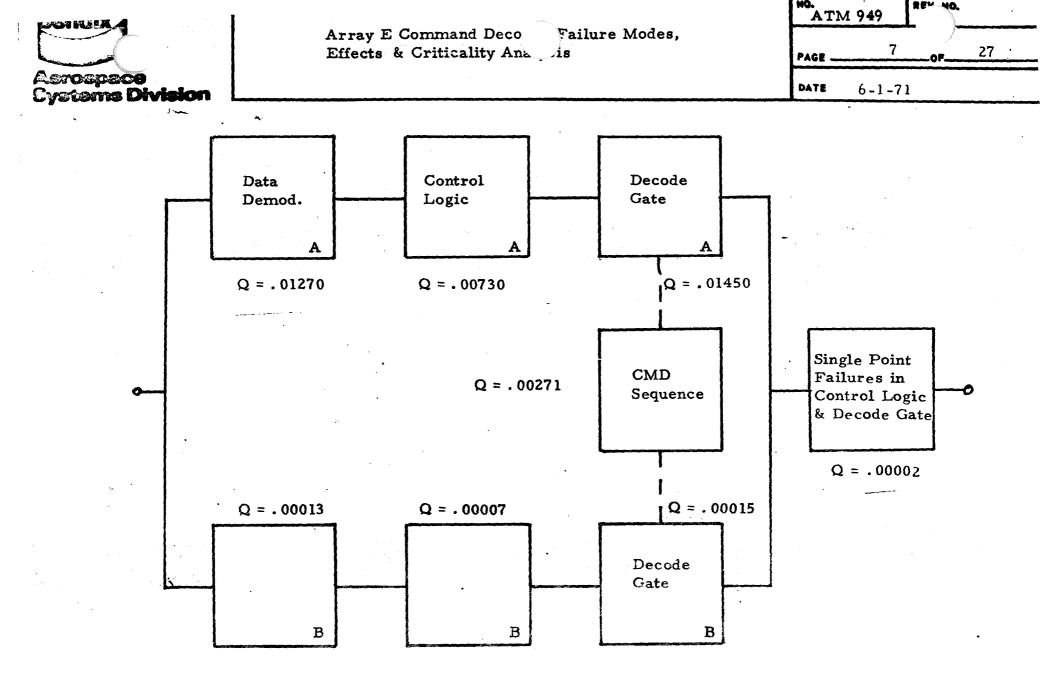

Figure 2 defines the Reliability Block Diagram and Mathematical Model for the Command Decoder. Two identical channels are represented by "A" in operation, and "B" in standby redundancy. The components associated with switching and located on the only non-redundant module represent the third reliability function. The fourth block represents the single point failures in the Control Logic and Decode Gate Modules.

The probability failures for each functional component identified in Figure 2 are tabulated in Table I. The probability failures shown represent composite totals derived from the parts application stress ratios of each electronic piece part modified by the failure mode apportionment.

Figure 2 Command Decoder Reliability Block Diagram

and the second s

Bendix

## Aerospace vistems Division

Ì.

| NO.      | REV. NO. |

|----------|----------|

| ATM 949  |          |

| PAGE8    | OF       |

| DATE 6-1 | 1-71     |

# TABLE I

ALSEP E Command Decoder Failure Modes, Effects and

Criticality Analysis

## PROBABILITY FAILURE SUMMARY

| Assembly              | Operating              | Standby                      |

|-----------------------|------------------------|------------------------------|

| Data Demodulator A*   | .01270                 | . 00013                      |

| Control Logic A       | .00730                 | . 00007                      |

| Control Logic SPFS    | .00001                 |                              |

| Decode Gates A        | .01450                 | . 00015                      |

| Decode Gates SPFS     | .00001                 |                              |

| Totals                | Q <sub>1</sub> =.03450 | <b>Q<sub>2</sub>=.0</b> 0035 |

| Sequencer (Switching) | $Q_{g} = .00271$       |                              |

2

\*B Boards have same failure rates as A Boards.

| Bendix 1         | ALSEP E Command Decoder<br>Reliability and Failure Mode, Effects | ATM 949      |

|------------------|------------------------------------------------------------------|--------------|

| Aerospace        | and Critical Analysis                                            | PAGE 9 OF 27 |

| Systems Division |                                                                  | DATE 6-1-71  |

3.1

**Reliability** Calculations

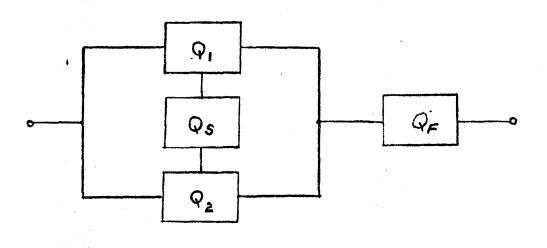

Figure 2 RELIABILITY MODEL

3.1.1

$Q_{1} = Probability Failure in Operation$   $Q_{2} = Probability Failure in Standby$   $Q_{S} = Probability Failure in Switching$   $Q_{F} = Probability Failure in Single Point Failures$   $Q_{T} = \frac{Q_{1} \cdot Q_{1}}{2} + \frac{Q_{1} \cdot Q_{2}}{2} + Q_{1} R_{2} Q_{S} + Q_{F}$   $Q_{T} = \frac{Q_{1}^{2}}{2} + \frac{Q_{1} \cdot Q_{2}}{2} + Q_{1} R_{2} Q_{S} + Q_{F}$

3.1.2

Ż

$$R_{T} = 1 - Q_{T}$$

$$R_{T} = 1 - Q_{1}^{2} - Q_{1} \cdot Q_{2} - Q_{1} R_{2} Q_{5} - Q_{F}$$

Reliability Equation for Command Decoder

| <b>Bendix</b>          | ALSEP E Command Decoder                                                                                            | NO. RE<br>ATM 949 |                                       | E V. NO. |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------|----------|--|

| Aerospace              | Failure Modes, Effects and<br>Criticality Analysis                                                                 |                   | 0 01                                  | 27       |  |

| Systems Division       |                                                                                                                    | DATE 6-1-71       |                                       | 1        |  |

| 3.1.3 Q <sub>2</sub> = | $1 - R_2$                                                                                                          |                   |                                       |          |  |

| R <sub>2</sub> =       | 1 - Q <sub>2</sub>                                                                                                 |                   |                                       |          |  |

| R <sub>2</sub> =       | 100035                                                                                                             |                   |                                       |          |  |

| R <sub>2</sub> =       | . 99965                                                                                                            |                   |                                       |          |  |

| Q <sub>1</sub> =       | .03450                                                                                                             |                   |                                       |          |  |

| Q <sub>2</sub> =       | . 00035                                                                                                            |                   |                                       |          |  |

| Q <sub>S</sub> =       | .00271                                                                                                             |                   |                                       |          |  |

| Q <sub>F</sub> =       | .00002                                                                                                             |                   |                                       |          |  |

| Q <sub>T</sub> =       | $\frac{\left(\frac{Q_{1}}{2}\right)^{2}}{2} + \frac{Q_{1} \cdot Q_{2}}{2} + Q_{1} \cdot R_{2} \cdot Q_{S} + Q_{F}$ | .,                | • • • • • • • • • • • • • • • • • • • |          |  |

| Q <sub>T</sub> =       | $\frac{(.03450)^2}{2} + \frac{(:03450)(.00035)}{2} + (.03450)(.9996)$                                              | 65) (.00)         | 271)+                                 | .00002   |  |

| Q <sub>T</sub> =       | .00060 + .00001 + .00009 + .00002                                                                                  |                   |                                       | ·        |  |

| Q <sub>T</sub> =       | .00072                                                                                                             |                   |                                       |          |  |

| 3.1.4 R_ =             | 1 - Q_                                                                                                             |                   |                                       |          |  |

.4  $R_T = 1 - Q_T$  $R_T = 1 - .00072$  $R_T = .99928$

**lerospace**

Systems Division

ALSEP-E Command Decoder Failure Modes, Effects and Criticality Analysis

| АТМ    |     |      |    |

|--------|-----|------|----|

| PAGE . | 11  | OF _ | 27 |

| DATE   | 6-1 | -71  |    |

## 4.0 FAILURE MODES, EFFECTS AND CRITICALITY ANALYSIS

The failure mode and effects analysis for the Command Decoder are documented in Table II. The failure probabilities reflect the identified line item. The criticality column lists in descending order the criticality as applied to the ALSEP system failure modes. This column will provide criticality rankings in accordance with BSR 3024, Section 5.2.2. The criteria for criticality rankings is listed in 4.1.

The format of Table II is designed to provide the reader with a narrative description of the varying types of failures that could occur, combined with the resultant performance characteristics. This information is useful to system support in performing fault isolation should any anomally occur.

There are two ALSEP-E single point failures within the Command Decoder itself. They are the two single lines between the Data Processor and Command Decoder. The CL0011ZN signal is a single point failure which will result in loss of all data except for LSPE, while the EXFZN signal will cause the system to go into the ASE Data Mode and remain there. The circuitry required to eliminate the two single point failures is extremely complex and reliability trade-off studies have shown that the increased complexity makes the circuitry less reliable.

The failure probability figures were derived using the data contained in ATM-954, the Command Decoder Parts Application Analysis. ATM 605A was used to derive the component  $\alpha$ 's (open, short, drift, etc. apportionments). Some failure modes, such as drift of a resistor in a digital circuit, do not affect the operation. The failure modes which do not affect the operation are not included in the FMECA. For this reason, the sum of  $\alpha$ 's for some circuit/function items do not always equal one. However, all Command Decoder piece-part failure modes which do not affect the operation of the Command Decoder or any other unit in ALSEP are included in the FMECA (Table II).

| B | er | d | i)  | 1 |

|---|----|---|-----|---|

|   |    |   |     |   |

|   |    |   | 2.0 |   |

ALSEP E Command Decoder Failure Modes, Effects and Criticality Analysis

| ATM  | 949   |     |    |  |

|------|-------|-----|----|--|

|      | 12    | OF. | 27 |  |

| DATE | 6-1-7 | 1   |    |  |

4.1 The criticality code to be used in the criticality column of Table II is listed below according to the following criteria:

I Loss of system

II Loss of system control

III Loss of one experiment

IV Loss of housekeeping channel(s)

V Loss of redundant element

VI Degradation of a redundant element

5.0 Reliability Assessment

The purpose of performing a reliability prediction and failure modes analysis is to identify inherent design weaknesses. From the results of these analyses it has been concluded the reliability and design objectives have been fully satisfied.

|     |                                             | • <b>*</b> | •           | ,              |      | •                                                                                                             |       | SYSTEM ALSEP PREPARED<br>DO THEM<br>DO THEM Decoder DWG NO.                                             | BY<br>paioan | NO.477<br>949 | PEV.           |

|-----|---------------------------------------------|------------|-------------|----------------|------|---------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------|--------------|---------------|----------------|

|     |                                             | FAILURE N  | NODE, EF    | FECT & CRI     | TICA | LITY ANALYSIS                                                                                                 |       | ASSY Decode Gates DWS NO 2                                                                              | 367626       | PAGE 13       | of 27<br>-1-71 |

| P   | ART/COMPONENT                               |            | AILURE MODE |                |      | EFFECT OI                                                                                                     | FAILU |                                                                                                         | FAt          |               | CRITIC-        |

|     | SYMBOL                                      |            | AILURE MOUL | (α)            |      | ASSEMBLY                                                                                                      |       | END ITEM                                                                                                | Q x          | 105           | ALITY          |

| 1.0 | Input Buffer<br>and Inverter:<br>UIA, UIB   | 1.1 UIA,   | UIB, Fail   | Low . 70       | 1.1  | U1A will act as an enable signal<br>to 4-input nand gates, U3B, U4B,<br>U5B, U6B, U7B, U8B, U9B, and<br>U10B. |       | Failure of UIA will permit one (1)<br>possible wrong command to be<br>executed when commanded.          | 1.1          | 7.36          | VI             |

|     |                                             |            |             |                | -    | U1B will act as an inhibit signal<br>to 4-input nand gates.                                                   |       | When U1B fails, fifty-three (53)<br>commands will be inoperative and<br>not capable of being executed.  |              |               |                |

|     |                                             | 1.2 U1A,   | Ulb Fai     | High . 30      | 1.2  | U1A will act as an inhibit signal<br>to 4-input nand gates                                                    |       | When UIA fails, fifty-three (53)<br>commands will be inoperative and<br>not capable of being executed.  | 1.2          | 3. 15         | v              |

|     |                                             |            |             | ·              |      | U1B will act as an enable signal to 4-input nand gates.                                                       | 1     | Failure of UIB will permit one (1)<br>possible wrong command to be<br>executed when commanded.          |              | _             |                |

| 2.0 | Input Buffer:<br>UIC                        | 2.1 UIC    | Fai         | Low . 70       | 2.1  | Acts as an inhibit signal to 4-input<br>nand gates, U3A, U4A, U5A, U6A,<br>U7A, U8A, U9A, and U10A.           | 2.1   | Fifty-one (51) commands will be<br>inoperative and not capable of<br>being executed.                    | 2.1          | 3.68          | 1              |

|     |                                             | 2.2 UIC    | Fai         | l High. 30     | 2.2  | Acts as an enable signal to 4-input nand gates.                                                               | ſ     | One (1) possible wrong command will be executed when commanded                                          | 2.2          | 1.58<br>7     | VI             |

| 3.0 | Input Buffer<br>and Inverter: .<br>UID, UIE | 3.1 UID,   | UIE Fai     | 1 Low . 70     | 3, 1 | UID will act as an enable signal<br>to 4-input nand gates. U7A, U7B,<br>U8A, U8B, U9A, U9B, U10A,<br>U10B.    |       | Failure of UID will permit one (1<br>possible wrong command to be<br>executed when commanded            | 3.1          | 7.36          | 'VI            |

|     | •<br>•<br>•                                 |            | -<br>-      | •              | •    | U1E will act as an inhibit signal<br>to 4-input nand gates.                                                   |       | When UlE fails, fifty-one (51)<br>commands will be inoperative and<br>not capable of being executed.    |              |               |                |

|     |                                             | 3.2 UID,   | UlE Fai     | 1 High . 30    | 3.2  | UID will act as an inhibit signal to<br>4-input nand gates.                                                   |       | When UID fails, fifty-one (51)<br>commands will be inoperative and<br>not be capable of being executed. | 3.2          | 3.15          | <b>v</b> .     |

|     |                                             |            |             | . <sup>1</sup> |      | UlE will act as an enable signal<br>to 4-input nand gates.                                                    |       | Failure of U1E will permit one (1 possible wrong command to be executed when commanded.                 | 1            | -             |                |

|     |                                             |            |             |                |      |                                                                                                               |       |                                                                                                         |              |               |                |

|     |                                             |            |             |                |      |                                                                                                               |       |                                                                                                         |              |               |                |

. . .

|                                               |              |          |                 |       |                                                                                                               |        | SYSTEM<br>ALSEP<br>END ITEM                                                         | PREPARED B |                    | NO. AT M<br>949<br>PAGE 14 | of 27   |

|-----------------------------------------------|--------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------|------------|--------------------|----------------------------|---------|

| <u></u>                                       | FAILURE MC   | DE, EFFI | ECT & CRI       | TICA  | LITY ANALYSIS                                                                                                 |        | ASS'Y Decode Gates                                                                  | DWG NO 236 | 7626               |                            | -1-71   |

| PART/COMPONENT<br>SYMBOL                      | FAIL         | URE MODE | 4.0.3           |       | EFFECT O                                                                                                      | F FAIL |                                                                                     |            | PROBA              | URE<br>BILITY              | CRITIC- |

| 4.0 Input Buffer:<br>UIF                      | 4.1 UIF      | Fail     | (œ)<br>Low . 70 | 4. 1. | ASSEMBLY<br>Acts as an inhibit signal to 4-input<br>nand gates, U3A, U3B, U4A, U4B,<br>U5A, U5B, U6A and U6B. | 4.1    | END (TEM<br>Fifty-one (51) commands<br>inoperative and not capab<br>being executed. |            | <u>Q x</u><br>4. 1 | <u>10</u> 3. r.8           | v       |

|                                               | 4.2 U1F      | Fail     | High . 30       | 4.2   | Acts as an enable signal to 4-input nand gates.                                                               | 4.2    | One (1) possible wrong co<br>will be executed when co                               | 1          | 4.2                | 1.58                       | Ņ       |

| 5.0 Input Buffer<br>And Inverter:<br>U2A, U2B | 5.1 U2A, U21 | B Fail   | Low .70         | 5.1   | U2A will act as an enable signal to<br>4-input nand gates, U4A, U4B<br>U6A, U6B, U8A, U8B, U10A, and<br>U10B. | 5.1    | Failure of U2A will perm<br>possible wrong command<br>executed when commande        | l to be    | 5.1                | 7.36                       | VI      |

|                                               |              |          |                 |       | U2A will act as an inhibit signal<br>to 4-input nand gates.                                                   |        | When U2B fails, fifty-for<br>commands will be inoper<br>not capable of being exec   | ative and  |                    |                            |         |

|                                               | 5.2 U2A, U2  | B Fail   | High . 30       | 5.2   | U2A will act as an inhibit signal to<br>4-input nand gates.                                                   | 5.2    | When U2A fails, fifty-for<br>commands will be inoper<br>not capable of being exec   | rative and | 5.2                | 3. 15                      | v       |

|                                               |              |          |                 |       | U2B will act as an enable signal to<br>4-input nand gates.                                                    |        | Failures of U2B will per<br>(1) possible wrong comm<br>executed when command        | hand to be |                    |                            |         |

| 6.0 Input Buffer:<br>U2C                      | 6.1 U2C      | Fail     | Low .70         | 6.1   | Acts as an inhibit signal to 4-input<br>nand gates, U3A, U3B, U5A,<br>U%B, U7A, U7B, U9A and U9B.             | 6.1    | Sixty (60) commands will<br>inoperative and not capal<br>executed.                  |            | 6.1                | 3. 68                      | v       |

|                                               | 6.2 U2C      | Fail     | High . 30       | 6.2   | Acts as an enable signal to 4-input nand gates.                                                               | 6.2    | One (1) possible wrong c<br>will be executed when co                                |            | 6.2                | 1. 58                      | VI      |

| 7.0 Input Buffer<br>and inverter<br>U2D, U3E  | 7.1 U2D, U2  | E Fail   | Low . 70        | 7.1   | U2D will act as an enable signal<br>to 4-input nand gates, U3A, U3B,<br>U4A, U4B, U7A, U7B, U8A, and<br>U8B   | 7.1    | Failure fo UZD will perm<br>possible wrong command<br>executed when command         | d to be    | 7.1                | 7.36                       | VI      |

|                                               |              |          |                 |       | U2D will act as an inhibit signal<br>to 4 input nand gates.                                                   |        | When U2D fails, sixty-th<br>commands will be inoper<br>not capable of being exer    | rative and |                    | ·                          |         |

|                                               |              | - ;      |                 |       |                                                                                                               |        |                                                                                     |            |                    |                            |         |

,

|                           | FAILURE MODE, EFFEC    | T& CRI        | TICA     | LITY ANALYSIS                                                                                                             |     | END ITEM<br>Command Decoder<br>ASS'Y<br>Decode Gates<br>230                                                                                                                                                                              | 57626 | DATE 6-    | 1-71    |

|---------------------------|------------------------|---------------|----------|---------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|---------|

| PART/COMPONENT            | FAILURE MODE           |               | ļ        | EFFECT OI                                                                                                                 | FAI | ILURE                                                                                                                                                                                                                                    | FAILU |            | CRITIC- |

| SYMBOL.                   |                        | (α)           | ļ        | ASSEMBLY                                                                                                                  |     | END ITEM                                                                                                                                                                                                                                 |       | न्द्र      |         |

| 7.0 (Continued)           | 7.2 U2D, U2E Fail High | . 30          | 7.2      | U2d will act as an inhibit signal to<br>4-input nand gates.<br>U2E will act as an enable signal to<br>4-input nand gates. | 7.2 | <ul> <li>When U2D fails, sixty-three (63)</li> <li>commands will be inoperative and not capable of being executed.</li> <li>Failure of U2E will permit one (1)</li> <li>possible wrong command to be executed when commanded.</li> </ul> | 7.2   | 3.15       | v       |

| 8.0 Input Buffer:<br>U2F  | 8.1 U2F Fail Low       | . 70          | 8.1      | Acts as an inhibit signal to 4-input<br>nand gates, U5A, U5B, U6A, U6B,<br>U9A, U9B, U10A, and U10B.                      | 8.1 | Fifty-one (51) commands will be<br>inoperative and not capable of being<br>executed.                                                                                                                                                     | 8.1   | 3.68       | v       |

|                           | 8.2 U2F Fail High      | . 30          | 8.2      | Acts as an enable signal to 4-input nand gates.                                                                           | 8.2 | One (1) possible wrong command will be executed when commanded.                                                                                                                                                                          | 8.2   | 1. 58      | VI      |

| 9.0 Input Buffer:<br>UllA | 9.1 UllA Fail Low      | . 70<br>.7' ) | 9.1      | Acts as an inhibit signal to 4-input<br>nand gates, U13A, U13B, U15A,<br>and U15B.                                        | 9.1 | Fifty-three (53) commands will be<br>inoperative and not capable of being<br>executed.                                                                                                                                                   | 9.1   | 3. 68      | v       |

|                           | 9.2 UllA Fail High     | • 30<br>• 10  | 9.2      | Acts as an enable signal to 4-input nand gates.                                                                           | 9.2 | One (1) possible wrong command will be executed when commanded.                                                                                                                                                                          | 9.2   | 1. 58<br>7 | VI      |

|                           |                        |               | <b>.</b> | · ·                                                                                                                       |     |                                                                                                                                                                                                                                          |       |            | •       |

|                           |                        |               |          |                                                                                                                           |     |                                                                                                                                                                                                                                          |       |            |         |

|                           |                        |               |          |                                                                                                                           |     |                                                                                                                                                                                                                                          |       |            |         |

|                           |                        |               |          |                                                                                                                           |     |                                                                                                                                                                                                                                          |       | · ·        |         |

|                           |                        |               |          | •                                                                                                                         |     |                                                                                                                                                                                                                                          |       |            |         |

|                           |                        |               |          |                                                                                                                           |     |                                                                                                                                                                                                                                          |       |            |         |

|                           |                        |               |          | · · · ·                                                                                                                   |     | •                                                                                                                                                                                                                                        |       |            | •       |

|                           |                        |               |          | •                                                                                                                         |     |                                                                                                                                                                                                                                          |       |            |         |

|                           |                        |               |          |                                                                                                                           |     |                                                                                                                                                                                                                                          |       |            |         |

. .

-

.

| •                                                                                |         | • • • • • • • • • • • • • • • • • • •                                                                  |              |       | •                                                                                                             |          | SYSTEN ALSEP                                                              | M. Papai                | oan           | ATM 949       | , REV     |

|----------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------|--------------|-------|---------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------------------------------|-------------------------|---------------|---------------|-----------|

|                                                                                  |         |                                                                                                        |              |       |                                                                                                               |          | END ITEM<br>Command Decoder                                               | DWG NO.                 |               | PAGE 16       |           |

|                                                                                  | FAILUR  | RE MODE, EFFECT &                                                                                      | <u>k CRI</u> | TICAL | ITY ANALYSIS                                                                                                  |          | ASS'Y<br>Decode Gates                                                     | DWG NO. 236             | 7626          | DATE 6-       | 1-71      |

| PART/COMPONENT                                                                   | 1       | FAILURE MODE                                                                                           | ľ            | · .   | EFFECT OF                                                                                                     | F FAILUR |                                                                           |                         | FAIL<br>PROBA | URE<br>BILITY | CRIT      |

| SYMBOL                                                                           | <b></b> |                                                                                                        | <u>(a)</u>   | ļ     | ASSEMBLY                                                                                                      | <b> </b> | END ITEM                                                                  |                         | Q ×           | BILITY<br>105 | ~ <u></u> |

| 10.0 Input Buffer:<br>UllB                                                       | 10.1    | UllB fail low                                                                                          | .70          | 10.1  | Acts as an inhibit signal to<br>4-input nand gates, U14A, U14B,<br>U15A and U15B.                             | i        | Fifty-four (54) command<br>noperative and not capa<br>being executed,     |                         | 10.1          | 3, 68°        | v         |

|                                                                                  | 10.2    | UllB fail high                                                                                         | • 30         | 10.2  | Acts as an enable signal to<br>4-input nand gates.                                                            | 10.2 C   | Dne (1) possible wrong o<br>will be executed when co                      | command<br>ommanded.    | 10.2          | 1.58          | VI        |

| 11.0 Input Buffer:<br>UllC                                                       | 11.1    | UllC fail low                                                                                          | .70          | 11.1  | Acts as an inhibit signal to<br>4-input nand gates, U12B, U13B,<br>U14B and U15B.                             | i i      | Fifty-four (54) command<br>noperative and not capa<br>being executed.     |                         | 11.1          | 3. 68         | v         |

|                                                                                  | 11.2    | U11C fail high                                                                                         | . 30         | 11.2  | Acts as an enable signal to<br>4-input nand gates.                                                            |          | One (1) possible wrong (<br>will be executed when co                      |                         | 11.2          | 1. 58<br>1:   | VI        |

| 12.0 Input Buffer;<br>Ul1D                                                       | 12.1    | U11D fail low                                                                                          | .70          | 12.1  | Acts as an inhibit signal to<br>4-input nand gates, U12A, U12B,<br>U13A, U13B, U14A, U14B, U15A,<br>and U15B. | v v      | One hundred-four (104)<br>will be inoperative and p<br>of being executed. |                         | 12.1          | 3. 68         | v         |

|                                                                                  | 12,2    | UllD fail high                                                                                         | . 30         | 12.2  | Acts as an enable signal to<br>4-input nand gates.                                                            |          | Possible random commi<br>executed.                                        | and will be             | 12 <b>. 2</b> | 1. 58         | VI        |

| FIRST TIER<br>13.0 U3A, U3B,<br>U4A, U4B,<br>U5A, U5B,<br>U6A, U6B,<br>U7A, U7B, | 13.1    | Fail low<br>U3A, U3B, U4A, U4B,<br>U5A, U5B, U6A, U6B,<br>U7A, U7B, U8A, U8B,<br>U9A, U9B, U10A, U10B  | . 70         | 13.1  | Acts as an inhibit signal to 2nd<br>tier gate.                                                                | n        | A possible eight (8) wro<br>nands will be executed<br>commanded.          | ng com-<br>when         | 13.1          | 176. 60       | vI        |

| U8A, U8B<br>U9A, U9B,<br>U10A, U10B                                              | 13.2    | Fail high<br>U3A, U3B, U4A, U4B,<br>U5A, U5B, U6A, U6B,<br>U7A, U7B, U8A, U8B,<br>U9A, U9B, U10A, U10B | . 30         | 13.2  | Acts as an enable signal to 2nd<br>tier gate.                                                                 | V V      | A maximum of eight (8)<br>will be inoperative and p<br>of being-executed. | commands<br>not capable | 13.2          | 75. 69        | V)        |

| ана.<br>Алана <b>н</b>                                                                                     |                                                                                                                                  |                                                         | SYSTEM ALSEP PREPARED BY<br>ALSEP M. Papaio<br>END ITEM<br>Command Decoder OWG NO.                                 |                                               |                    |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------|

|                                                                                                            | FAILURE MODE, EFFECT & CRI                                                                                                       | TICALITY ANALYSIS                                       |                                                                                                                    | PAGE 17<br>07626 04TE 6                       | <u>of</u><br>5-1-7 |

| PART/COMPONENT<br>SYMBOL                                                                                   | FAILURE MODE (Q.)                                                                                                                |                                                         | FAILURE ·                                                                                                          | FAILURE<br>PROBABILITY<br>Q × 10 <sup>5</sup> | CRI<br>ALI         |

| 14.0 U12A, U12B,<br>U13A, U13B,<br>U14A, U14B,<br>U15A, U15B                                               | 14.1 Fail low .70<br>U12A, U12B, U13A, U13B,<br>U14A, U14B, U15A, U15B                                                           |                                                         | .1 A possible eight (8) wrong com-<br>mands will be executed when<br>commanded.                                    | 14.1 88.30                                    | v                  |

|                                                                                                            | 14.2 Fail high 30<br>U12A, U12B, U13A, U13B,<br>U14A, U14B, U15A, U15B                                                           | 14.2 Acts as an enable signal to 2nd 14.<br>tier gate.  | .2 A maximum of fourteen (14) com-<br>mands will be inoperative and not<br>capable of being executed.              | 14.2 37.84                                    |                    |

| SECOND TIER<br>15.0 U11E, U11F,<br>U16A, U16B,<br>U17A, U17B,<br>U18A, U18B,<br>U19A, U19B,<br>U20A, U20B, | 15.1 Fail low .70<br>U11E, U11F, U16A, U16B,<br>U17A, U17B, U18A, U16B,<br>U19A, U19B, U20A, U20B,<br>U20C, U20D, U20E, U20F     | 15.1 Acts as an inhibit signal to 3rd 15.<br>tier gate. | .1 A maximum of eight (8) commands<br>will be inoperative and not capable<br>of being executed.                    | 15.1 58.87                                    | v                  |

| U20C, U20D,<br>U20E, U20F                                                                                  | 15.2 Fail high .30<br>U11E, U11F, U16A, U16B, .3<br>U17A, U17B, U18A, U18B,<br>U19A, U19B, U20A, U20B,<br>U20C, U20D, U20E, U20F | 15.2 Acts as an enable signal to 3rd 15.<br>tier gate.  | .2 A maximum of eight (8) wrong<br>commands will be executed when<br>commanded.                                    | 15.2 25.23<br>4                               | v                  |

| 16.0 U16C, U16D,<br>U16E, U16F,<br>U17C, U17D,<br>U17E, U17F,<br>U18C, U18D,                               | 16.1 Fail low                                                                                                                    | 16.1 Acts as an inhibit signal to 3rd 16.<br>tier gate. | <ul> <li>A maximum of eight (8) commands<br/>will be inoperative and not capable<br/>of being executed.</li> </ul> | 16.1 58.87<br>                                | <b>v</b>           |

| U18E, U18F,<br>U19C, U19D,<br>U19E, U19F                                                                   | 16.2 Fail high                                                                                                                   | 16.2 Acts as an enable signal to 3rd 16.<br>tier gate.  | .2 A maximum of eight (8) wrong<br>commands will be executed when<br>commanded.                                    | 16.2 25.23                                    | V                  |

|        |                                 |         |                                                       | •      | · .                           | ••••••   |                                                             |                                             |                       |            |

|--------|---------------------------------|---------|-------------------------------------------------------|--------|-------------------------------|----------|-------------------------------------------------------------|---------------------------------------------|-----------------------|------------|

| •      |                                 |         | ,<br>                                                 |        |                               |          | SYSTEM ALSE P M. Papain<br>END ITEM<br>Command Decoder      |                                             | <u>m 949</u><br>GE 18 |            |

|        |                                 | FAILURE | MODE, EFFECT & CR                                     | TICALI |                               |          | Command Decoder<br>ASSY<br>Decode Gate<br>2367              | 7626 DAT                                    | 0-1                   | 1-71       |

|        | /CONFONENT<br>MBOL              |         | FAILURE MODE (OL)                                     |        | EFFECT O                      | F FAILUR | END ITEM                                                    | FAILURE<br>PROBABILI<br>Q × 10 <sup>5</sup> | TY                    |            |

| 17.0   | 104 Two-<br>Input Nand<br>Gates | 17.1    | Fail low .68                                          | T      | Permanent Command             |          | Switch to redundant unit to regain functions.               | 17.1 56                                     |                       | <b>v</b> . |

| sheets | usively on<br>4,5 & 6 of        | 17.2    | Fail high . 30                                        | 17.2   | No commands will be executed. | 17.2     | Switch to redundant unit to regain functions.               | 17.2 24                                     |                       | <b>v</b>   |

| Dwg.   | 2349326)                        | 17.3    | Fail low (short).01                                   |        | Permanent Command             | 17.3     | Cannot be removed by switching to redundant unit.           | 17.3                                        | 8. ZC                 | 11         |

|        | •                               | 17.4    | U25A - Fail Low except .01<br>for pulldown transistor | 17.4   | Permanent Command             | 17.4     | Same as 17.2                                                | 17.4                                        | 4.08                  | v          |

|        | · ,                             | .17.5   | U25A - Pulldown transistor<br>on chip U25A fails low  | 17.5   | Permanent Command             | 17.5     | Single point failure - loss<br>of all data except for LSPE. | 17.5                                        | 1.36                  | I          |

|        |                                 |         |                                                       |        | · · ·                         | -<br>-   |                                                             |                                             |                       |            |

|        | •                               |         | •                                                     |        | •                             |          |                                                             |                                             |                       |            |

|        | ·                               |         | •                                                     |        |                               |          | •                                                           |                                             |                       | •          |

|        |                                 |         | •                                                     |        | · · · · · · · ·               |          |                                                             |                                             |                       |            |

|        | 8                               |         | •                                                     |        |                               |          |                                                             |                                             |                       |            |

|        | •                               |         |                                                       |        |                               |          |                                                             |                                             |                       |            |

|        |                                 |         |                                                       |        |                               |          |                                                             |                                             |                       |            |

|        |                                 |         |                                                       |        |                               |          | •                                                           |                                             |                       | •          |

|        |                                 |         |                                                       |        | •                             |          |                                                             |                                             |                       |            |

|                                                                                                 |                                                                                                        |                                                                                                                 |                                                                                      | $\bigcirc$        |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------|

|                                                                                                 | AILURE MODE, EFFECT &                                                                                  | CRITICALITY ANALYSIS                                                                                            | SYSTEM ALSEP PREPARED E<br>END ITEM<br>Command Decoder<br>ASS'Y<br>Control Logic 236 | D107.10 0         |

| PART/COMPONENT                                                                                  |                                                                                                        | EFFECT OF                                                                                                       |                                                                                      | FAILURE CRITIC    |

| SYMBOL                                                                                          | FAILURE MODE                                                                                           | ac) ASSEMBLY                                                                                                    | END ITEM                                                                             | PROBABILITY ALITY |

| 1.0 Counter M/Pro-<br>gram Counter<br>Circuitry and                                             | 1.1 Low - U5, U9A, U9B, U4B .<br>High - U8A                                                            | 24 1.1 No Counter Output                                                                                        | 1.1 Permanent Low Level Out                                                          | 38.3 V            |

| Input and Output<br>Buffers: U5,<br>U9A, U9B, U1A,                                              | 1.2 Low - U8A<br>High - U4B                                                                            | 1.2 No Counter Output                                                                                           | 1.2 Permanent High Level Out                                                         | 8.99 V            |

| U1B, U7A, U7B,<br>U7C, U8A, U4B                                                                 | 1.3 Low - UIA, UIB<br>High - UIA, UIB                                                                  | 133 1.3 No Clock Input                                                                                          | 1.3 Permanent Low Level Out                                                          | 15.73 V           |

| •                                                                                               | 1.4 High - U5, U9A                                                                                     | 200 1.4 Erroneous Count                                                                                         | 1.4 Output - Count of 3                                                              | 23.65 V           |

|                                                                                                 | 1.5 Low - U7A, U7C<br>High - U7B, U9B                                                                  | 180 1.5 Erroneous.Count                                                                                         | 1.5 Output - Count of 4                                                              | 21.29 V           |

|                                                                                                 | 1.6 Low - U7B<br>High - U7A, U7C                                                                       | 087 1.6 Erroneous Count                                                                                         | 1.6 Output - Count of 8                                                              | 10.29 V           |

| 2.0 Counter M/Pro-<br>gram Counter<br>Circuitry and                                             | 2.1 Low - U10A, U11A<br>High - U10A, U11A                                                              | 2.1 No clock input to counter Gate U13A permanently high.                                                       | 2.1 No Command Executed                                                              | 15.77 <b>v</b>    |

| Input and Output<br>Buffers:. U12A,<br>U14A, U14B,<br>U10A, U11A,<br>U16A, U13C,<br>U11B, U13A, | <b>2.2 U12A</b> $\begin{array}{c} Q & \overline{Q} \\ 1 & 1 \\ 1 & 0 \\ 0 & 1 \\ 0 & 0 \end{array}$    | 240 2.2 Gate UI3A permanently high.                                                                             | 2.2 No Command Executed                                                              | 31.54 🗸           |

| U13B                                                                                            | 1 1<br>1 0<br>0 1                                                                                      | <ul> <li>20</li> <li>2.3 Counter keeps cycling to a count of</li> <li>2. Gate U13A permanently high.</li> </ul> | 2.3 No Command Executed                                                              | 15.77 V           |

|                                                                                                 | $\begin{array}{ccc} 0 & 0 \\ 2.4 & U14B & \underline{Q} & \underline{Q} \\ 1 & 1 \\ 1 & 0 \end{array}$ | 060 2.4 Counter becomes inhibited after<br>first count.                                                         | 2.4 Random Commands Executed                                                         | 7.88 V            |

|                                                                                                 | 2.5 U14B <u>Q Q</u><br>0 1<br>0 0                                                                      | 060 2.5 Flip-Flops U12A and U14A operate<br>continuously. Gate U13A perma-<br>nently high.                      | 2.5 No Command Executed                                                              | 7.88 V            |

| •                                                                                               | •                                                                                                      |                                                                                                                 |                                                                                      |                   |

| PAILURE MODE, EFFECT & CRITICALITY ANALYSIS       Do THE MODE, OF FRAURE<br>Command Decoder No Recommend Decoder No | •   |                                   |             |                                       |                   | •           |                                   | ·     |                                                     |                       |            |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------|-------------|---------------------------------------|-------------------|-------------|-----------------------------------|-------|-----------------------------------------------------|-----------------------|------------|----------|

| FAILURE MODE, EFFECT & CRITICALITY ANALYSIS       Secantical Legits       PAILURE MODE       CRITICALITY ANALYSIS       PAILURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | •                                 |             |                                       |                   |             |                                   |       | ALSEP<br>END ITEM                                   | M. Papai<br>DWG NC.   | oan ATM 49 |          |

| PART/COMPORENT<br>SYMBOL         PAILURE MODE<br>(C)         CRT<br>(C)         EFFECT OF PAILURE<br>ASSEMBLY         PAILURE<br>END ITEM         PAILURE<br>(CRT<br>(CRT)           2.6         Low - UIAA<br>High - UIGC, UIA, UIBA         .120         2.6         No Gated Parity Clock         2.6         No parity check is made and<br>command with be accuted         15.77         VI           2.7         Low - UIAC, UIA, UIBA         .28         Low - UIBA         .028         2.7         No Command Executed         29.96         V           2.8         Low - UIBA         .028         .29         High - UIAA         .024         2.9         No Command Executed         3.66         VI           2.9         High - UIAA         .024         .024         .29         Random commands are executed.         3.15         V           3.0         Address Recormition Enable<br>Filtp-Tiop: UZ         .1         Low - U2         .620         3.1         Counter enable F. F. will permanentity enable Counter Clock input<br>to M Counter.         3.1         Counter M and N reset lines are<br>inhibited.         24.44         V           2.0         Address Recormition Filtp-Filtp-<br>antion Filtp-Filtp-<br>UID         .32         Counter enable F. F. permanentity         3.2         Counter M will not operate.         14.98         V           4.0         Address Recormition SignAL <th></th> <th></th> <th>FAILU</th> <th>RE MODE, EFFECT</th> <th>&amp; CRIT</th> <th><b>FICA</b></th> <th>LITY ANALYSIS</th> <th></th> <th></th> <th>DWG NO.<br/>23676</th> <th>36 DATE</th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                                   | FAILU       | RE MODE, EFFECT                       | & CRIT            | <b>FICA</b> | LITY ANALYSIS                     |       |                                                     | DWG NO.<br>23676      | 36 DATE    |          |

| High - U16A       Image: Command will be executed.       Image: Command will be executed.       Image: Command will be executed.         2.7       Low - U13C, U13A, U13B       .228       Image: Command Will be executed.       29, 96       V         2.8       Low - U13C, U13B       .028       Image: Command Executed in ASE Mode.       3.68       VI         2.9       High - U13A       .024       Image: Command Executed in ASE Mode.       3.68       VI         3.0       Address Recog.       3.1       Low - U2       High - U1C       .620       3.1       Counter anable F.F. will permanently mable Counter Clock input to M Counter.       3.1       Counter anable F.F. permanently to M Counter.       3.1       Counter anable F.F. permanently to M Counter.       3.2       Counter M will not operate.       14.98       V         4.0       Address Recog.       4.1       Low - U3A, U3C       .500       4.1       A permanent low level ADDRESS       4.1       VIII Inbibit the resetting of M and N       15.77       V         4.0       Address Recog.       5.1       Low - U3B, U5A       .500       5.1       Permanent low level ADDRESS       4.1       VIII Inbibit the resetting of M and N       15.77       V         4.0       Address Recog.       5.1       Low - U3B, U5A       .500       5.1       Pe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |                                   |             | FAILURE MODE                          | (a)               |             |                                   | )F FA |                                                     |                       | FAILURE    | CRITIC-  |

| High - U13C, U11B, U13B.0282.8No Command Executed in ASE Mode.3.68VI2.9High - U13A.0242.9Random commands are executed.3.15V3.0Address Recognition Cate and<br>Counter Enable<br>PTIp-Frop: U2<br>U1C, U1D3.1Low - U2<br>High - U1C.6203.1Counter enable F, F, will permanently enable Counter Clock input<br>to M Counter.3.1Counter M and N reset lines are<br>inhibited.24.44V3.2High - U1C.6203.1Counter enable F, F, permasently<br>inhibits Counter Clock input<br>inhibits Counter.3.2Counter M will not operate.14.98V4.0Address Recognition Signal<br>UGA4.1Low - U3B, U3C, 5004.1A permanent low level ADDRESS<br>RECOGNITION SIGNAL.4.1Will inhibit the resetting of M and N15.77Vu3A, U3B, U3C,<br>U6A.5004.2A permanent high level ADDRESS<br>RECOGNITION SIGNAL.4.2Will permit erratic resetting of M and N15.77V5.0Uplink Shift<br>Etable Flip-<br>Flop U6B,<br>U6C5.1Low - U6C.5005.1Permanent low level of U6C.5.1No Command Executed7.88V6.0Command Veril<br>High - U4C, U15B.4676.1Permanent low level of U6C.5.4Random Commands are Executed7.88V6.2Low - U7D, U8C<br>High - U4C, U15B.533.5336.2Permanent low level of WEZP<br>eignal to Data Processor.6.1Partial Failure - System Will Oper-<br>ate14.73VI0.2Low -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . • |                                   | 2.6         |                                       | . 120             | 2.6         | No Gated Parity Clock             | 2.6   |                                                     |                       | 15.77      | VI       |

| 2.9       High - U13A       .024       2.9       Random commands are executed.       3.15       V         3.0       Address Recognition fasts and Counter Enable F, F, will permanently enable Counter Clock input inhibited.       3.1       Counter Enable File-Fibre U2       3.1       Counter Enable File-Fibre U2       3.2       Counter enable F, F, permanently inhibited.       3.1       Counter M and N reset lines are inhibited.       24.44       V         4.0       Address Recognition Fibre Fibre U2       3.2       Counter enable F, F, permanently inhibits Counter Clock input.       3.2       Counter M will not operate.       14.98       V         4.0       Address Recognition Fibre Fibre U3A, U3C       .500       4.1       A permanent low level ADDRESS       4.1       Will inhibits the resetting of M and N       15.77       V         u3A, U3B, U3C       .2       Low - U3B, U6A       .500       4.2       A permanent low level ADDRESS       4.2       Will permit erratic resetting of M and N       15.77       V         u6A       Uplink Shift       5.1       Low - U6C       .500       5.1       Permanent low level of U6C.       5.1       No Command Executed       7.88       V         u6A       .2       Low - U6B       .500       5.2       Permanent low level of U6C.       5.4       Random Commands are Executed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |                                   | 2.7         |                                       | . 228             |             |                                   | 2.7   | No Command Executed                                 |                       | 29.96      | <b>v</b> |