|                              |                                           | NO. REV. NO. |

|------------------------------|-------------------------------------------|--------------|

| Render                       | ALSEP Array E                             | ATM-985      |

|                              | Command Decoder<br>Breadboard Test Report | PAGE OF      |

| Aerospace<br>Sv ems Division |                                           | DATE 2/26/71 |

The following ATM has been prepared to document the testing and test results of the command decoder breadboard for Array E.

| Table of Contents           | 5             |           |

|-----------------------------|---------------|-----------|

| 1.0 Data Demodulator Board  | <br>.: .      | Page<br>3 |

| 2.0 Testing of Logic Boards |               | 8         |

| 3.0 Testing of Breadboard   |               | 9         |

| Figures 1 thru 29           | in the second | 11-39     |

Prepared by: V. C. Kemp

Prepared by: <u>G. W. Alexander</u>

Approved by: B. C. McLeod

| Ber        | Mix |

|------------|-----|

| <b>Ann</b> |     |

|            |     |

## Aerospace Systems Division

| 1 | NÓ.    |      | RE   | . NO. |  |

|---|--------|------|------|-------|--|

|   | ATI    | M-98 | 5    |       |  |

|   | PAGE _ | 2    | OF.  | 39    |  |

|   | DATE   | 2/2  | 6/71 |       |  |

## List of Diagrams

ALSEP Array E Command Decoder

Breadboard Test Report

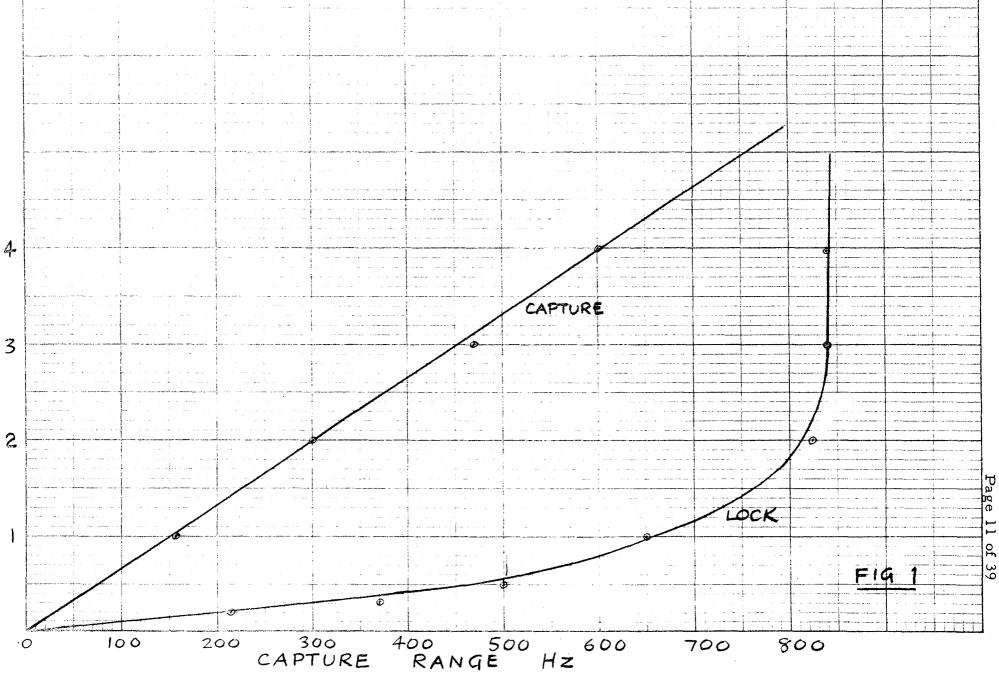

- 1. Phase Lock Loop Capture Range

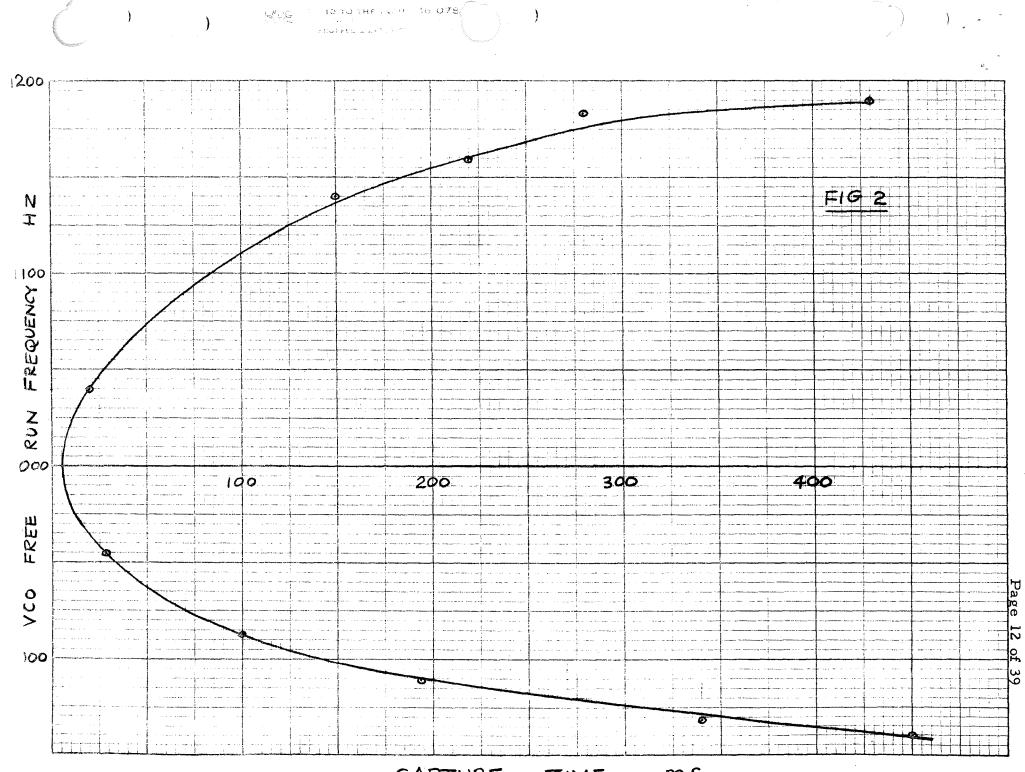

- 2. Phase Lock Loop Capture Time

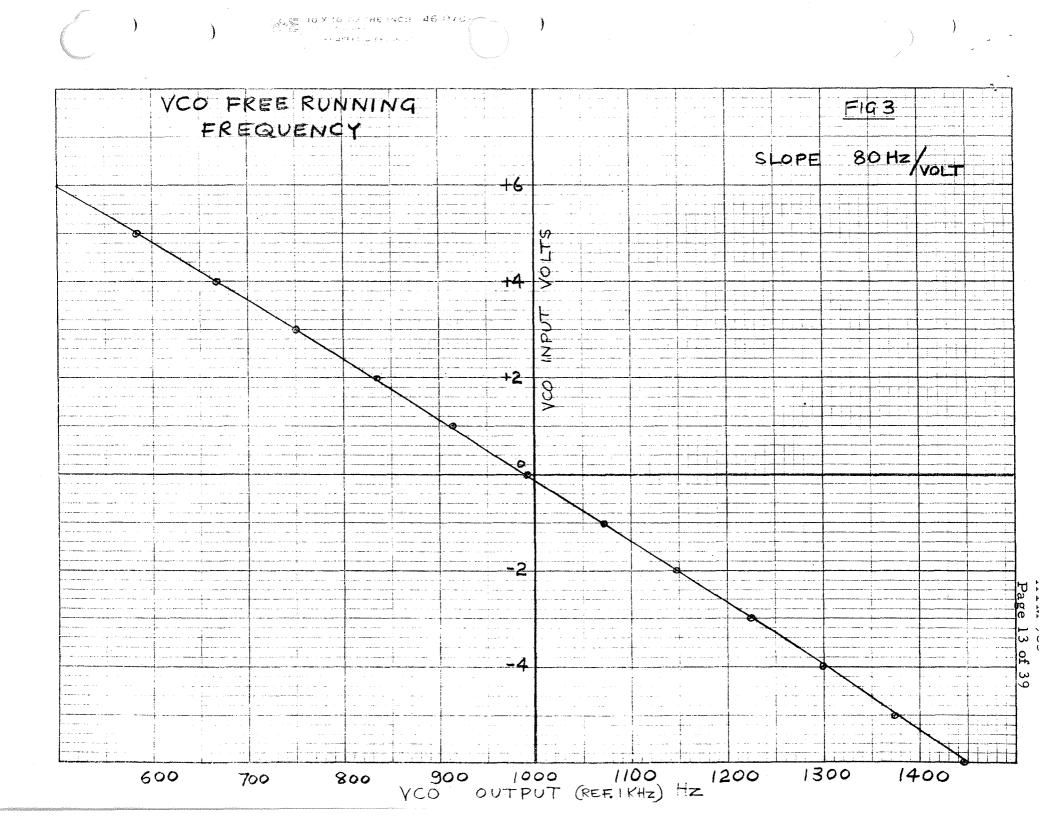

- 3. VCO Characteristics

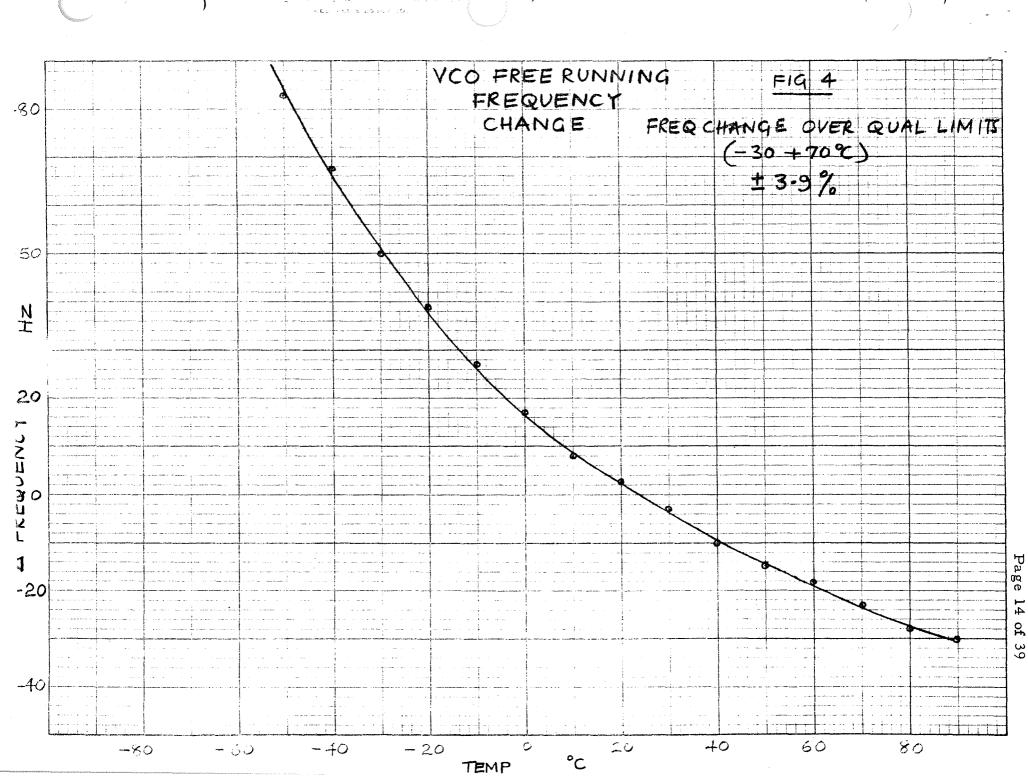

- 4. VCO Free Running Frequency Change with Temperature

- 5. VCO Free Running Frequency Change with Voltage Supply

- 6. Loop Filter Open Loop Gain

- 7. Phase Sensitive Rectifier Characteristics

- 8. Bode Diagram Phase Lock Loop

- 9. Static Phase Error

- 10. Response to White Noise

- 11. Demodulator Performance with Noisy Signal

- 12. Minimum Input Voltage Required

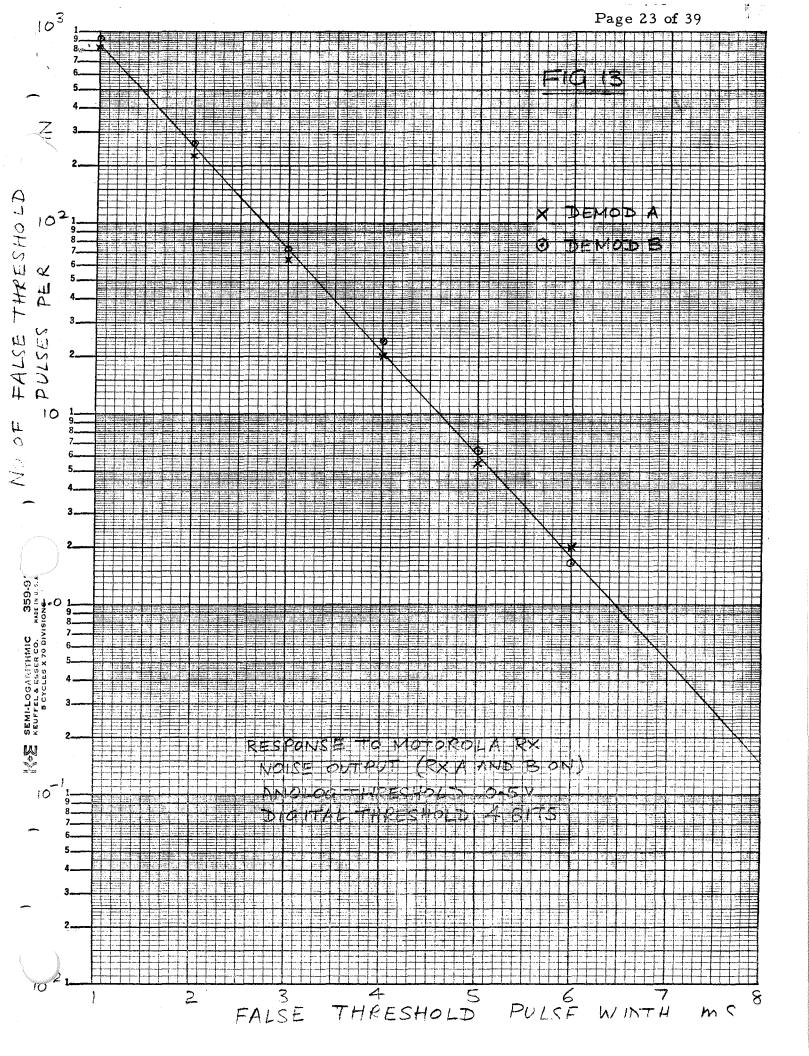

- 13. Response to Motorola Rx Noise Output

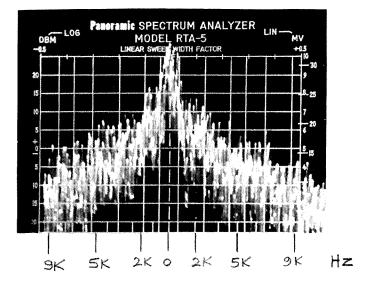

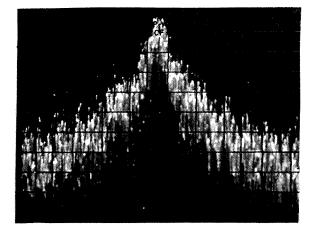

- 14. Receiver Noise Spectra

- 15. Demodulator Waveforms

- 16. Test Set-up for Closed Loop Frequency Response

- 17. Test Set-up for PSR Characteristics

- 18. Threshold Analysis Set-up

- 19. Test Circuit for Signal and Noise Response

- 20. Data Modulator Circuit

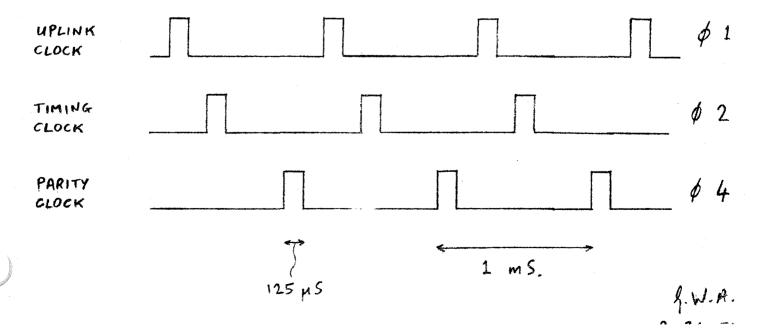

- 21. Uplink Clock Generator

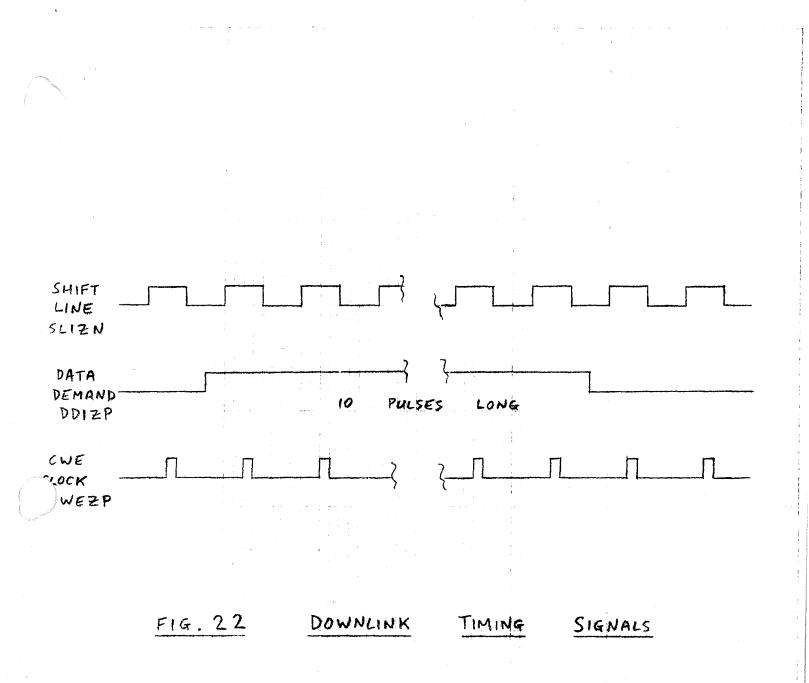

- 22. Downlink Timing Signals

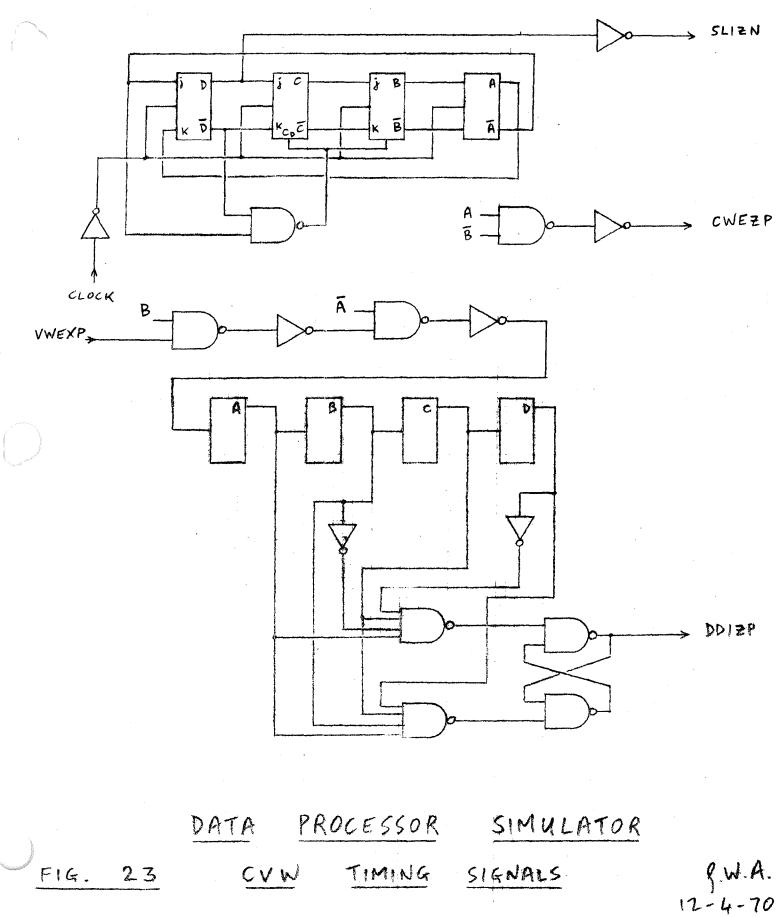

- 23. Data Processor Simulator

- 24. Ripple-off Command Output

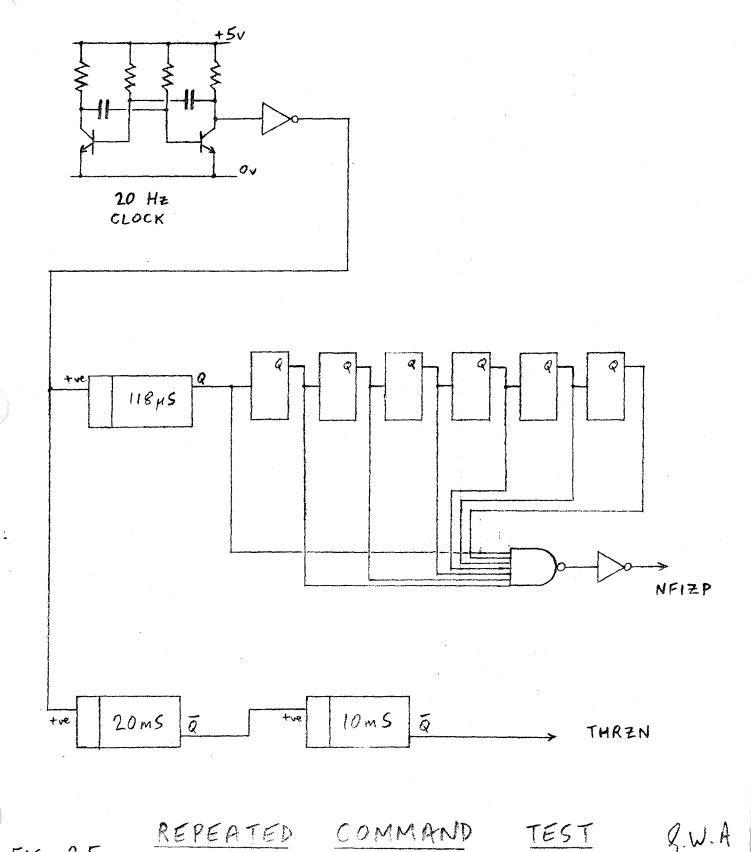

- 25. Repeated Command Test Set

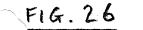

- 26. Power Reset Circuit

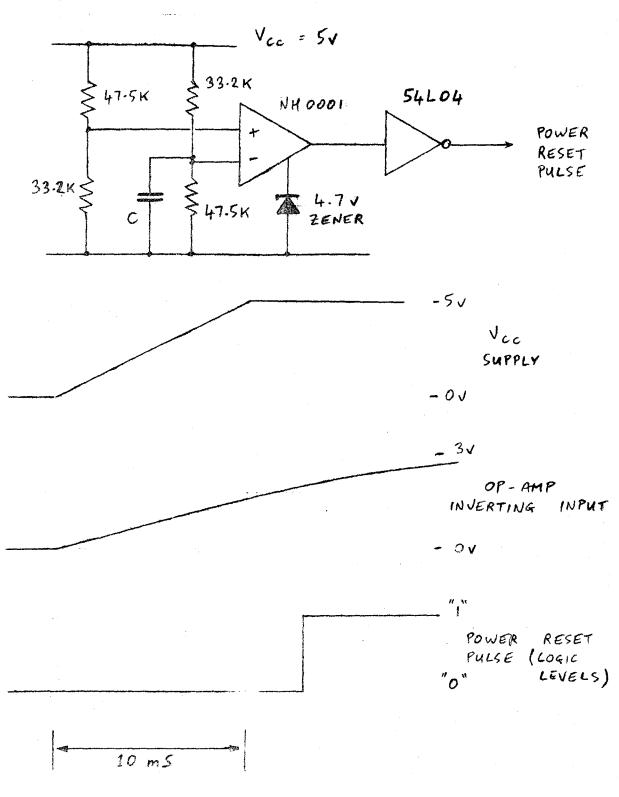

- 27. 5 Volt Supply Variations with Temperature

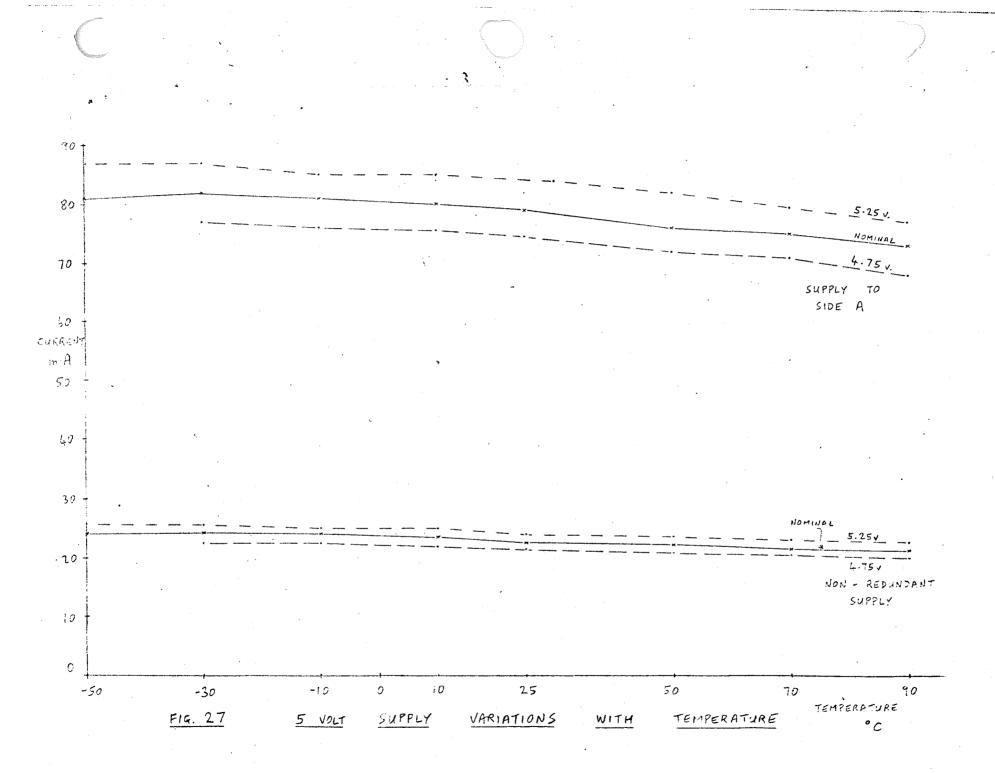

- 28. 12 Volt Supply Variations with Temperature

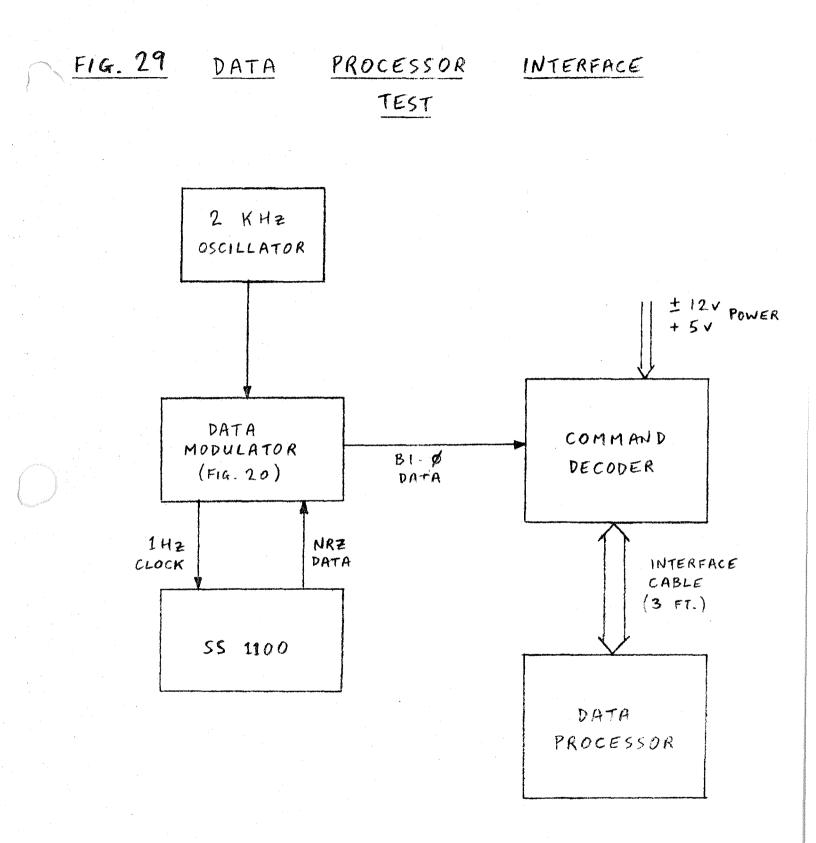

- 29. Data Processor Interface Test

| ,<br>इन्हेल्ला के क           |                                           | NÔ.        | REV. NO. |

|-------------------------------|-------------------------------------------|------------|----------|

| endax                         | ALSEP Array E                             | ATM-985    |          |

| Aerospace                     | Command Decoder<br>Breadboard Test Report | PAGE3      | of       |

| Aerospace<br>Systems Division |                                           | DATE 2/26/ | 71       |

## 1.0 DATA DEMODULATOR BOARD (Drawing No. 2349346)

## 1.1 PHASE LOCK LOOP

## 1.1.1 Lock and Capture Frequency Ranges

These were measured by injecting a variable amplitude and frequency sine wave at the RXMAP input and monitoring the operational amplifier output at AR 3 pin 7, with an oscilloscope on a suitable d. c. range. As the system comes into lock the output of AR 3 jumps to a d. c. level proportional to the phase difference between the two oscillators. The capture range was measured by approaching the VCO free running frequency from both higher and lower frequencies until phase lock was achieved in less than 2 seconds. The capture range is then the difference between these frequencies. The lock range was measured by taking the system out of lock at frequencies above and below the VCO free running frequency. The lock range is then the difference between these two frequencies.

This was repeated for various amplitudes of the input signal and the results are plotted in Figure 1.

#### 1.1.2 Capture Time

The capture time is defined as the time between applying the data at RXMAP and a permanent threshold signal appearing at U8E output.

This was measured when applying the minimum specified 1 and 2 KHz data stream to the RXMAP input. The VCO free running frequency was varied by a variable resistor in place of R9. The threshold signal was monitored at the output of U8E pin 2.

The data stream was switched manually and a triggerable counter was initiated by the data stream and stopped when the threshold signal appeared. The counter then displayed the time between these two events.

| Ser | ndip | 5  |   |  |

|-----|------|----|---|--|

|     |      |    |   |  |

| Aer | oso  | ac | 9 |  |

Systems Division

## ALSEP Array E Command Decoder Breadboard Test Report

| I | NO.    |      | REV. | REV. NO. |  |

|---|--------|------|------|----------|--|

|   | AT N   | M-98 | 5    |          |  |

| ſ | PAGE _ | 4    |      | 39       |  |

| ŀ |        |      |      |          |  |

|   | DATE   | 2/2  | 6/71 |          |  |

The threshold signal was also used to trigger an oscilloscope to ensure that the counter had been stopped at the leading edge of a permanent threshold signal. This was found necessary since the threshold signal sometimes went high intermittently as the system came into lock. For the larger offset VCO frequencies the oscilloscope reading was used to correct the timer reading, due to the problem of threshold "bounce". The measurement was repeated about 20 times for each value of VCO free running frequency and an average value taken.

The VCO free running frequency was measured for each set of readings by grounding  $R_{93}$  at the AR 3 end and measuring the frequency at U3B pin 9. These results are plotted in Figure 2.

## 1.1.3 VCO Frequency

- (a) The VCO frequency was measured on a digital frequency counter monitoring U3B pin 9. A variable frequency sine wave was applied to RXMAP input and the d. c. output of operational amplifier AR 3 pin 7 was measured on a D. V. M. The input frequency was varied and the output of AR 3 and the VCO frequency were measured. The results are plotted in Figure 3.

- (b) The variation of the VCO free running frequency with temperature was measured, with the phase lock loop open. This was done by disconnecting R4 and R 12 from U l and grounding them. The results are plotted in Figure 4.

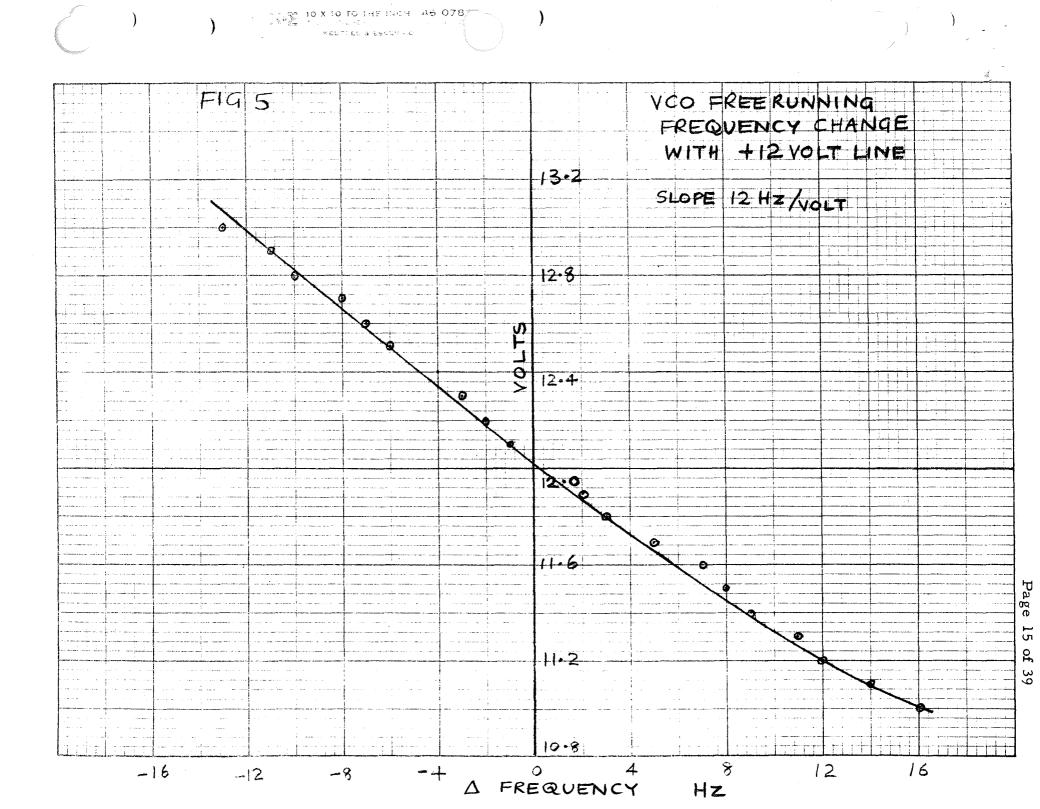

- (c) The variation of the VCO free running frequency with the voltage supplies was measured with the P.LL open as in (b). No change was recorded for the +5 volt and -12 volt lines, but the variation with the +12 volt line is recorded in Figure 5.

## 1.1.4 The Open Loop Frequency Gain Response of the Loop Filter

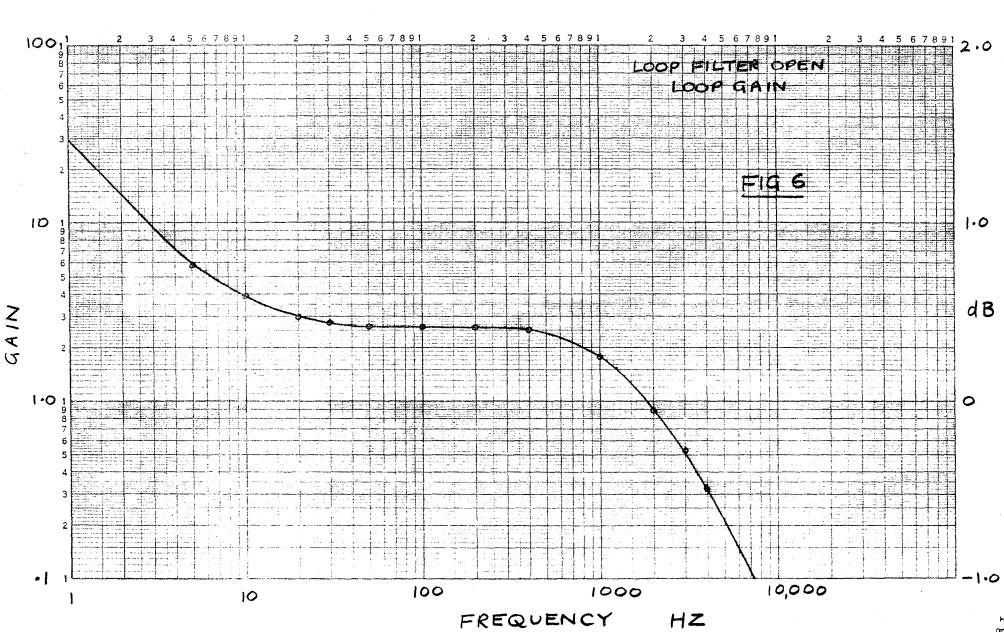

This was measured for the initial system with breaks at 0.17, 10.8, 1060 and 1800 Hz. The variable frequency was injected at  $R_3$  and with switch U1 6-5 closed, the output AR3/7 was monitored with an oscilloscope. These results are plotted in Figure 6.

| Bendix                        | ALSEP Array E                             | NO.<br>ATM-985 |     |  |

|-------------------------------|-------------------------------------------|----------------|-----|--|

| Aerospace                     | Command Decoder<br>Breadboard Test Report | <b>PAGE</b> 5  | of  |  |

| Aerospace<br>Systems Division |                                           | DATE 2/26      | /71 |  |

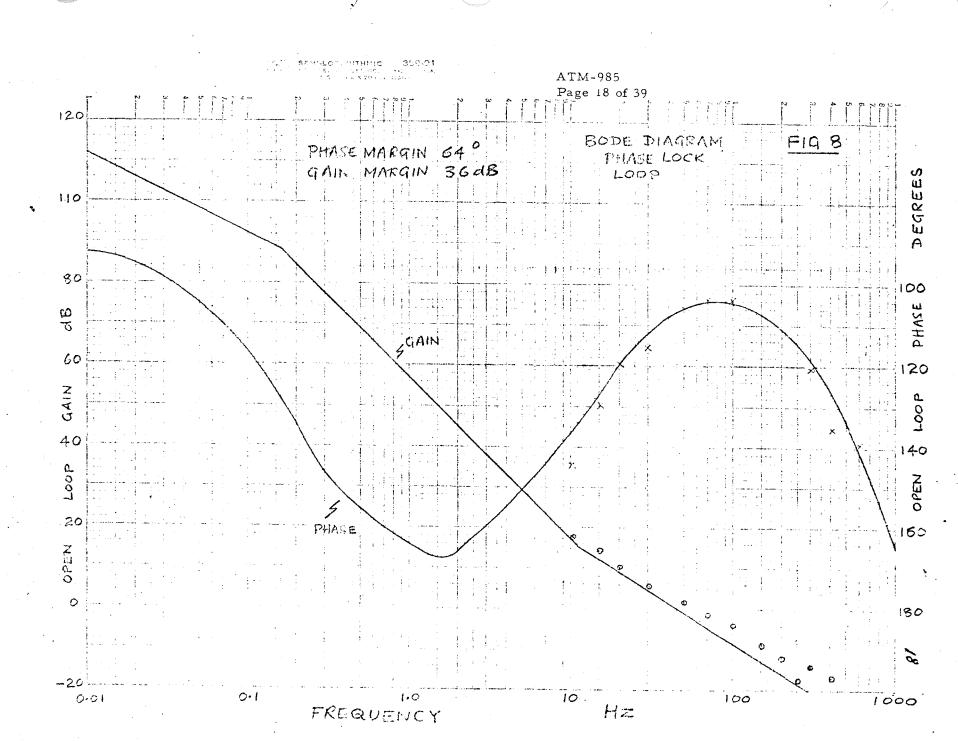

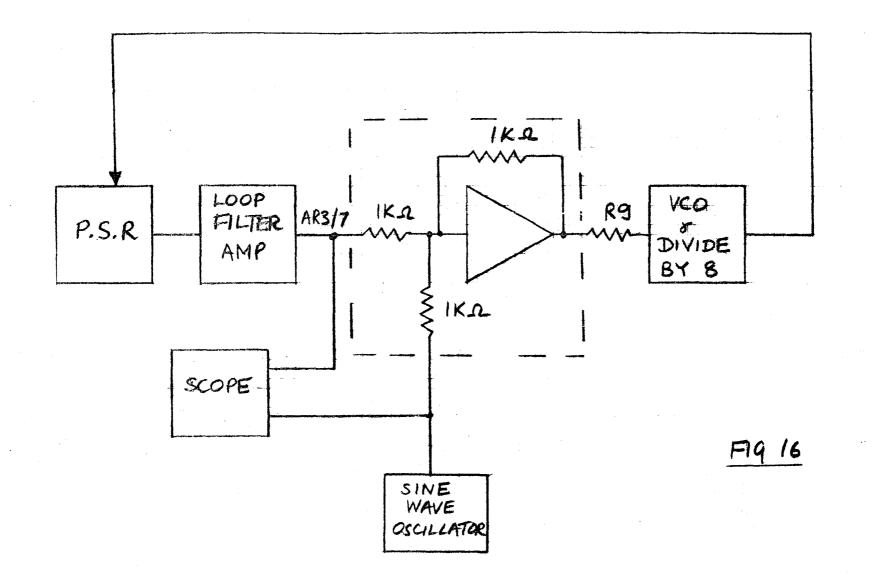

## 1.1.5 The Closed Loop Frequency Response of the Phase Lock Loop

This was measured with the set up shown in Figure 16. The phase lock loop was broken at AR 3 output and a unity gain operational amplifier was inserted. The op amp enables the closed loop to be perturbed by a variable frequency sine wave. The closed loop transfer function is then given by the ratio of the AR 3 output to the input sine wave disturbance. The gain was measured directly from the magnitudes of the two sine waves on the oscilloscope and the phase measurement was performed by a Lissajous technique on the scope. The closed loop results were reflected through a Nicholls Chart to obtain an open loop Bode plot. The Bode plot is shown in Figure 8, together with the theoretical curves.

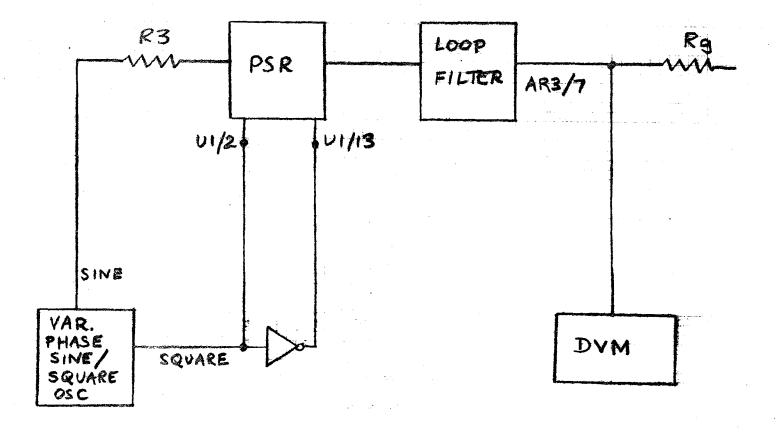

## 1.1.6 P.S R Characteristic

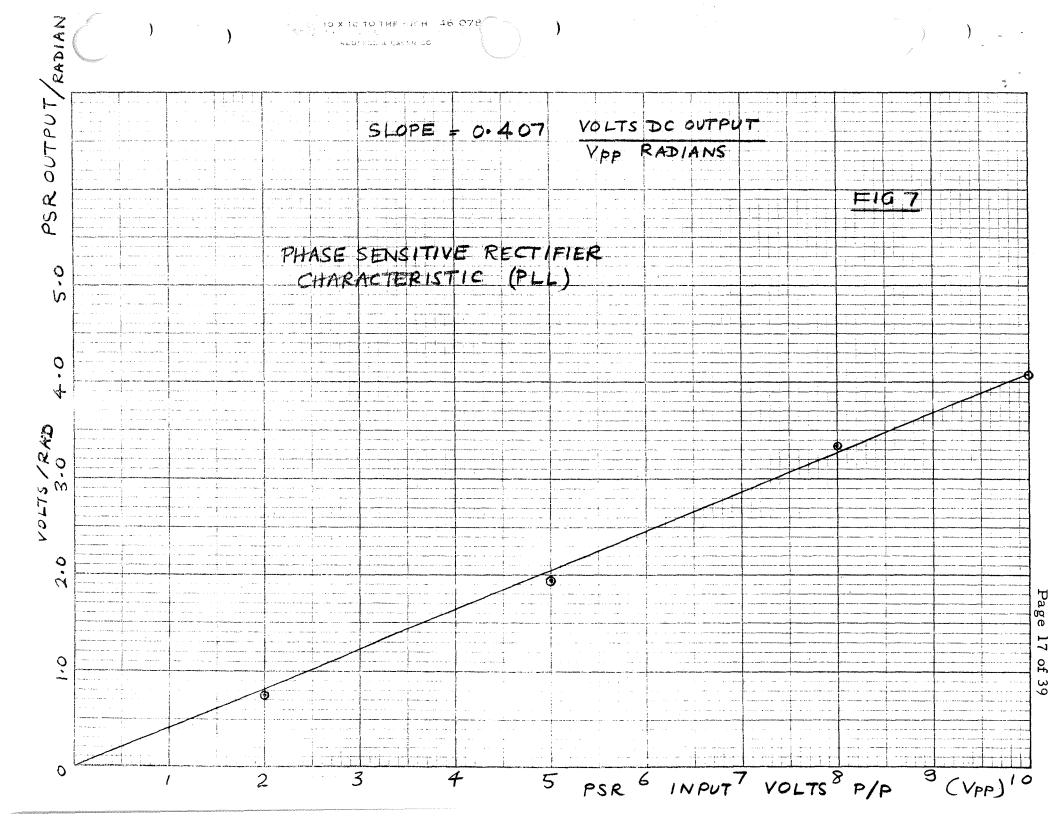

This was measured using the test set up shown in Figure 17. The phase lock loop is broken by disconnecting the switches at U1/2 and U1/3 and disconnecting R 3 at the junction with R 2. A special purpose variable phase sine/square wave oscillator was used together with an inverter to supply synthetic signals to the PSR input and switching lines. The oscillator provided a sine wave output together with a variable phase square wave with a calibrated phase control. The frequency was set at 1 KHz and a set of voltage readings at AR 3/7 was obtained for various sine wave amplitudes and phase differences. The slopes of a family of PSR output volts versus phase shift curves are plotted in Figure 7.

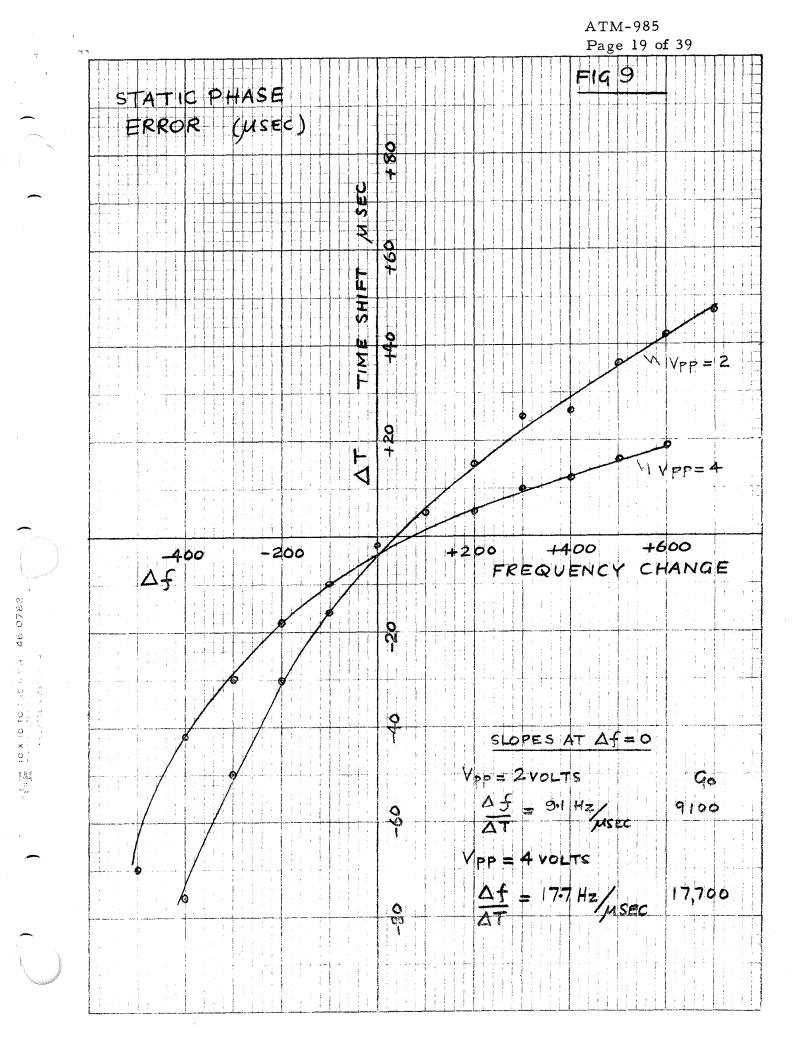

#### 1.1.7 The Static Phase Error of the Phase Lock Loop

This was measured for the maximum and minimum input signal voltage. The measurement was made by injecting a variable sine wave signal at RXMAP and measuring with an oscilloscope the phase difference in  $\mathcal{M}$  sec between the signals at AR 1/7 and U5 B/9. These results are shown in Figure 9.

#### 1.2 DATA DEMODULATOR

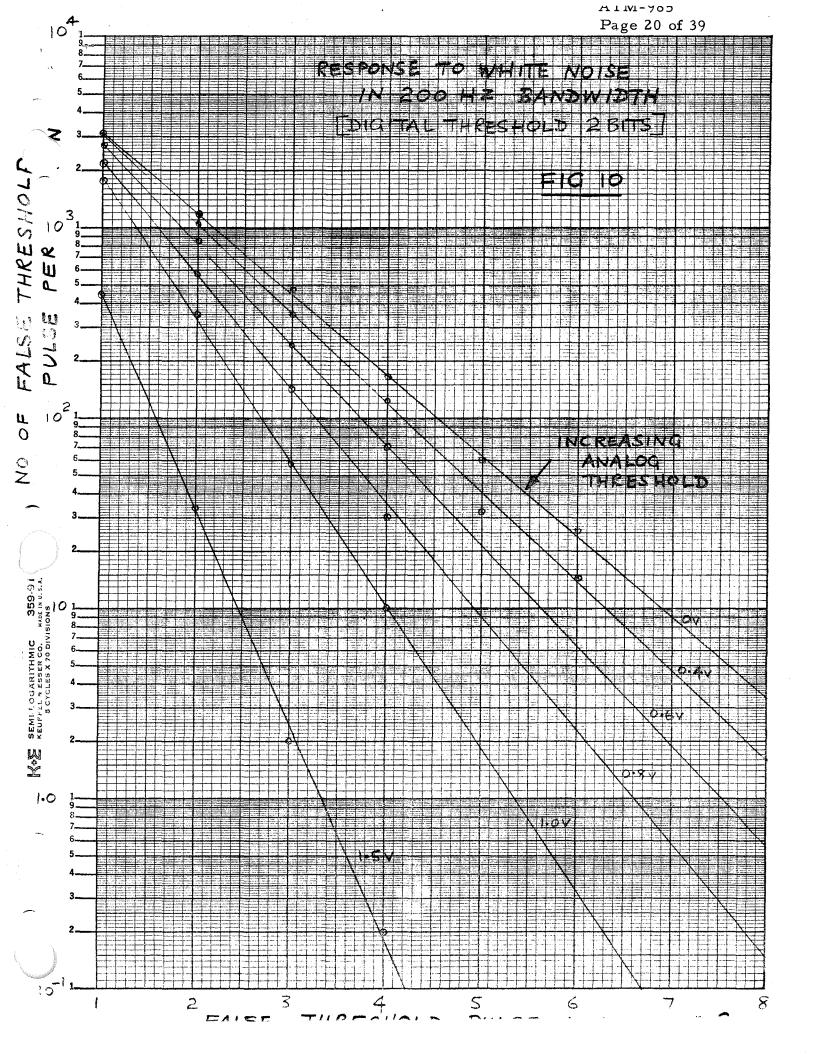

#### 1.2.1 Threshold Response to Noise

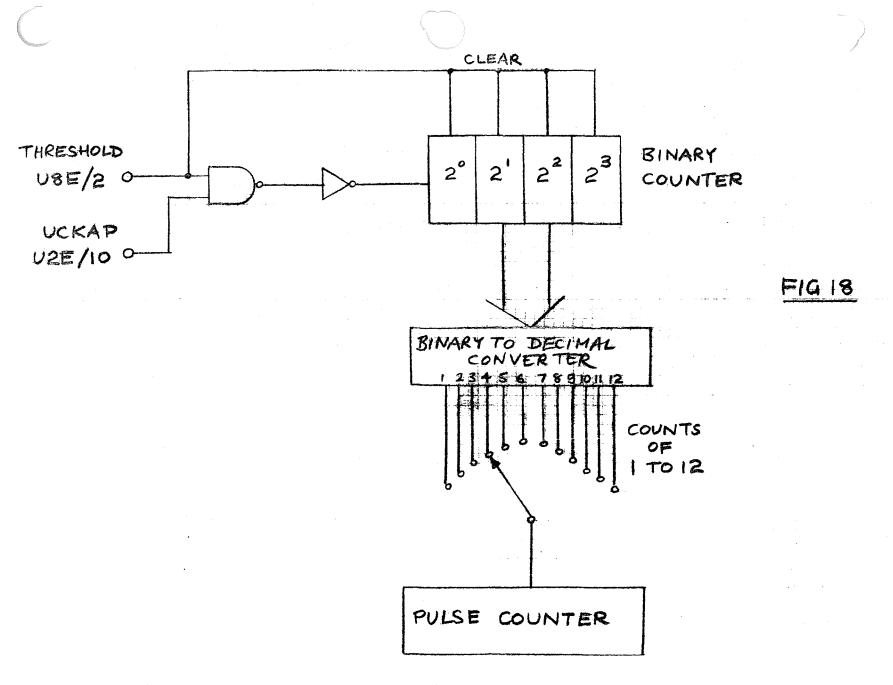

The response of the threshold to a noise input was measured using the test set up of Figure 18. The noise was derived from two sources; firstly, a white noise generator followed by a filter amplifier with a

| Bendix                        |                                                            | <b>NO.</b><br>АТМ-985 | REV. NO.     |

|-------------------------------|------------------------------------------------------------|-----------------------|--------------|

|                               | ALSEP Array E<br>Command Decoder<br>Breadboard Test Report | PAGE6                 | of <u>39</u> |

| Aerospace<br>Systems Division |                                                            | DATE 2/26             | 0/71         |

roll off of 200Hz, secondly, a Motorola receiver with no input signal. The noise was injected at RXMAP input. The duration of the false threshold high pulse was measured with the circuit in Figure 18, by gating the threshold with a 1 ms clock in a binary counter. Then the outputs of the binary to decimal converter were monitored with a digital counter. The number of counts  $N_n$  recorded on the nth channel is given by

$N_n' = N_n - N_{n+1}$

Where  $N_n$  is the number of counts of threshold pulses n milliseconds in duration. Each decimal output channel was monitored one at a time by the counter for a period sufficient to give a meaningful number of samples (about 50). The results are plotted in Figures 10 and 13, for various analog threshold voltages, (measured at the junction of R 28 and R 29, and varied by adjusting R 29).

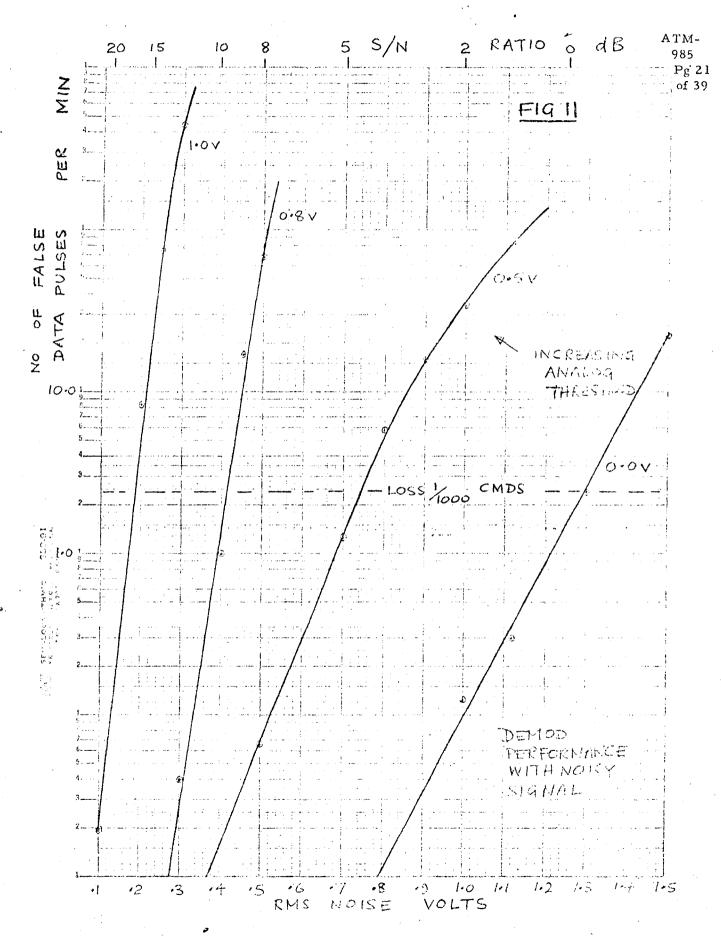

## 1.2.2 Threshold Response to Signals and Noise

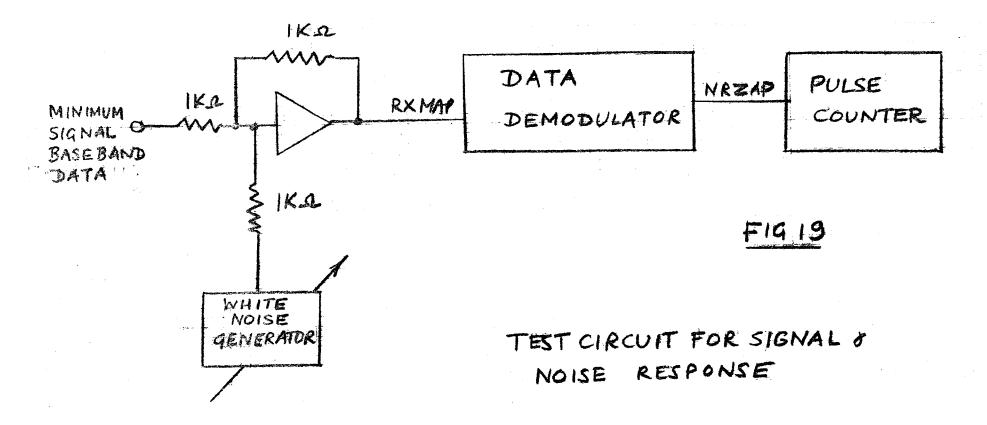

The response of the threshold circuit to noise was measured by monitoring the NRZ data output, when a noisy baseband signal of all 1's was injected at the RXMAP input. The test circuit is shown in Figure 19. A series of curves of number of false data pulses (when NRZ output indicated a zero) versus signal noise ratio were plotted for various analog threshold voltages and the results are shown in Figure 11.

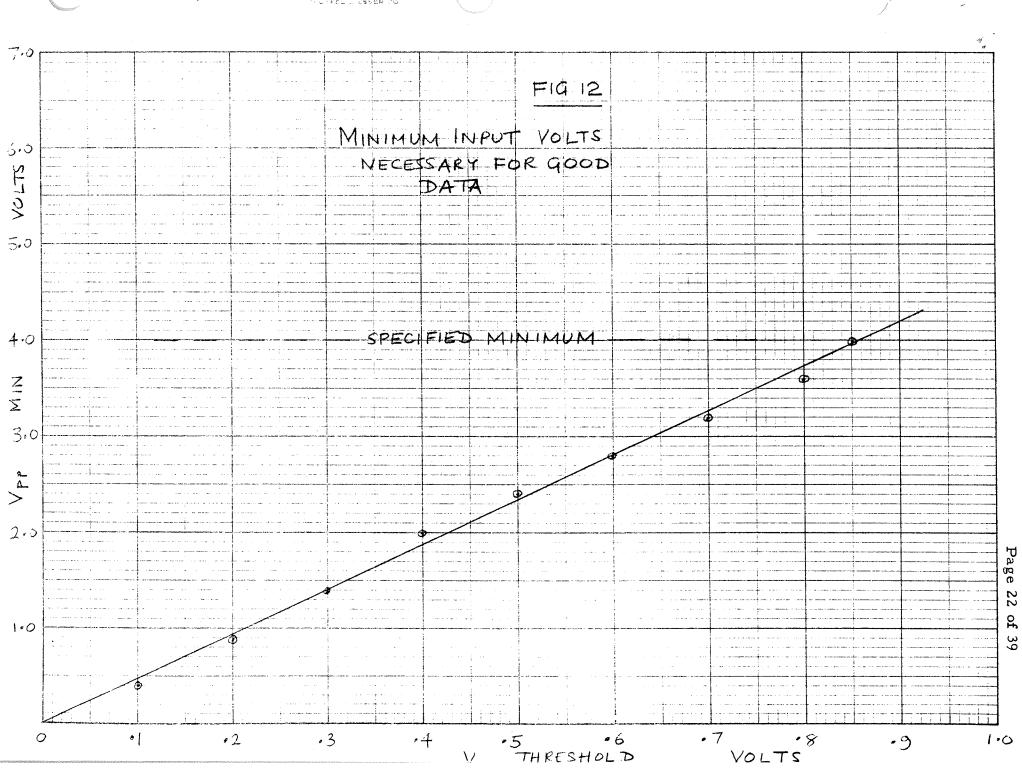

## 1.2.3 Minimum Input Voltage Requirements

The data input level was reduced to the data demodulator until the threshold circuit removed the data output. This level was determined for various analog threshold voltages and these results plotted in Figure 12.

1.2.4 Photographs of the Philco and Motorola receiver noise power spectra are shown in Figure 14.

| Ben | dix_ |  |

|-----|------|--|

|     |      |  |

|     |      |  |

## Aerospace Systems Division

| ALSEP Arra | ay E        |

|------------|-------------|

| Command D  | ecoder      |

| Breadboard | Test Report |

| NÔ.<br>ATM | 1-985 |        | . NO.   |

|------------|-------|--------|---------|

| PAGE _     | 7     | _ OF _ | 39      |

| DATE       | 2/2   | 26/7   | <u></u> |

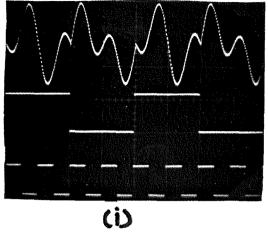

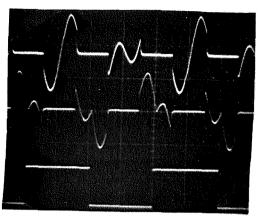

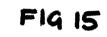

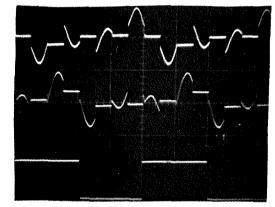

## 1.2.5 A series of 'scope photos of the demodulator are shown in Figure 15.

- Top One/zero baseband data input Middle - One/zero data output Bottom - 2 KHz clock

- (2) Top and Middle PSR outputs in P. L. L. Bottom - One/zero data output

- (3) Top and Middle PSR outputs in Data Detector Bottom - One/zero data output

- (4) Top and Middle Comparator inputs in Data Detector Bottom - One/zero data output

- (5) Top Capacitor Discharge Pulse

Middle 2 KHz

Bottom One/zero data output

- (6) Top Uplink Clock (UCK)

Upper Middle Gate Clock (GCK)

Lower Middle Parity Clock (PCK)

Bottom One/zero data output

## Aerospace Systems Division

| ALSEP Array E          |

|------------------------|

| Command Decoder        |

| Breadboard Test Report |

| <b>NÒ.</b><br>АТМ |        | REV. NO. |  |

|-------------------|--------|----------|--|

| PAGE _            | 8 OF . | 39       |  |

| DATE              | 2/26/7 | 1        |  |

## 2.0 TESTING OF LOGIC BOARDS

## 2.1 DECODE GATE BOARDS

The two decode gate boards where tested with a seven bit input command and command execute pulse provided from a switch panel. Each of the 104 commands were individually tested and found to be the correct command signal for the code inserted.

## 2.2 CONTROL LOGIC BOARDS

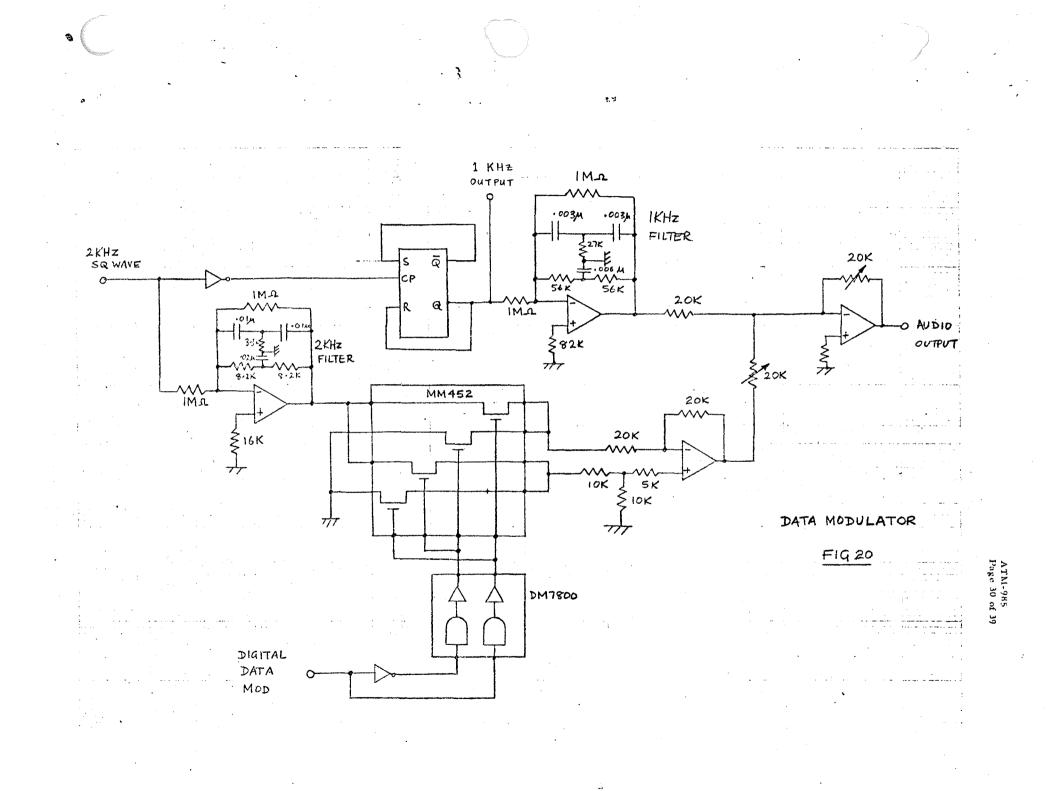

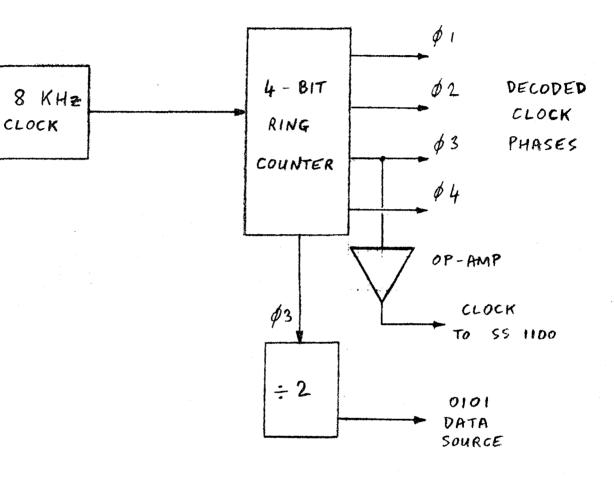

These were tested by using a Bendix SS1100 Signal Simulator, and two external clock sources to simulate uplink and downlink timing. The uplink clock (1 KHz) provided four clock pulse phases, and a clock signal to the SS1100 (Figure 21). The SS1100 has the capability of sending a 21 bit sequence at any repetition rate, with a choice of idle bits in between the sequences. This was used to send the Array E address (octal 151) followed by a command complement and a command. Since this sequence was programmed on individual switches, deliberate address or parity errors could be introduced. The downlink timing simulator produced the CWE clock, shift line (SLIZN) and data demand, all with the correct phase relationship (Figures 22 and 23).

Testing was carried out by providing various commands and checking the events sequence of address recognition, parity checking, command execution, CVW production and reset conditions. Various errors in the address and command complement were introduced, and their effect noted. Commands were sent to switch the command decoder into the LSP data mode, and a check was made on this alternative reset mode.

## 2.3 INTEGRATION OF DATA DEMODULATOR AND CONTROL LOGIC

The already tested data demodulator board was connected to a control logic board, and the control logic tests repeated with data processed by the demodulator. The data was still generated by the SS1100, but a special test board was constructed to generate a biphase modulated signal (Figure 20). This check assured that all the phases of the data demodulator clock were correct with respect to each other and to the NRZ data generated.

| , <b>,</b>     |                        | 1 NO. 1 REV. NO. |

|----------------|------------------------|------------------|

|                | •                      | ATM-985          |

|                | ALSEP Array E          |                  |

|                | Command Decoder        |                  |

| rospace        | Breadboard Test Report | PAGE9 OF39       |

| stems Division |                        | DATE 2/26/71     |

#### 2.4 POWER RESET CIRCUIT

This circuit is used three times in the command decoder, on the command sequencer, and each of the data demodulator boards. The circuit was tested by applying a 10 mS ramp function on the 5 volt logic supply lines, and ensuring that the power reset pulse was negative for a measurable time after  $V_{\rm CC}$  had exceeded 4.5 volts. This 4.5 volt figure is the minimum  $V_{\rm CC}$  at which Texas Instruments will guarantee that their 54L logic will work. The value of the capacitor C is 1.0  $\mu$ F in the data demodulator circuits, but is 6.8  $\mu$ F in the command sequencer circuit. This would expand the time scale seven times, and ensure that this circuit would work with a 70 mS  $V_{\rm CC}$  rise time.

3.0 TESTING OF BREADBOARD

## 3.1 BREADBOARD INTEGRATION

All the boards were now inserted into the rack except for the command sequencer, and a check was carried out on every command, with first side A powered, and then side B. This process was then repeated with the command decoder in the LSP reset mode. From this test it was concluded that the method of implementation of redundancy was correct.

## 3.2 COMMAND SEQUENCER

The command sequencer board was then inserted in the rack, and its functions checked. Firstly, the ripple-off circuit was checked by generating a variable width negative pulse corresponding to the reserve power signal RESZP. This signal was out of phase with any of the other command decoder signals.

Each output was checked for correct timing (Figure 24) and to ensure that a pulse was completed (8 mS long) even if the reserve power signal had returned high during its period. A check was also made to ensure that the system inhibited itself if the input pulse finished after the last command pulse was generated. A separate command or power reset was then required to return the circuit to its active state.

|             | ALSEP Array E                             | <b>no.</b><br>ATM-985 |      |

|-------------|-------------------------------------------|-----------------------|------|

| pace        | Command Decoder<br>Breadboard Test Report | PAGE10                | . OF |

| ms Division | . · ·                                     | DATE 2/26             | /71  |

REV. NO.

39

The repeated command sequencer and uplink switch circuit was next tested with a simulated 90th frame mark and a Word Three (Figure 25). The repetition rates were speeded up to cycle in 4 minutes instead of 60 hours. This circuit was then checked at this high repetition rate, and the command OR circuit checked for both A and B sides, and also for the ripple-off commands.

#### 3.3 POWER CONSUMPTION MEASUREMENTS

vsto

The whole command decoder breadboard rack was placed in a temperature chamber, and all of the power supply currents measured at 20°C temperature intervals.

The currents taken by the 5 volt supply lines are shown in Figure 27 for nominal, high and low variations of voltage at various temperatures. Figure 28 shows the results for the + and -12 volt lines. No plots are shown for voltage variations of the 12 volt lines since the current variation was less than 100 mV at all points. The 12 volt non-redundant supply was between 40 and  $60\mu$  A on both the positive and negative lines.

## 3.4 INTEGRATION WITH DATA PROCESSOR

The final test carried out with the command decoder breadboard was that of integration with the data processor. The two units were hooked up with a 3 ft. interface cable, and both units worked well (Figure 29). This was quite a severe test for the logic to drive a 3 ft. line in a noisy environment, but no problems were experienced once a single point ground system was implemented for the power supplies and test equipment. In flight hardware, this length has been designed to be less than 10 inches.

46 07 LOCK RANGE Hz 1400 1000 400 ł., DATA DEMOD P.L.L

0

1800

CAPTURE TIME

ms

2

0

10 X 10 TO THE INCH 40 0782

åd - T 1/1 -16 сf, 0

U OGARITHMIC STREET AND OVER SH 46 7522  $(x_1, x_2, x_3, x_4)$ · • ... -KEUFFEL & ESSER CO

10 10 THE INCH 46 UPS. NEW STREET ASSER TO

F1914

# MOTOROLA RX (IOVPPCLIPPED)

. بە

PHILCO RX (21Vpp)

RECEIVER NOISE SPECTRA

(ii)

(11)

TEST SET UP FOR CLOSED LOOP FREQUENCY RE FONSE

FIG 17

# TEST SET UP FOR PSR CHARACTERISTIC

THRESHOLD ANALYSIS SET UP

BW= IOKHZ

Å.

FIG. 21

``

UPLINK

CLOCK GENERATOR

|                           |                                     | $\sum$ |              |

|---------------------------|-------------------------------------|--------|--------------|

|                           |                                     |        |              |

|                           | 120±10 mS                           |        |              |

| RESERVE<br>POWER<br>RESZP |                                     |        |              |

| СОММ AND<br>021<br>023    |                                     |        |              |

| 037<br>043                |                                     | •      |              |

| 046                       |                                     |        | AT           |

| 053                       |                                     |        | ATM-985 Page |

|                           | FIG. 24 RIPPLE - OFF COMMAND OUTPUT |        | ge 34 of 39  |

|                           |                                     |        |              |

FIG. 25

: ,5

SET

R.W.A 12-9-70

CIRCUIT

J.W.A 2-25-71

ATM-985 Page 37 of 39

g.w.A.