volume 1

Lobb

# ALSEP/SIDE/CCGE contract no. 51966-14

PRIME CONTRACT NO. NAS9-5911

TIME-ZERO corporation

Page ii

## FINAL ENGINEERING REPORT

For

### ALSEP/SIDE/CCGE

(Apollo Lunar Surface Experiments Package/ Suprathermal Ion Detector Experiment/ Cold Cathode Gauge Experiment)

> Contract No. S1966-14 Prime Contract No. NAS 9-5911

> > Prepared For

### RICE UNIVERSITY

Houston, Texas

Prepared By

## TIME-ZERO CORPORATION

(Formerly Marshall Laboratories)

Page iii

#### ENGINEERING REPORT

## ALSEP/SIDE/CCGE

CONTRACT NO. S1966-14 PRIME CONTRACT NO. NAS 9-5911

PREPARED BY: R.A. Rivas

Member of the Technical Staff

PREPARED BY: A fun Jak Sam Pollack

Program Mechanical Engineer

APPROVED BY:

William Sandstrom Program Manager

APPROVED BY:

George Mohler Vice-President Manager, Aerospace Division

#### Page iv

#### ABSTRACT

The Suprathermal Ion Detector Experiment/Cold Cathode Gauge Experiment (SIDE/CCGE) was designed and fabricated by Marshall Laboratories as an integral part of the Apollo Lunar Surface Experiments Package (ALSEP).

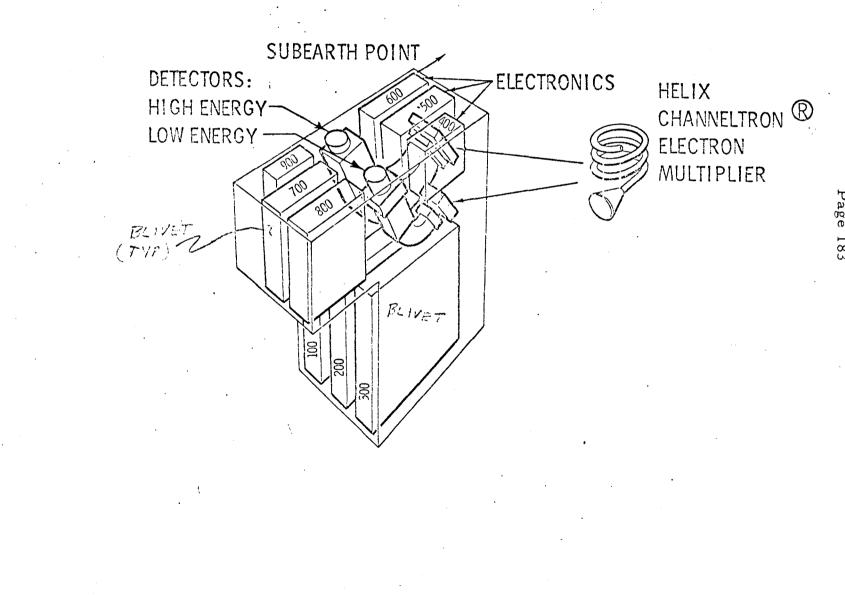

The SIDE/CCGE Experiment will measure the flux, number density, velocity and energy per unit charge of positive ions in the vicinity of the lunar surface and transfer such information to the ASLEP Data Subsystem. A Low Energy (LE) detection system, consisting of a Wein Velocity selector (crossed electric and magnetic fields), an electrostatic analyzer, and a Channeltron (R) Electron Multiplier, detects positive ions with masses up to 130 AMU, and measures the differential energy spectrum of ions in a narrow velocity range having energies from 0.2 ev to 48.6 ev per unit charge. A High Energy (HE) detection system, consisting of an electrostatic analyzer and a Channeltron (R) Electron Multiplier, detects all positive ions regardless of mass, and measures the differential energy spectrum of ions having energies from 10 ev to 3500 ev per unit charge. The ions passing through the electrostatic analyzers of each detection system are focused on their respective Channeltron (R) Electron Multiplier (2 per SIDE), whose output is amplified by their Detector Amplifiers (2 per SIDE). A data accumulator (0 to 10<sup>°</sup> counts per sample interval) stores the amplified channeltron output pulses during each accumulation interval. Parallel data paths direct to the ALSEP Analog-to-Digital (A/D) converters are provided for the High Energy and Low Energy detection systems. Outputs of the converters consist of eight bits of digital information, which are commutated into one output. Housekeeping data is also monitored by the SIDE A/D Converters. A Master Timing Generator controls all timing functions as follows: (1) provides an address for each frame in a cycle (SIDE FRAME count), (2) provides sequencing information for the electrostatic analyzer stepping voltages, velocity selector voltages, and Ground Plane Screen voltages, and (3) provides sequencing and timing signals for various portions of the experiment. The Ground Plane Screen furnishes a stepped reference potential on the lunar surface for the entire experiment. A Command System consisting of five command lines furnishes any of 16 command input combinations.

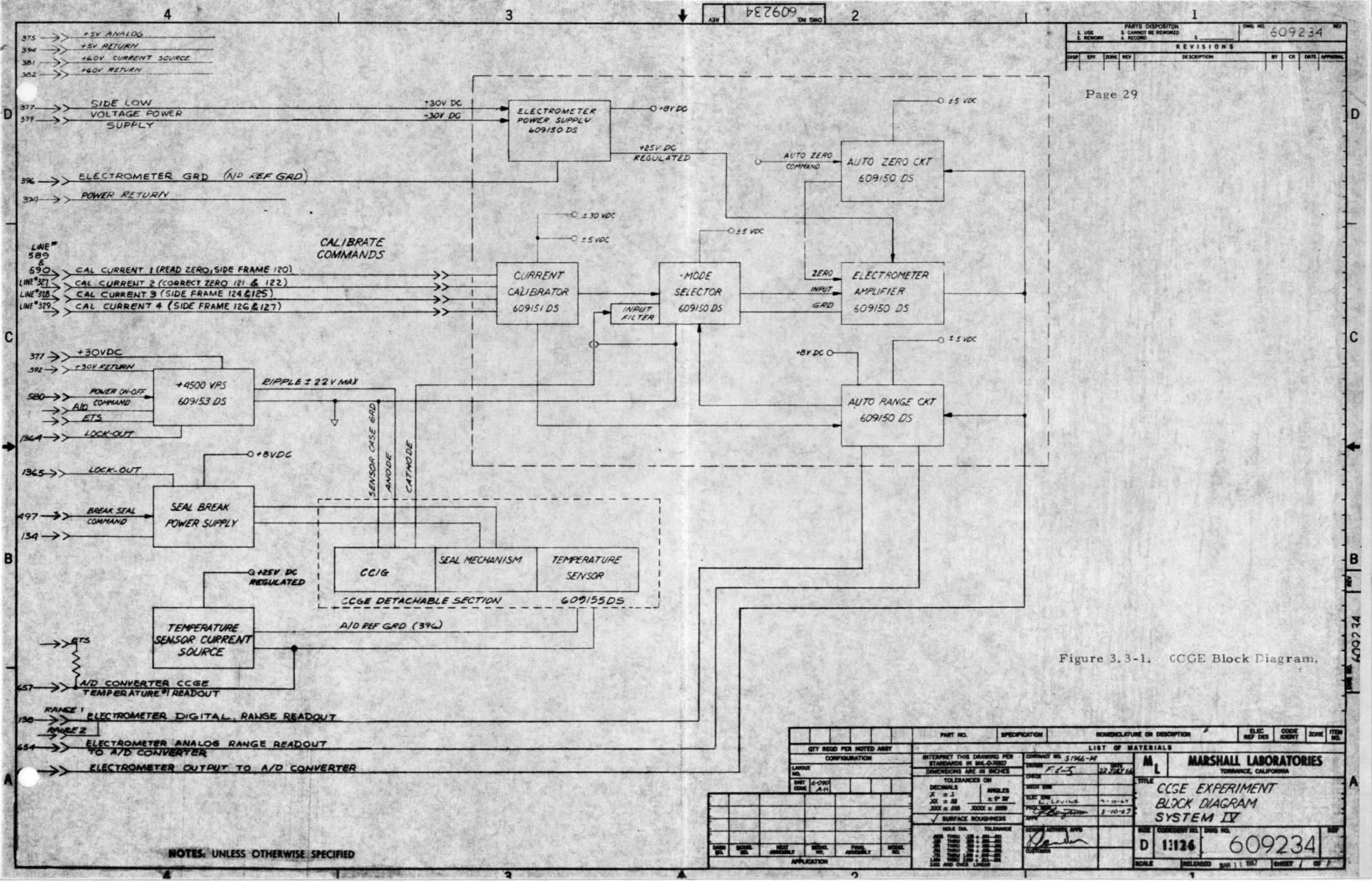

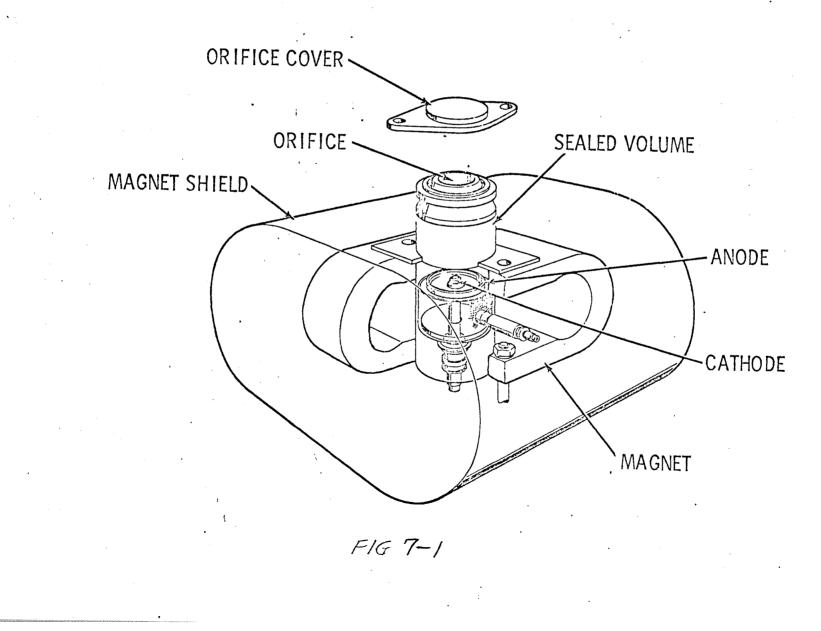

The CCGE experiment will determine (1) the density of any lunar ambient atmosphere corresponding to pressures of  $10^{-6}$  torr to approximately  $10^{-12}$  torr, including any temporal variations either of a random character or associated with lunar local time or solar

#### Page v

activity, and (2) the rate of loss of contaminants left in the landing area by the astronauts and the Lunar Module. The sensor is a plasma discharge device which effects conversion of density to direct current. An Auto Ranging, Auto Zero electrometer monitors currents in the  $10^{-14}$  to  $10^{-6}$  amperes range, and the data is processed by the A/D converters in the SIDE. The gauge produces a magnetic field of 1020 gauss, and operates at an anode voltage of 4500 volts. A Seal Mechanism provides protection against premature contamination of the sensor, and is released when the proper command is executed from the ground station.

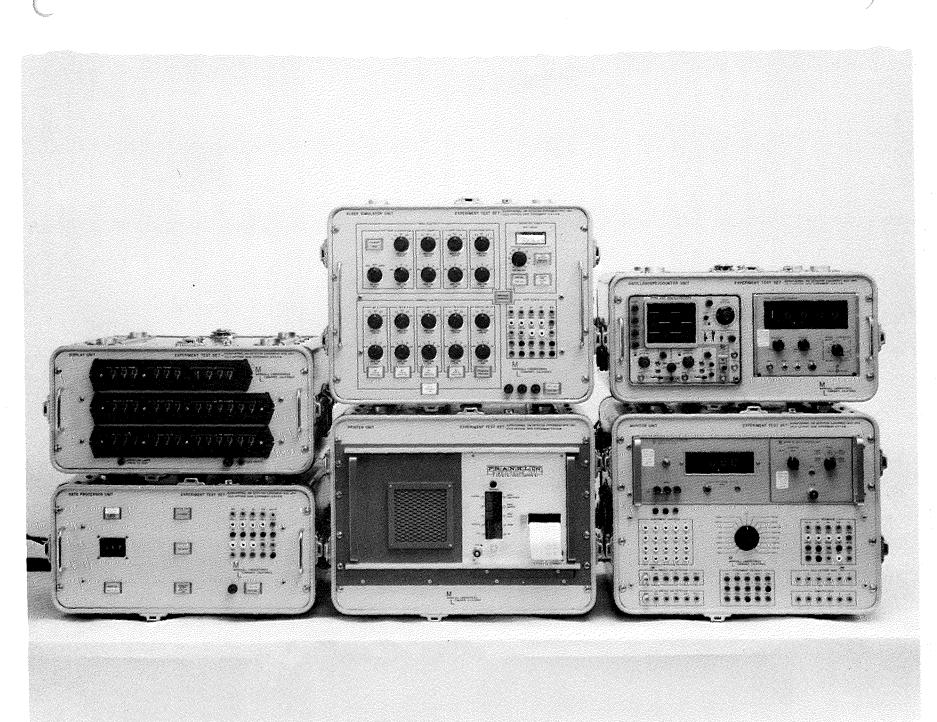

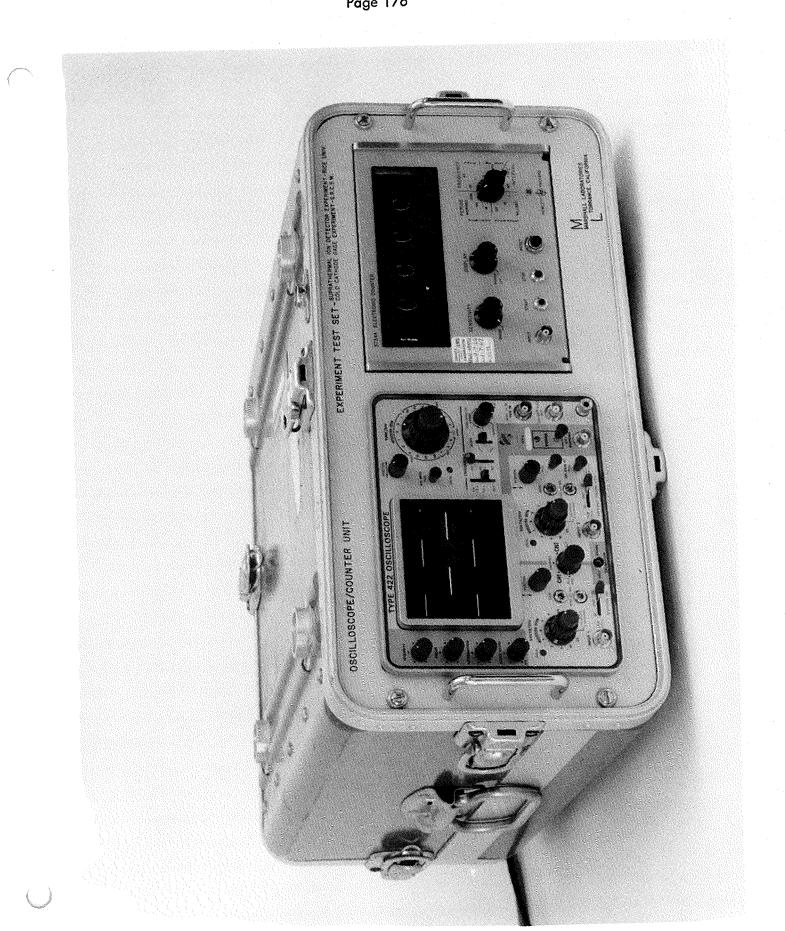

Special equipment requirements include an Experiment Test Set (ETS) to completely check out the entire experiment package. The ETS consists of the following major subassemblies: (1) Data Processor, Printer Unit, Data Phone Unit; (2) Display Unit; (3) ALSEP Simulator Unit; (4) Monitor Unit; and (5) Oscilloscope/ Counter Unit. The function of the ETS is to process data from the SIDE/CCGE, display it in decimal form, print out the data or transmit it through the dataphone, provide timing and command signals to simulate the function of ALSEP, and supply power to the SIDE/ CCGE.

## Page vi

## TABLE OF CONTENTS

|     |               |                               | Page |

|-----|---------------|-------------------------------|------|

| 1.0 | INTRODUC      | CTION                         | 1    |

| 2.0 | PROGRAM       | I HISTORY                     | 12   |

| 3.0 | EXPERIM       | ENT DESCRIPTION               | 19   |

|     | 3.1           | Low Energy Detection System   | 25   |

|     | 3.2           | High Energy Detection System  | 26   |

|     | 3.3           | Cold Cathode Gauge Experiment | 28   |

|     | 3.4           | Support Electronics           | 28   |

| 1   | <b>3.4.</b> 1 | Power                         | 28   |

|     | 3.4.2         | Logic Timing; Command System  | 30   |

|     | 3.4.3         | Dust Cover and Seal           | 36   |

|     | 3.4.4         | Analog-to-Digital Conversion  | 36   |

|     | 3.4.5         | Temperature Sensors; Heaters  | 37   |

|     | 3.4.6         | Ground Plane Generator        | 37   |

| 4.0 | ALSEP INT     | TERFACES                      | 39   |

|     | 4.1           | Mechanical Interfaces         | 39   |

|     | 4.2           | Electrical Interfaces         | 39   |

|     | 4.2.1         | Primary Power Interface       | 39   |

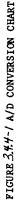

|     | 4.2.2         | Signal Interfaces             | 39   |

|     | 4.2.2.1       | Input Isolation Amplifiers    | 39   |

|     | 4.2.2.2       | Output Isolation Amplifier    | 41   |

|     |          | Page vii                                           | Page |

|-----|----------|----------------------------------------------------|------|

| 5.0 | SYSTEM 1 | DESCRIPTION                                        | 42   |

|     | 5.1      | Logic and Support Electronics                      | 42   |

|     | 5.1.1    | Low Voltage Power Supply                           | 42   |

|     | 5.1.2    | Temperature Monitors                               | 45   |

|     | 5.1.3    | Command System                                     | 45   |

|     | 5.1.4    | SIDE Frame Counter                                 | 50   |

|     | 5.1.5    | Status Subcommutator                               | 52   |

|     | 5.1.6    | Shift Pulse and Word Generator                     | 53   |

|     | 5.1.7    | Logic Timing and Strobe Gates;<br>Power on Detect  | 55   |

|     | 5.1.7.1  | X10 Mode                                           | 55   |

|     | 5.1.7.2  | Synchronizing Pulses                               | 58   |

|     | 5.1.7.3  | Word NOR Gates; Start A/D Pulse                    | 58   |

|     | 5.1.7.4  | Power On Detect                                    | 58   |

|     | 5.1.7.5  | Command Gates                                      | 60   |

|     | 5.1.7.6  | Reset High Energy Counter Pulse                    | 60   |

|     | 5.1.7.7  | High Energy Accumulator Logic<br>Timing            | 60   |

|     | 5.1.7.8  | Low Energy Accumulator Logic<br>Timing             | 61   |

|     | 5.1.7.9  | Converter and Stepper Voltages<br>ON/OFF Controls. | 61   |

|     | 5.1.7.10 | Strobe Gates                                       | 62   |

|     | 5.1.8    | Parity Generator                                   | 62   |

». ۲

,

## Page viii

|         | rage vill                                                 | Page |

|---------|-----------------------------------------------------------|------|

| 5.1.9   | Analog-to-Digital Converters;<br>A/D Subcommutator        | 62   |

| 5.1.10  | Heater Control Circuit                                    | 68   |

| 5.1.11  | Dust Cover Circuit; Solar Cell                            | 68   |

| 5.1.12  | Voltage Dividers                                          | 71   |

| 5.1.13  | One Time Command Status;<br>Break Seal-Dust Cover Monitor | 71   |

| 5.2     | Low Energy Ion Detector                                   | 77   |

| 5.2.1   | Calibration Pulser; Calibration<br>Rate Counter           | 77   |

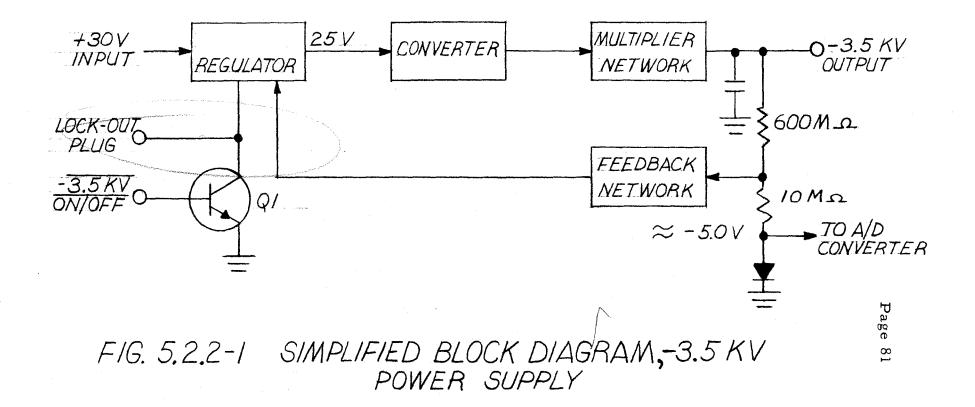

| 5.2.2   | -3.5kV Power Supply                                       | 80   |

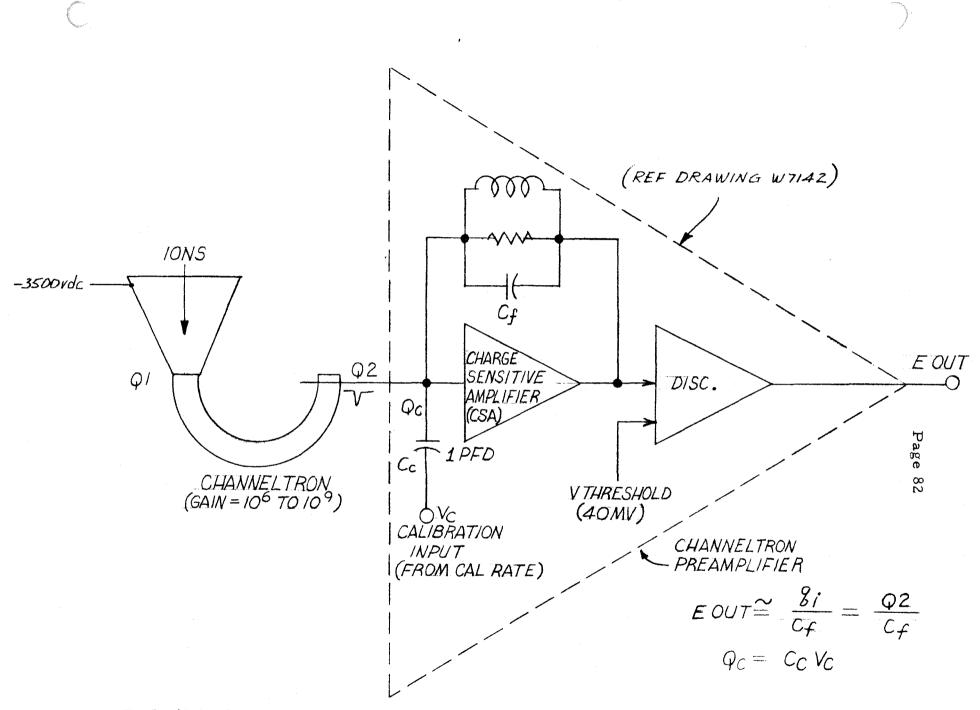

| 5.2.3   | Channeltron Preamplifier                                  | 80   |

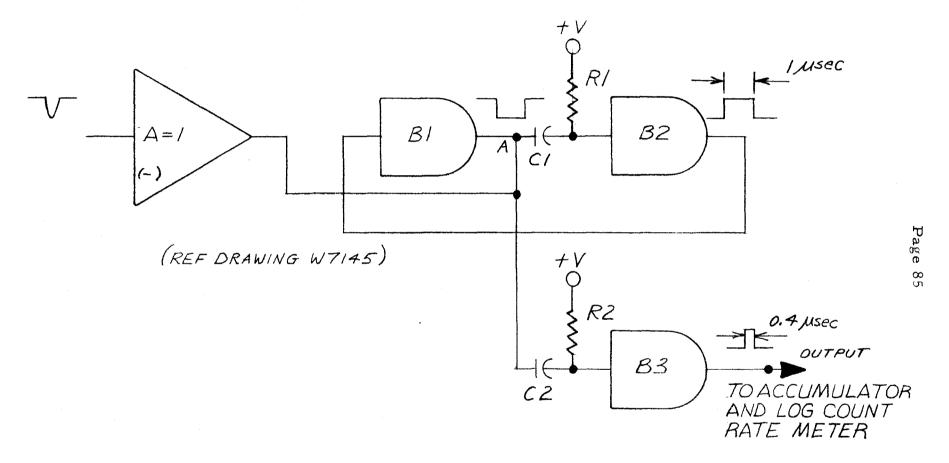

| 5.2.4   | Deadtime Circuit                                          | 83   |

| 5.2.5   | Log Count Rate Meter                                      | 86   |

| 5.2.6   | Low Energy Accumulator                                    | 88   |

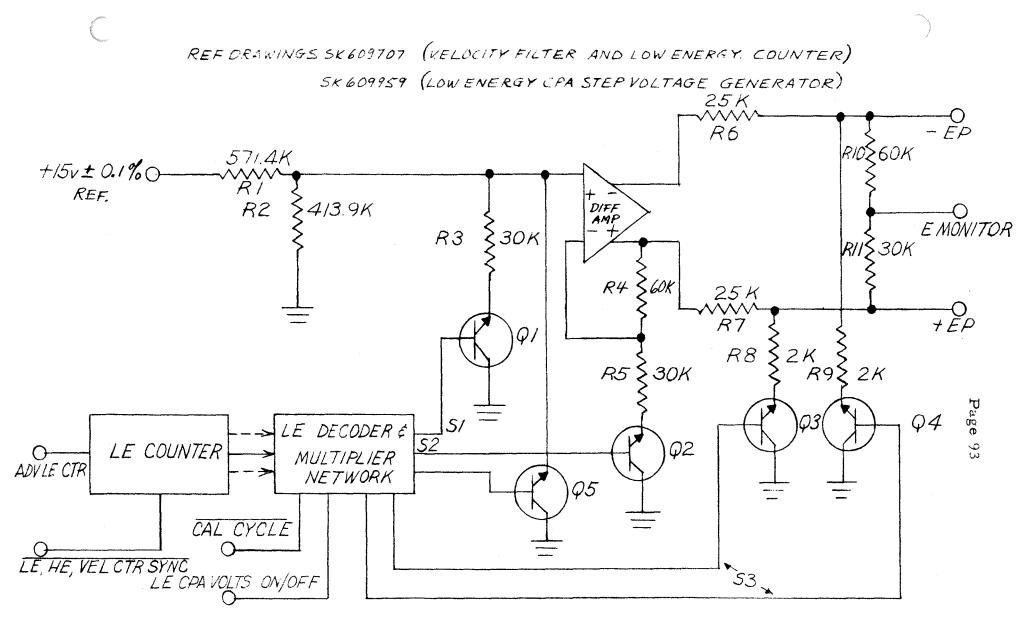

| 5.2.7   | Low Energy Step Voltage Generator                         | 92   |

| 5.2.7.1 | Low Energy Counter                                        | 95   |

| 5.2.7.2 | Low Energy Decoder and Multiplier<br>Network              | 95   |

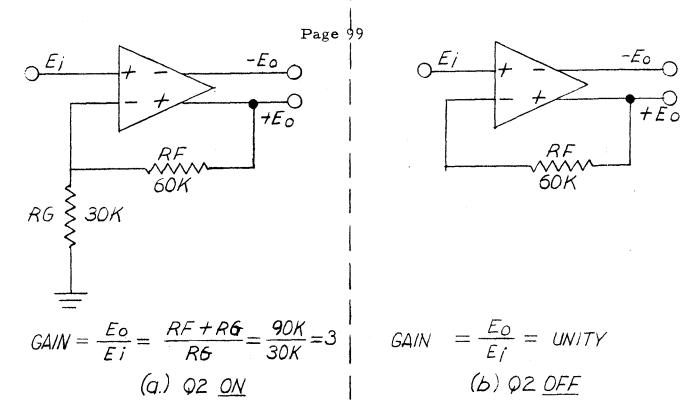

| 5.2.7.3 | Low Energy Amplifier                                      | 98   |

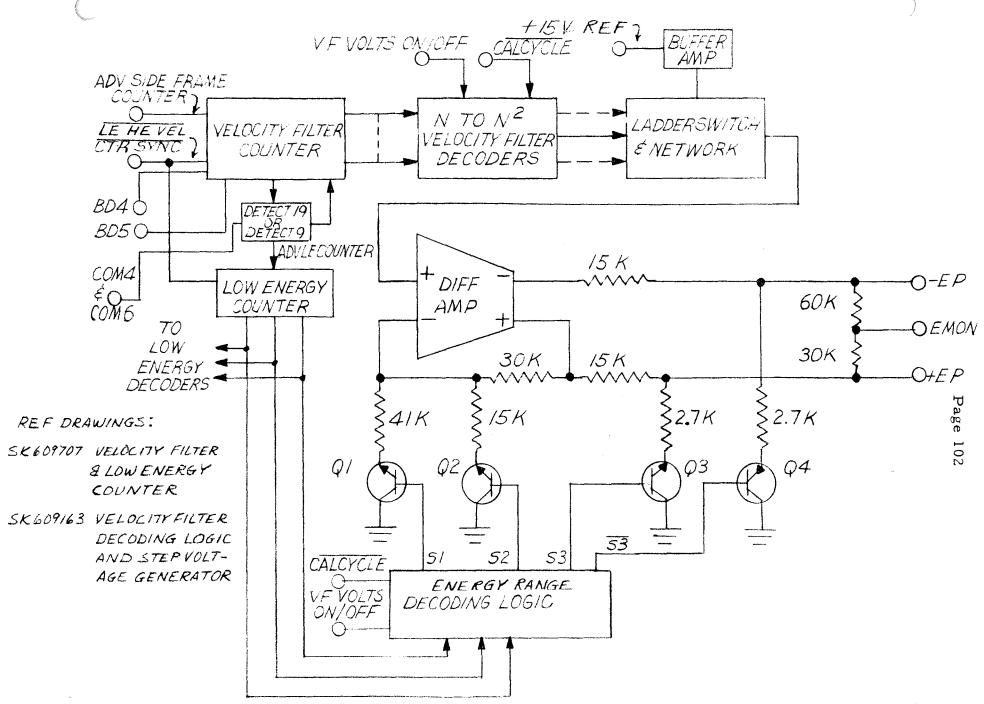

| 5.2.8   | Velocity Filter Step Voltage<br>Generator                 | 101  |

| 5.2.8.1 | Velocity Filter Counter                                   | 101  |

| 5.2.8.2 | Velocity Filter Decoders; Ladder<br>Switch and Network    | 106  |

-

|         | Page ix                                        | Page |

|---------|------------------------------------------------|------|

| 5.2.8.3 | Velocity Filter Amplifier                      | 112  |

| 5.3     | High Energy Ion Detector                       | 115  |

| 5.3.1   | Calibration Pulse; Calibration<br>Rate Counter | 115  |

| 5.3.2   | -3.5kV Power Supply                            | 115  |

| 5.3.3   | Channeltron Preamplifier                       | 115  |

| 5.3.4   | Deadtime Circuit                               | 115  |

| 5.3.5   | Log Count Rate Meter                           | 115  |

| 5.3.6   | High Energy Accumulator                        | 115  |

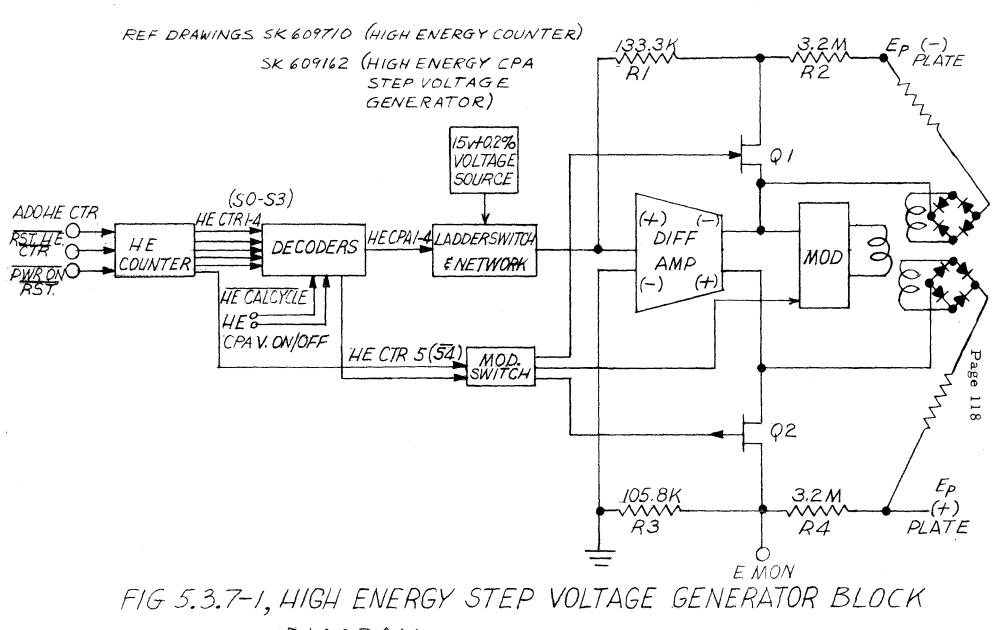

| 5,3.7   | High Energy Step Voltage Generator             | 117  |

| 5.3.7.1 | High Energy Counter                            | 119  |

| 5.3.7.2 | High Energy Decoder                            | 125  |

| 5.3.7.3 | Ladder Switch and Network                      | 125  |

| 5.3.7.4 | Modulator Switch                               | 125  |

| 5.3.7.5 | High Energy Amplifier                          | 128  |

| 5.4     | Cold Cathode Gauge Experiment                  | 130  |

| 5.4.1   | Electrometer                                   | 130  |

| 5.4.2   | Sensor                                         | 141  |

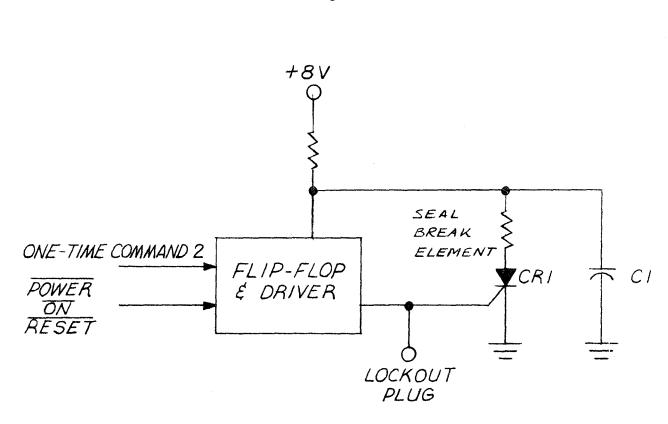

| 5.4.3   | Seal Mechanism Power Supply                    | 141  |

| 5.4.4   | Seal Mechanism                                 | 143  |

| 5.4.5   | 4500 Volt Power Supply                         | 143  |

| 5.4.6   | Temperature Sensor and Monitoring<br>Circuit   | 145  |

-

| Ρ | а | g | е | $\mathbf{x}$ |

|---|---|---|---|--------------|

|   |   |   |   |              |

|     |          |                                                              | Page      |

|-----|----------|--------------------------------------------------------------|-----------|

|     | 5.5      | Ground Plane                                                 | 145       |

|     | 5.5.1    | Ground Plane Step Voltage<br>Generator                       | 145       |

|     | 5.5.1.1  | Ground Plane Counter                                         | 145       |

|     | 5.5.1.2  | Ground Plane Decoders; Ladder<br>Switch and Network          | 148       |

|     | 5.5.1.3  | Ground Plane Amplifier                                       | 148       |

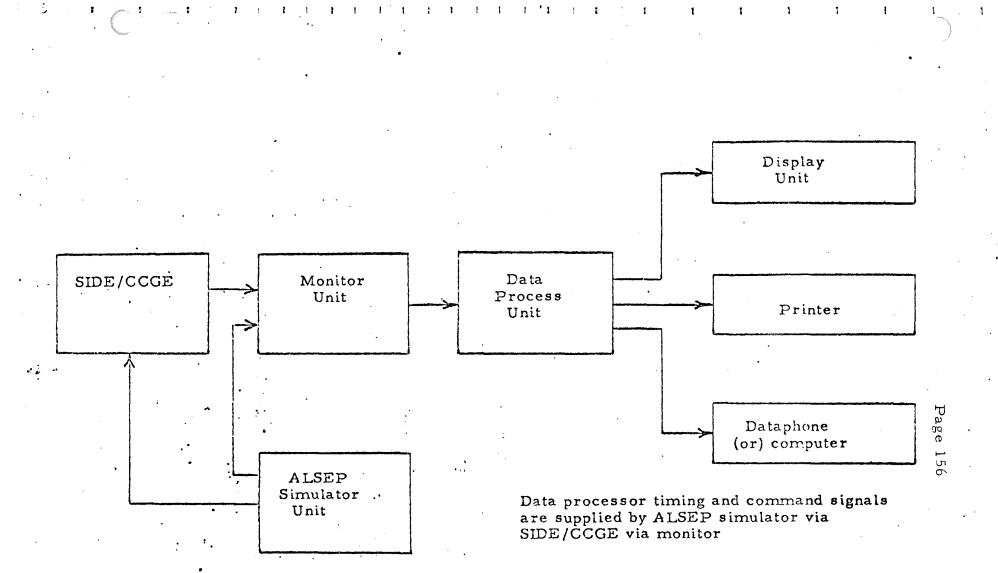

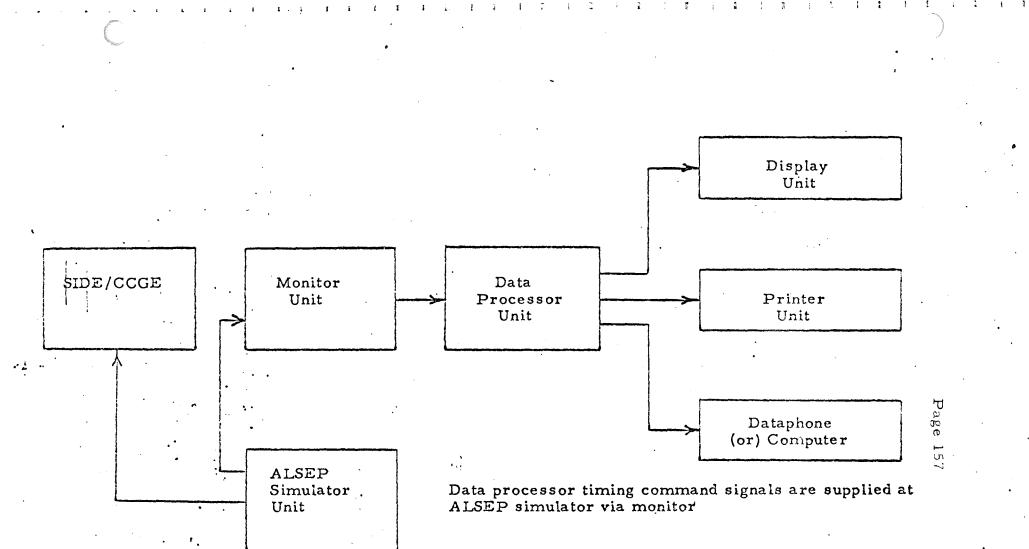

| 6.0 | EXPERIME | ENT TEST SET                                                 | 155       |

|     | 6.1      | Display Unit                                                 | 155       |

|     | 6.2      | Data Processor Unit                                          | 163       |

|     | 6.3      | ALSEP Simulator Unit                                         | 169       |

|     | 6.4      | Monitor Unit                                                 | 172       |

|     | 6.5      | Printer Unit                                                 | 174       |

|     | 6.6      | Oscilloscope/Counter Unit                                    | 174       |

| 7.0 | MECHANIC | CAL AND THERMAL DESIGN                                       | 177       |

|     | 7.1      | Basic Mechanical Design Configuration                        | 177       |

|     | 7.1.1    | ALSEP/SIDE Deployment on Lunar<br>Surface                    | 177       |

|     | 7.1.2    | CCIG (Cold Cathode Ion Guage)<br>Deployment                  | 180       |

|     | 7.1.3    | Operation of Dust Cover and Solenoid<br>Mechanism            | 180       |

|     | 7.1.4    | Deployment of ALSEP/SIDE Interconnectin<br>Flat Ribbon Cable | ng<br>180 |

## Page xi

|        |                                                                         | Page |

|--------|-------------------------------------------------------------------------|------|

| 7.1.5  | Packaging Design, Inner and Outer<br>Assemblies                         | 182  |

| 7.1.6  | ALSEP/SIDE Collapsible Leg<br>Design and Deployment                     | 182  |

| 7.1.7  | Sine and Random Vibration Tests                                         | 184  |

| 7.1.8  | Ground Screen Design and<br>Deployment                                  | 184  |

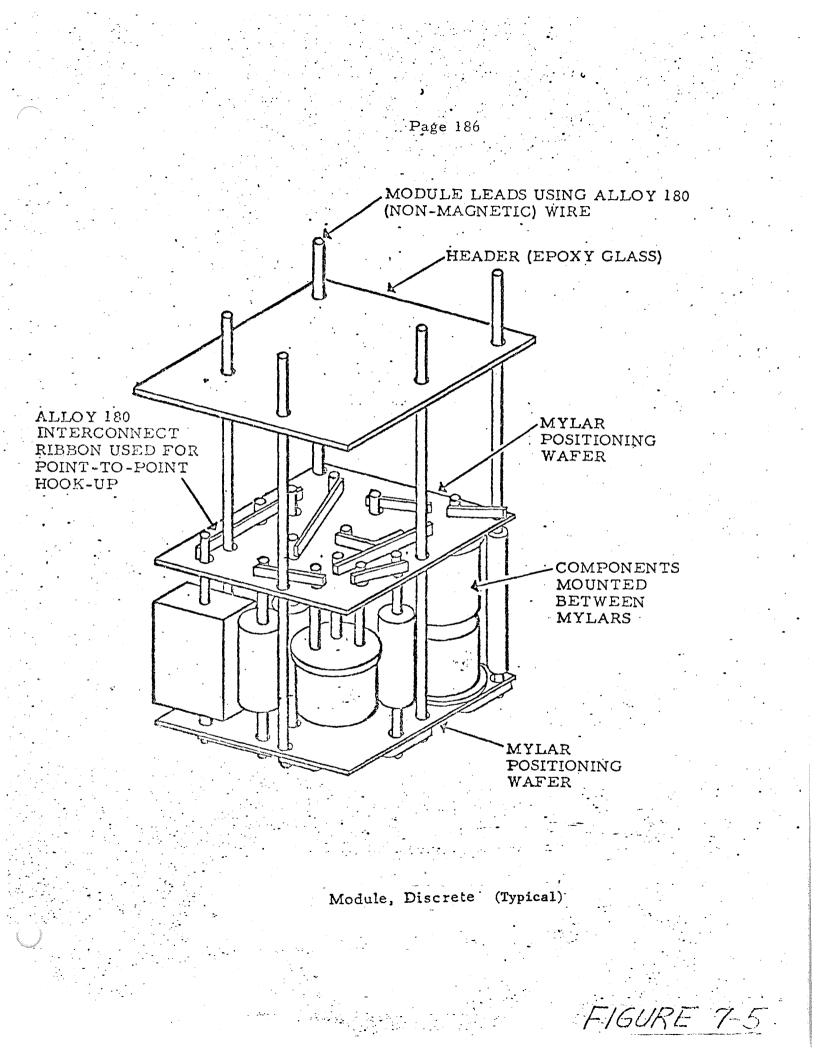

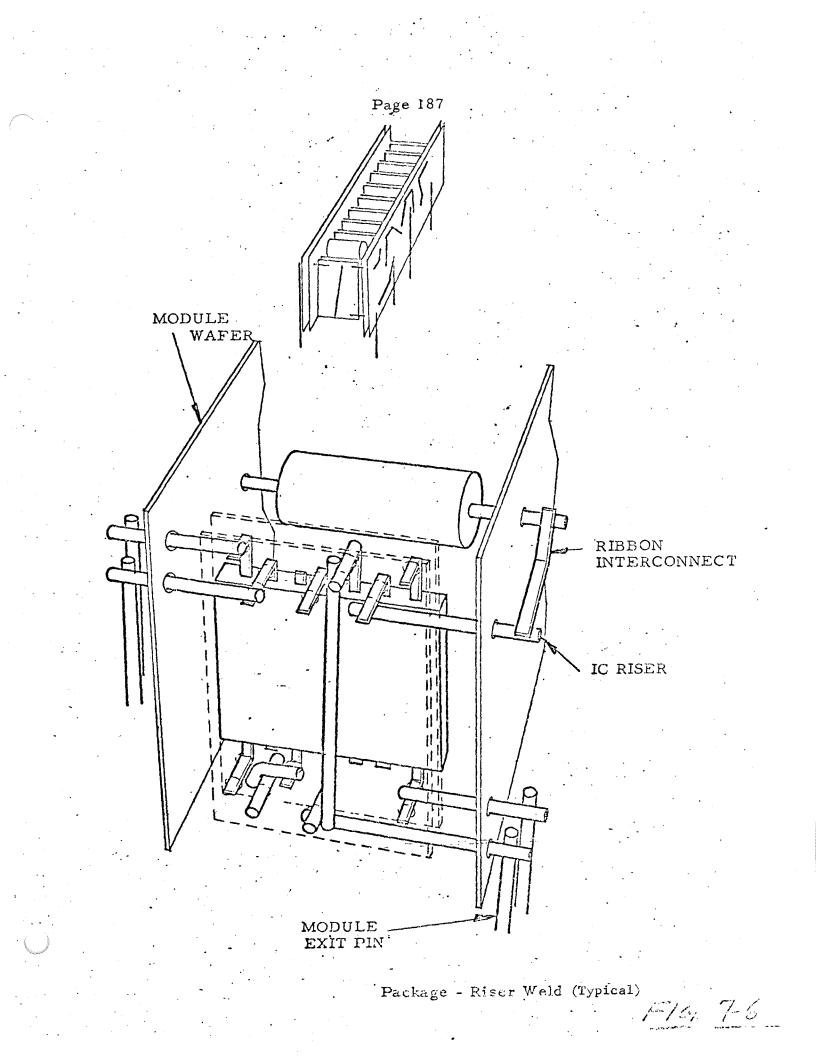

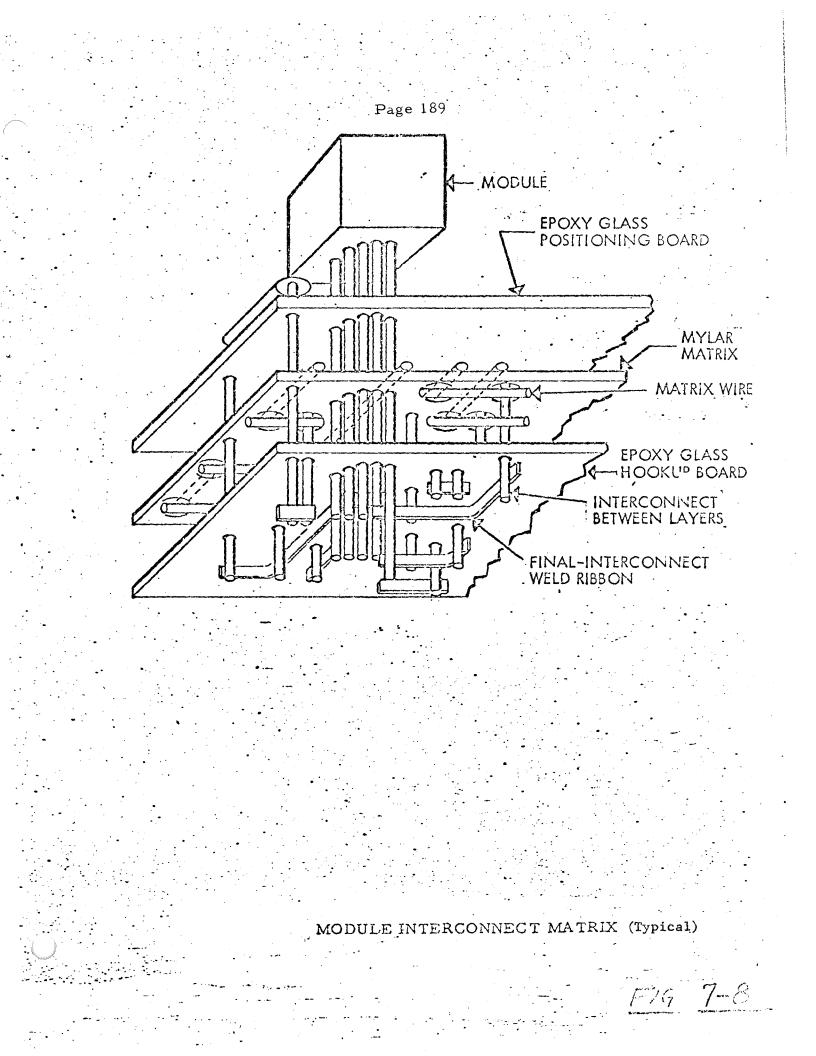

| 7.1.9  | Electronic Packaging Welded<br>Module and Blivet Assembly               | 184  |

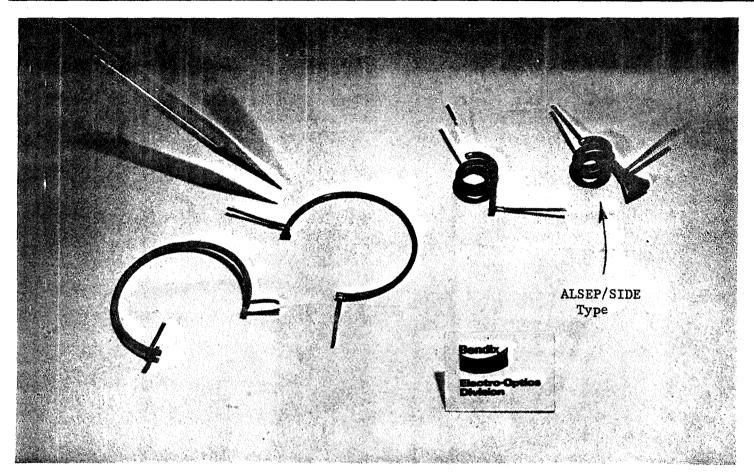

| 7.1.10 | Channeltron Mechanical Con-<br>figuration (High and Low Energy)         | 190  |

| 7.1.11 | ALSEP/SIDE/CCGE Qualifications<br>Vibration                             | 190  |

| 7.1.12 | Special Studies and Calculations                                        | 190  |

| 7.1.13 | ALSEP/SIDE/CCGE Material<br>List and Miscellaneous Vendor<br>Literature | 193  |

| 7.1.14 | ALSEP/SIDE/CCGE Assembly<br>Plans                                       | 193  |

| 7.1.15 | Master Drawing List                                                     | 193  |

| 7.1.16 | Interface and Top Assembly Drawings                                     | 193  |

| 7.1.17 | Special Tools and Fixtures                                              | 194  |

| 7.1.8  | Cleaning Materials                                                      | 194  |

| 7.2    | Thermal Design                                                          | 195  |

| 7.2.1  | Thermal Simulator                                                       | 195  |

| 7.2.2  | ALSEP/SIDE/CCGE Thermal Design<br>Features                              | 195  |

۲

#### Page xii

|      |            |                                                   | Page |

|------|------------|---------------------------------------------------|------|

|      | 7.2.3      | Summary of Thermal Studies and<br>Tests Performed | 201  |

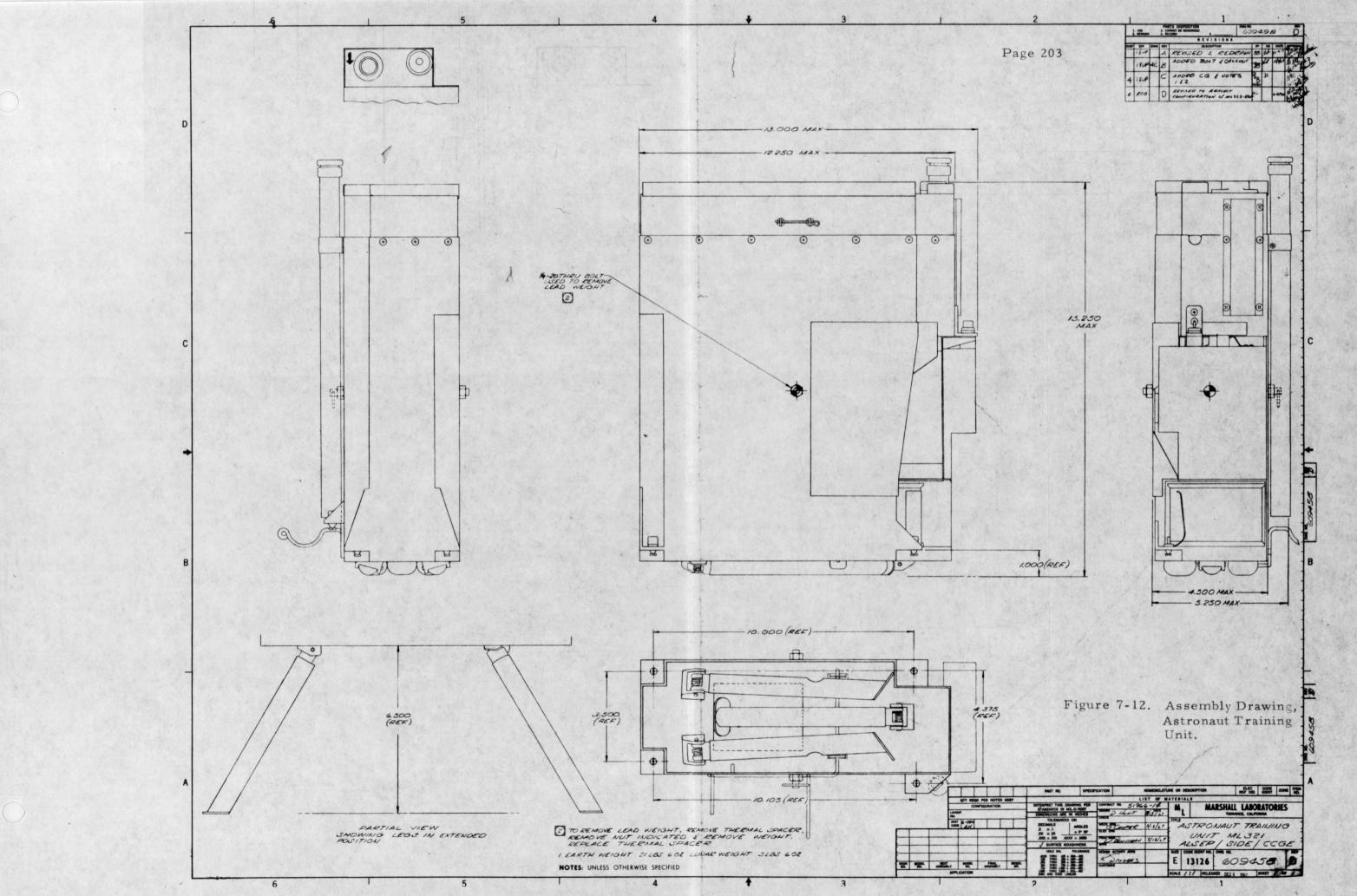

|      | 7.3        | Astronaut Training Unit                           | 201  |

| 8.0  | NEW TEC    | HNOLOGY                                           | 204  |

| APPE | NDICES - E | lectrical                                         |      |

| I    | Data Sheet | s - Applicable Fairchild IC's                     |      |

II Master Drawing List

Ι

- Test Procedure (SIDE/CCGE Test Procedure and III Typical Test Data Results (System 7, ML 323-5)

- IV Low Energy Step Voltage Generator Error Analysis

- V Velocity Filter Step Voltage Generator Error Analysis

- VI High Energy Step Voltage Generator Error Analysis

- VII Ground Plane Step Voltage Generator Error Analysis

- VIII ETS Master Drawing List

### APPENDICES - Mechanical

- А Typical Sine and Random Vibration Test Reports and Requirements

- В Thermal Control

C Drawings:

Assembly, Ground Screen Interface Control Drawing Assembly, Blivet 100 Positioning/Hookup Board, Blivet 100 Matrix Assembly No. 1, Blivet 100

- D Ground Screen Deployment Procedures; ALSEP/SIDE/CCGE Special Handling Instructions; CCIG Lanyard and Cable Stowing Procedure

- E Typical Assembly Plan; Chassis Assembly

- F Special Studies and Calculations

- G Assembly Drawings, High and Low Energy Alignment Fixtures

## Page xiv FIGURES AND ILLUSTRATIONS

| Figure  | Title                                              | Page       |

|---------|----------------------------------------------------|------------|

| 1.0-1   | Lunar Surface Deployment                           | 2          |

| 1.0-2   | SIDE/CCGE Deployed Configuration                   | 3          |

| 1.0-3   | ALSEP System Objectives                            | . 4        |

| 1.0-4   | SIDE/CCGE Objectives Summary                       | 5          |

| 1.0-5   | Stowed Configuration                               | 6          |

| 1.0-6   | Deployment for ALSEP                               | 7          |

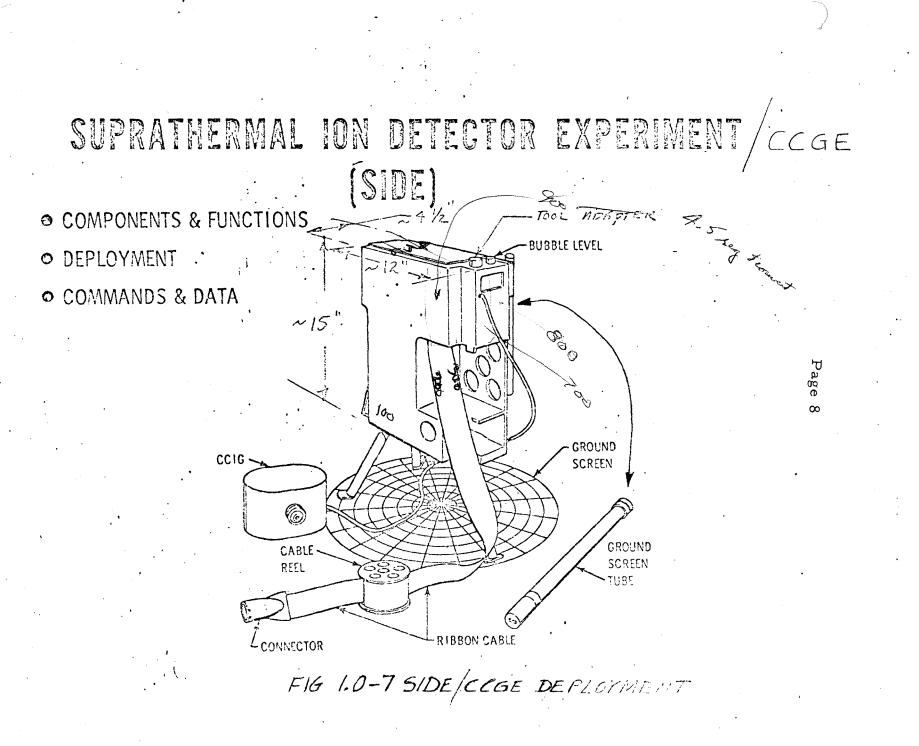

| 1.0-7   | SIDE/CCGE Deployment                               | 8          |

| 1.0-8   | ALSEP Experiment Objectives                        | 9          |

| 1.0-9   | ALSEP Experiments                                  | 10         |

| 1.0-10  | SIDE General Features                              | 11         |

| 3.0-1   | Simplified Block Diagram, SIDE/<br>CCGE Experiment | 21         |

| 3.0-2   | SIDE/CCGE Operational Diagram                      | 22         |

| 3.0-3   | A/D and Status Subcom Sequence                     | 23         |

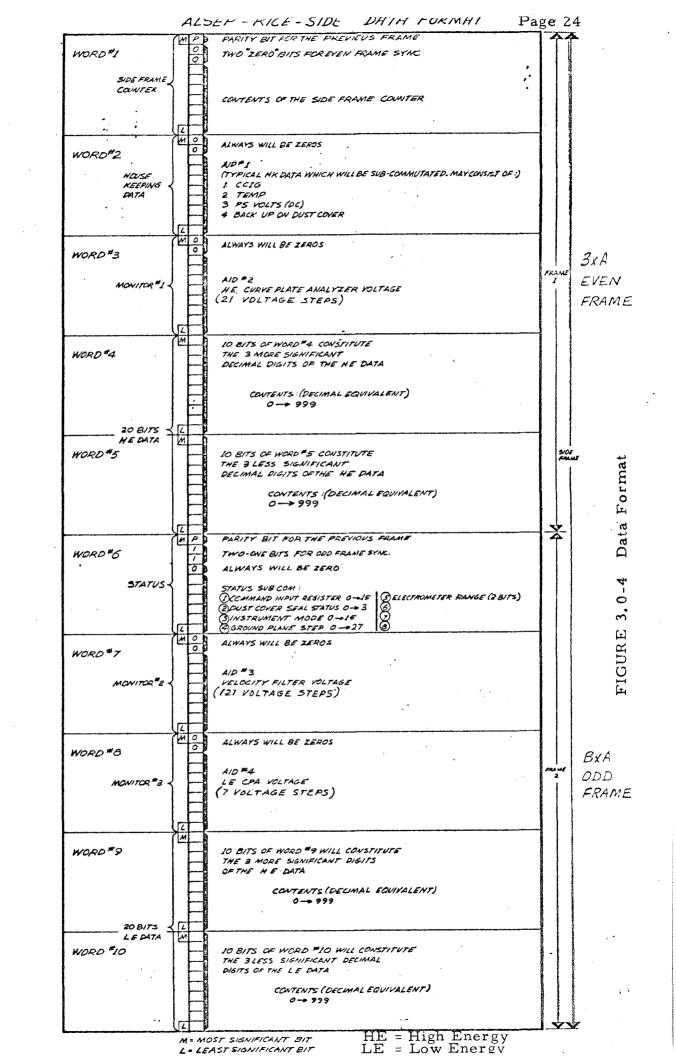

| 3.0-4   | Data Format                                        | 2 <b>4</b> |

| 3.3-1   | CCGE Block Diagram                                 | 29         |

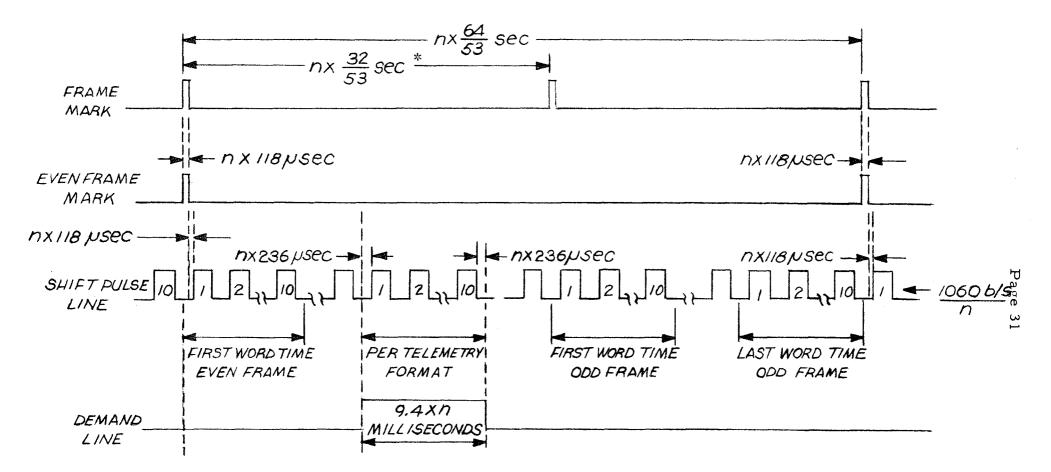

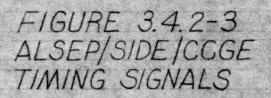

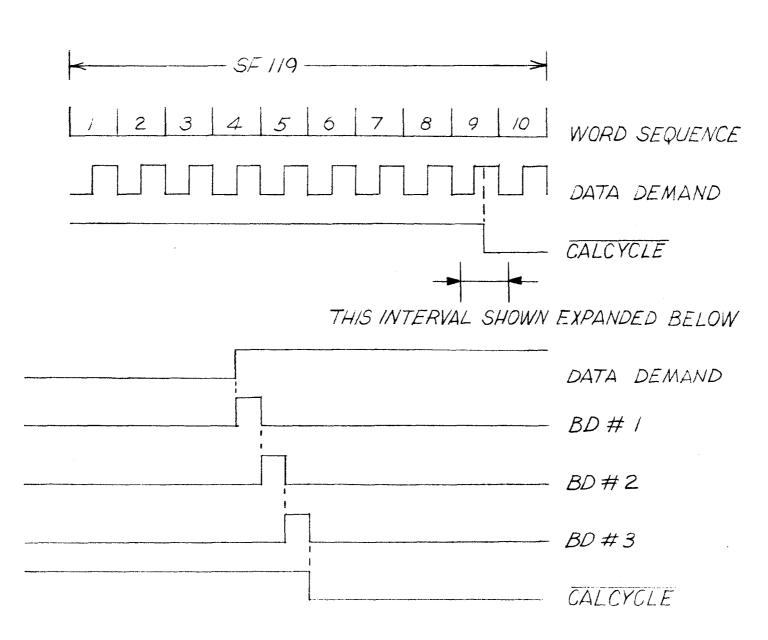

| 3.4.2-1 | ALSEP Timing Signals                               | 31         |

| 3.4.2-2 | ALSEP/SIDE/CCGE Timing Signals                     | 32         |

| 3.4.2-3 | ALSEP/SIDE/CCGE Timing Signals                     | 33         |

| 3.4.2-4 | ALSEP/SIDE/CCGE Timing Signals                     | 34         |

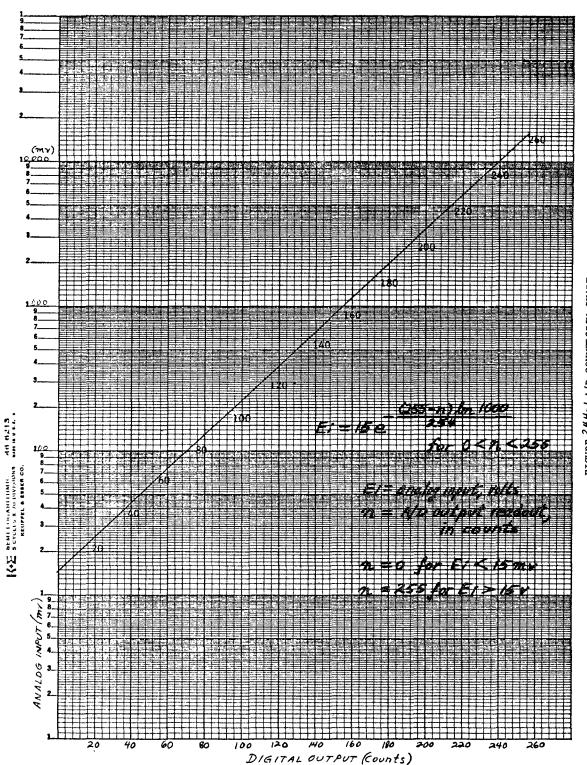

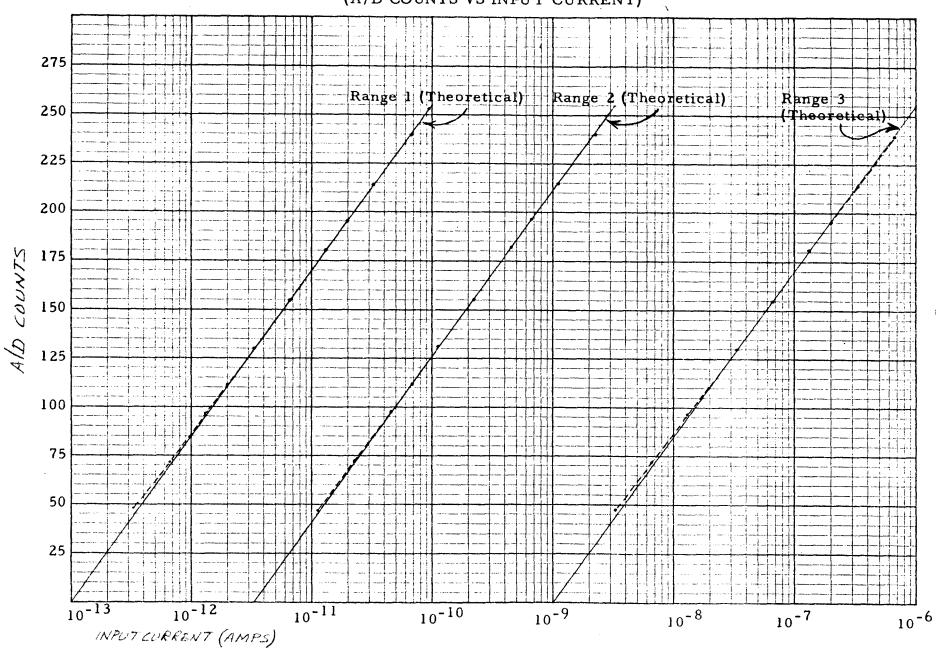

| 3.4.4-1 | A/D Conversion Chart                               | 38         |

Page xv

| Figure   | Title                                                   | Page       |

|----------|---------------------------------------------------------|------------|

| 4.2.2-1  | Signal Interfaces                                       | 40         |

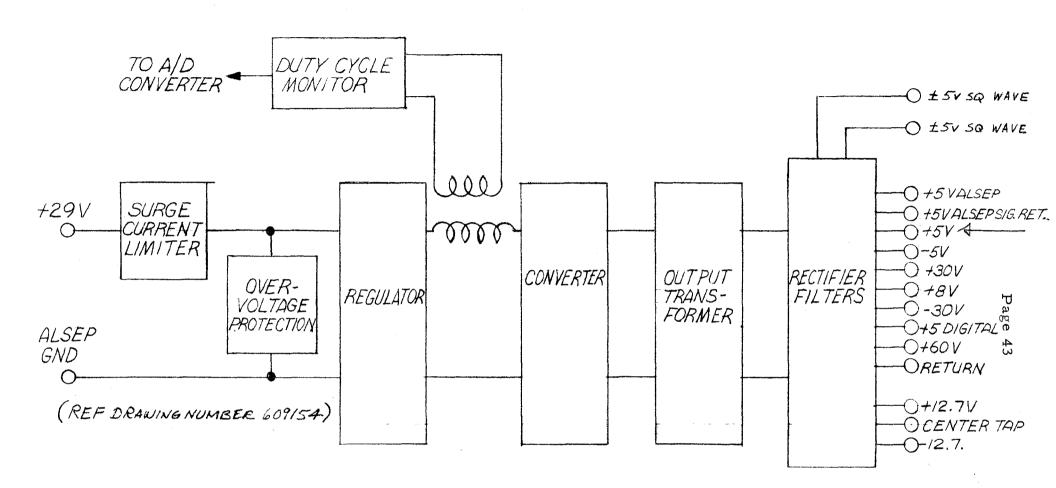

| 5.1.1-1  | Low Voltage Power Supply, Block<br>Diagram              | 43         |

| 5.1.1-2  | Duty Cycle Monitor Voltage                              | 44         |

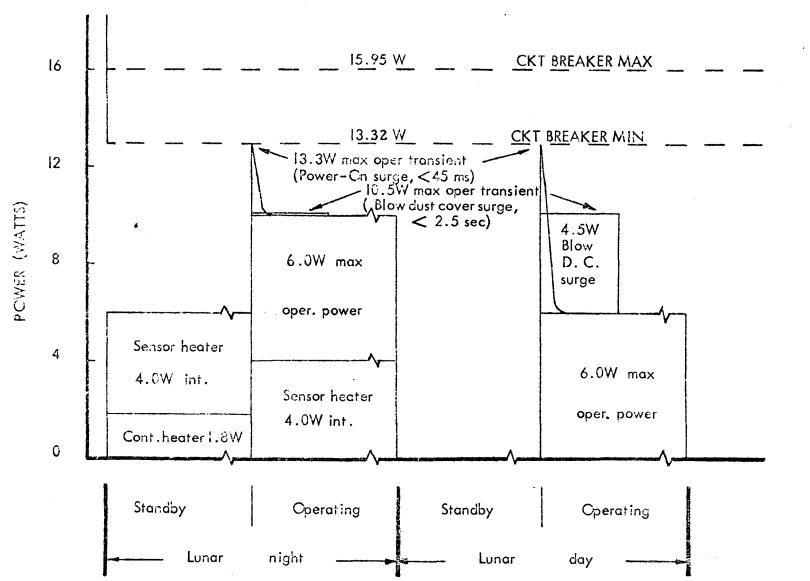

| 5.1.1-3  | SIDE/CCGE Power Profile                                 | <b>4</b> 6 |

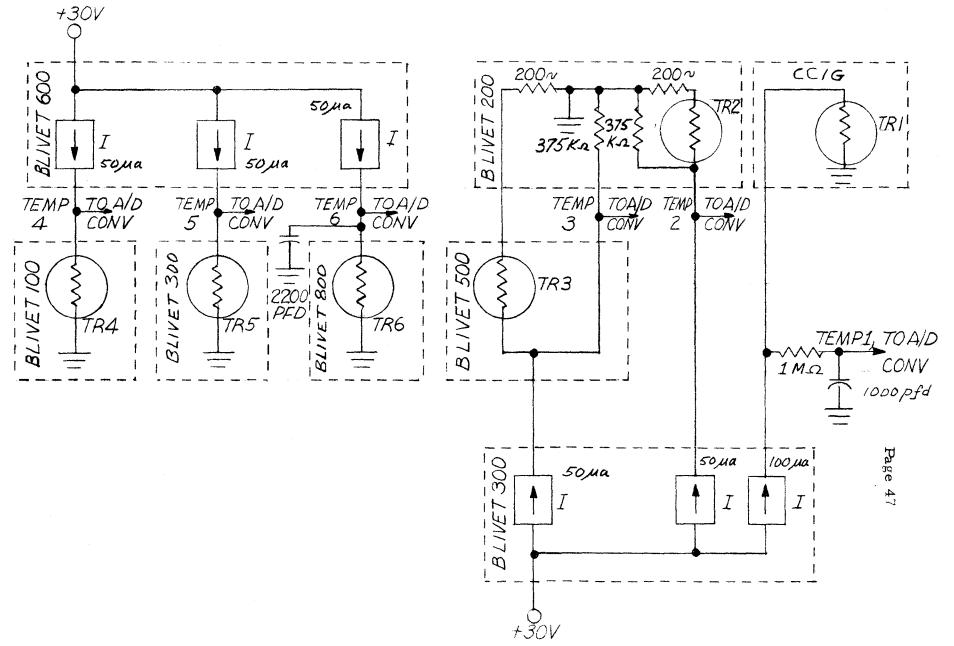

| 5.1.2-1  | Temperature Sensors, Block Diagram                      | 47         |

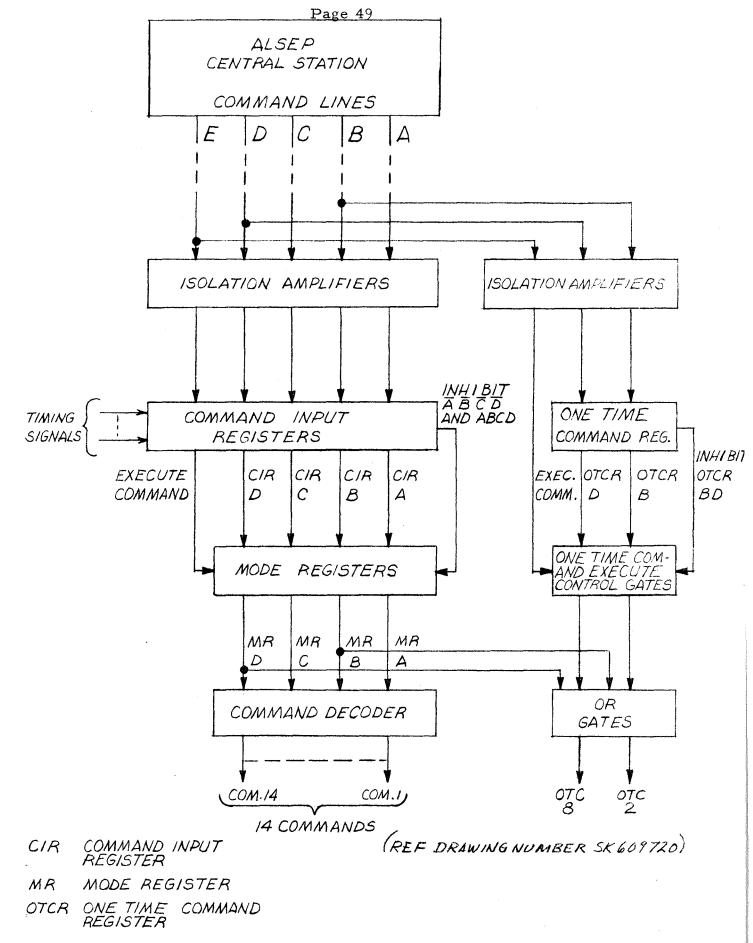

| 5.1.3-1  | Command System, Block Diagram                           | 49         |

| 5.1.4-1  | SIDE Frame Counter, Block Diagram                       | 51         |

| 5.1.6-1  | Shift Pulse and Word Generator, Block<br>Diagram        | 5 <b>4</b> |

| 5.1.6-2  | Shift Pulse and Word Generator, Timing<br>Diagram       | 56         |

| 5.1.7-1  | X10 Mode Logic, Simplified Block Diagram                | 57         |

| 5.1.7-4  | Power On Detect Circuit                                 | 59         |

| 5.1.7-5  | Strobe Gates, Block Diagram                             | 63         |

| 5.1.9-1  | Analog-to-Digital Converter, Block Diagram              | 64         |

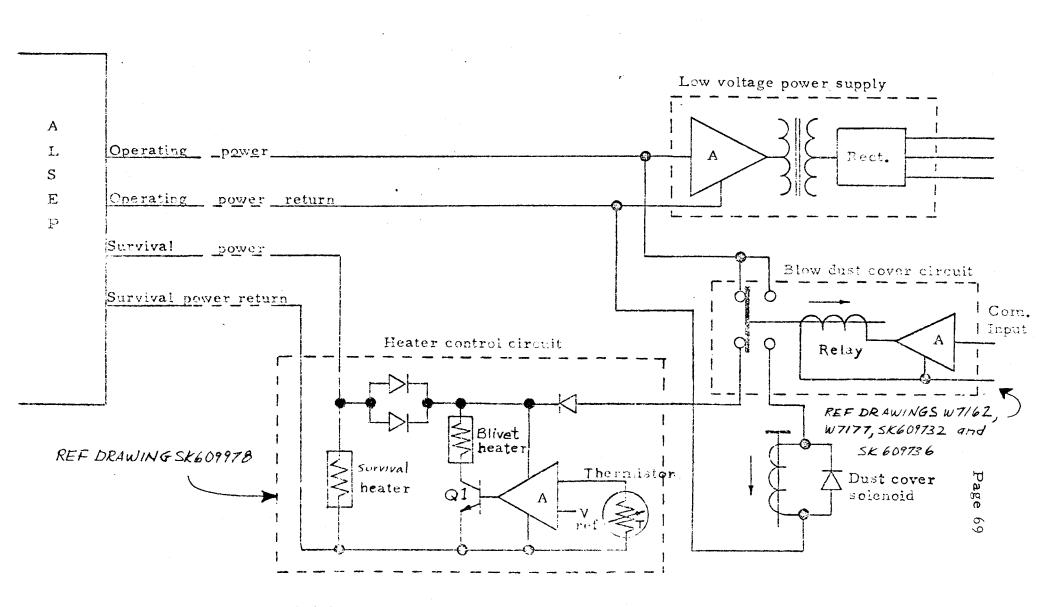

| 5.1.10-1 | Blow Dust Cover and Heater Control Circuit              | 69         |

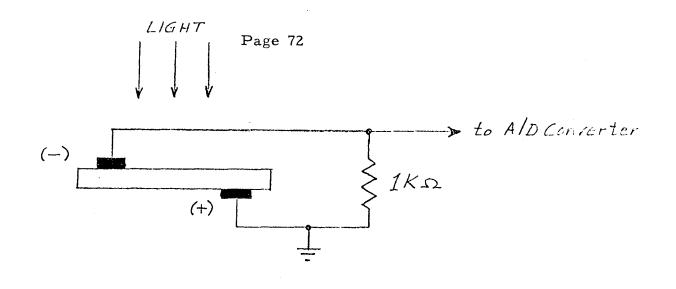

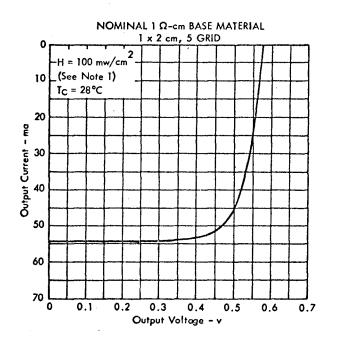

| 5.1.11-1 | Solar Cell, Schematic                                   | 72         |

| 5.1.11-2 | Solar Cell Current - Voltage Characteristics            | 72         |

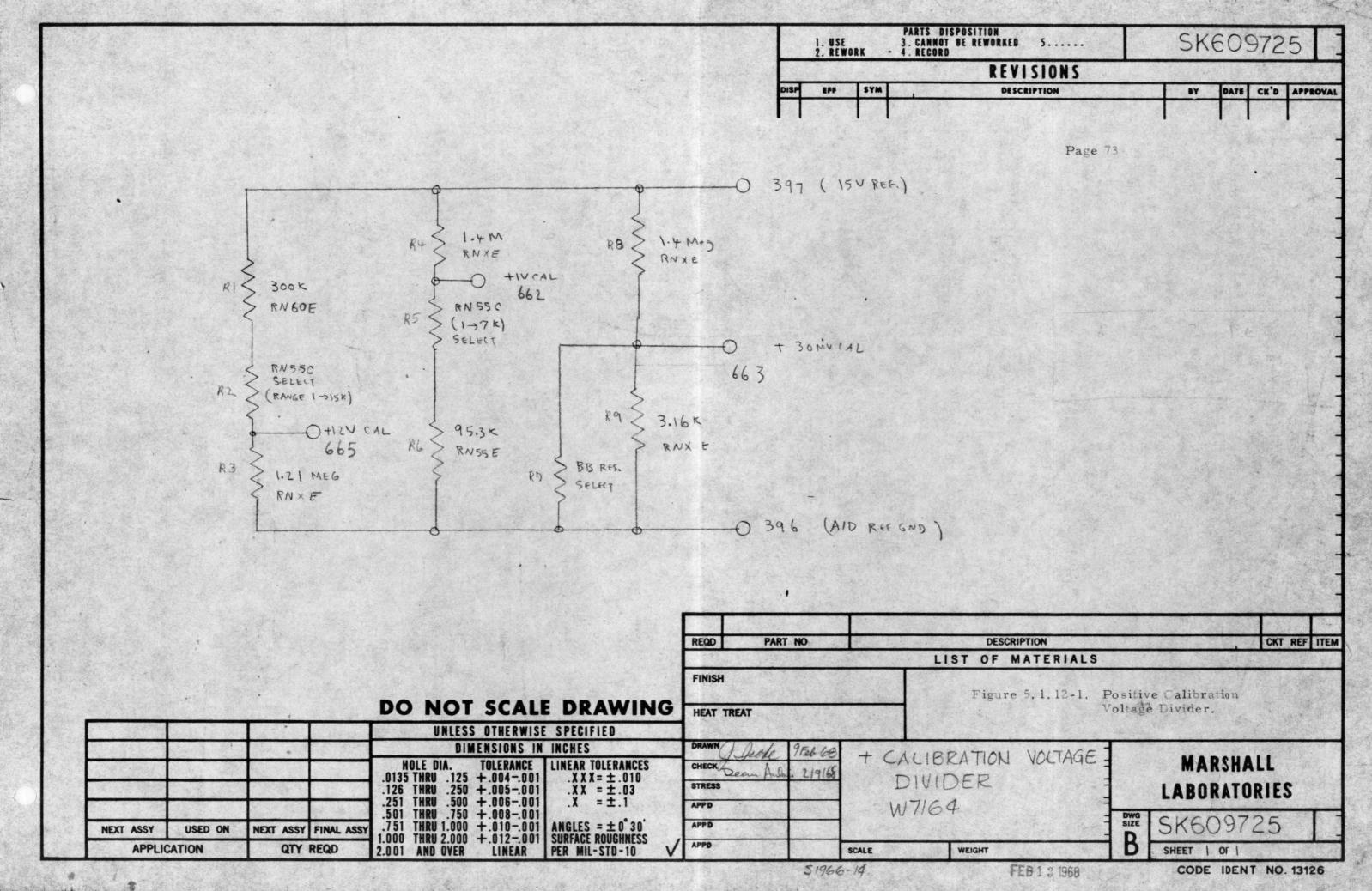

| 5.1.12-1 | Positive Calibration Voltage Divider                    | 73         |

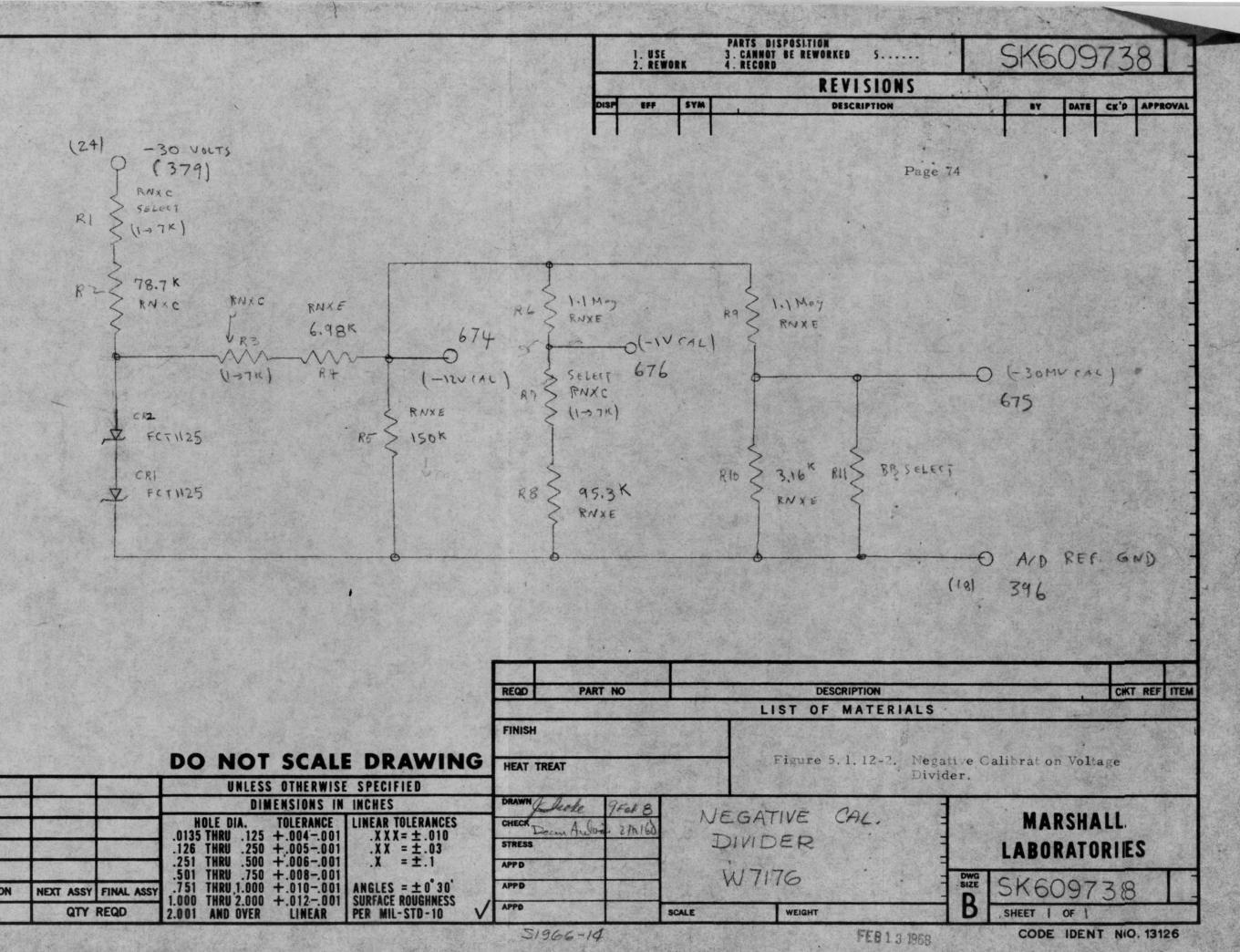

| 5.1.12-2 | Negative Calibration Voltage Divider                    | 74         |

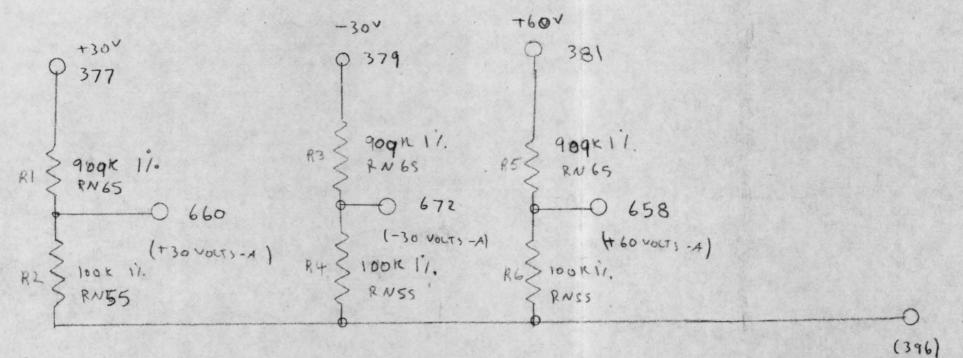

| 5.1.12-3 | +30, -30, +60v Divider                                  | <b>7</b> 5 |

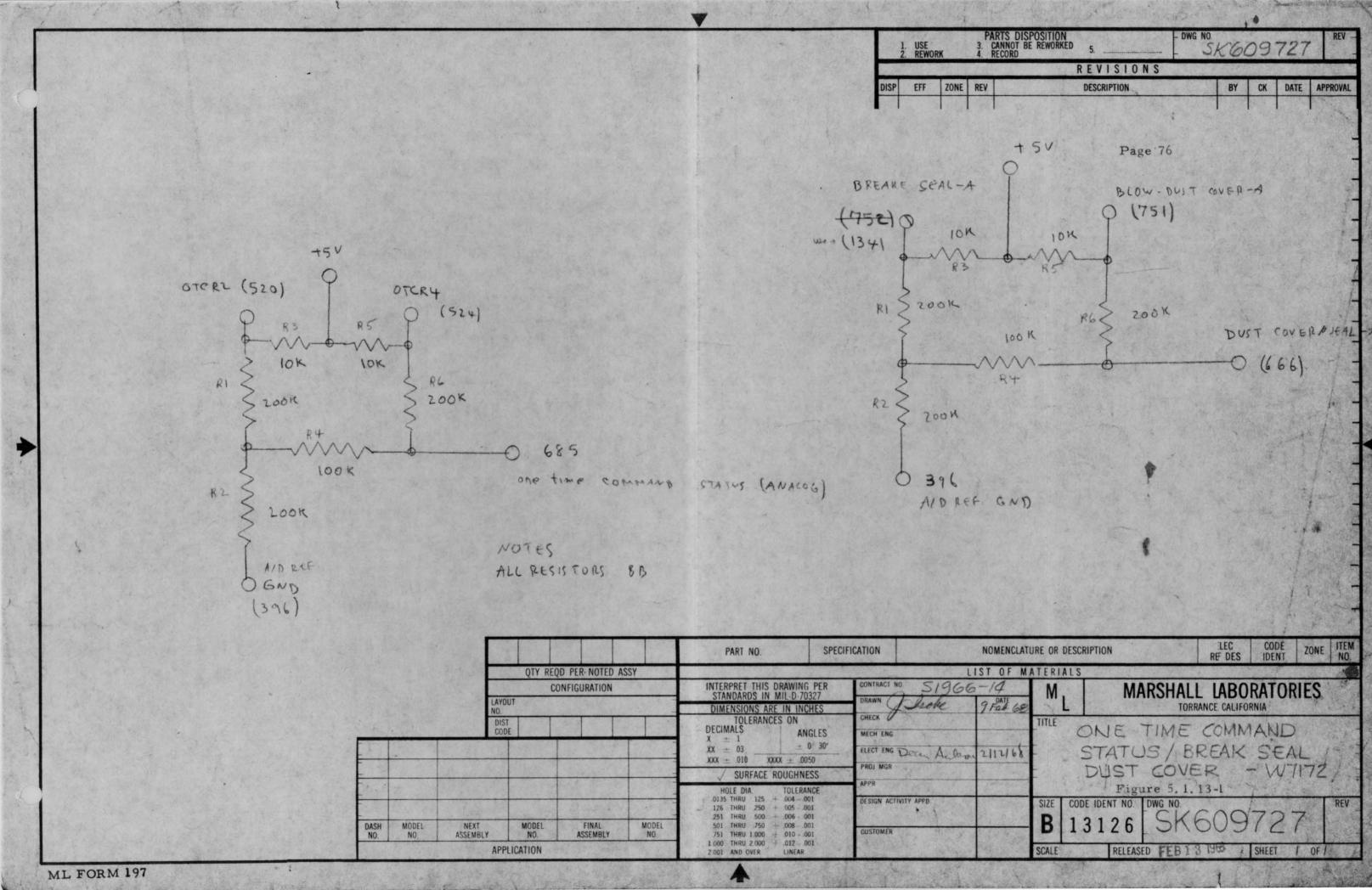

| 5.1.13-1 | One Time Command Status/Break Seal<br>Dust Cover        | 76         |

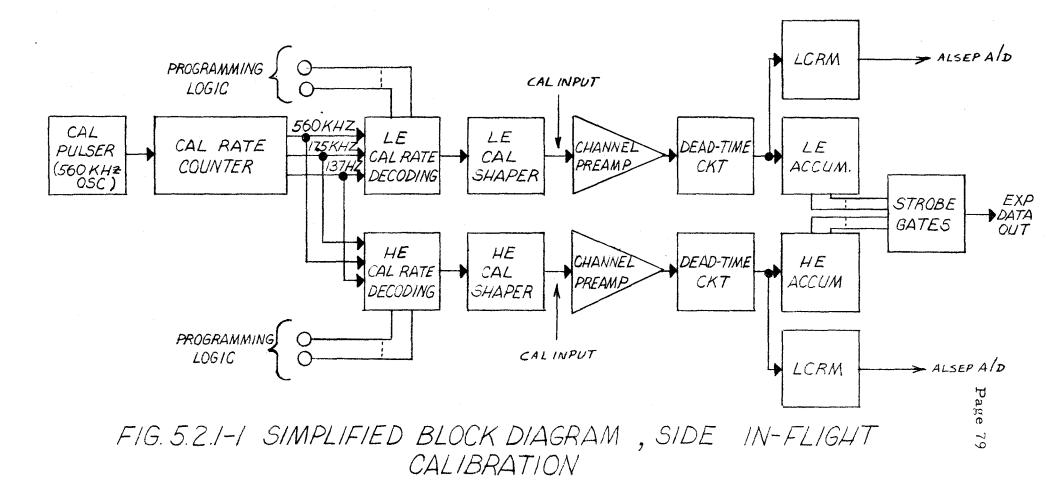

| 5.2.1-1  | Simplified Block Diagram, Side In-Flight<br>Calibration | 79         |

| 5.2.2-1  | Simplified Block Diagram, -3.5 Kv P.S.                  | 81         |

Page xvi

| Figure  | Title                                                               | Page |

|---------|---------------------------------------------------------------------|------|

| 5.2.3-1 | Channeltron Preamplifier, Block Diagram                             | 82   |

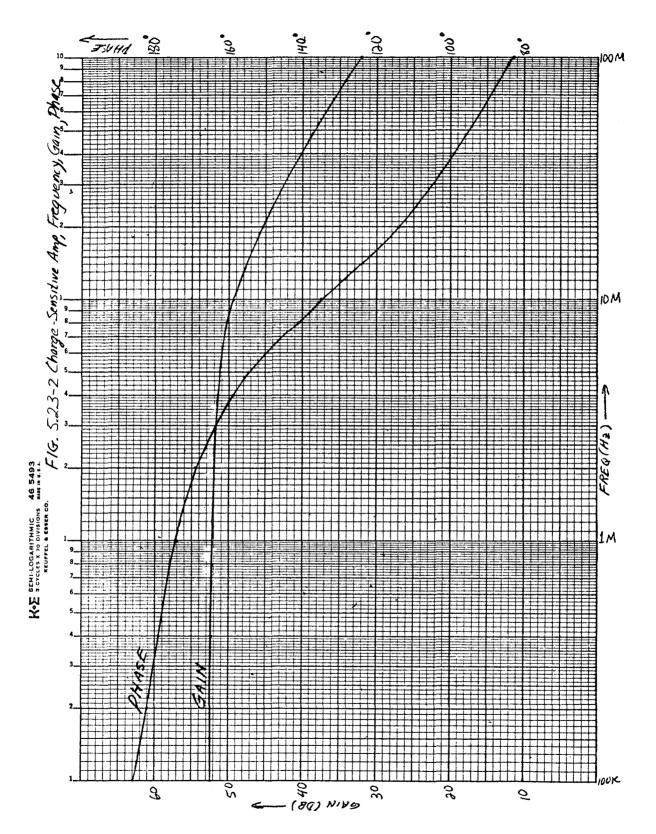

| 5.2.3-2 | Charge-Sensitive Amplifier, Frequency/Gain/<br>Phase                | 84   |

| 5.2.4-l | Dead-Time Circuit, Block Diagram                                    | 85   |

| 5.2.5-1 | Log Count Rate Meter, Simplified<br>Block Diagram                   | 87   |

| 5.2.5-2 | Log Count Rate Meter Output, Typical<br>System                      | 89   |

| 5.2.6-1 | Low Energy Accumulator Timing Relationships                         | 90   |

| 5.2.6-2 | Accumulator (High Energy and Low Energy)<br>Block Diagram           | 91   |

| 5.2.7-1 | Low Energy Step Voltage Generator,<br>Simplified Block Diagram      | 93   |

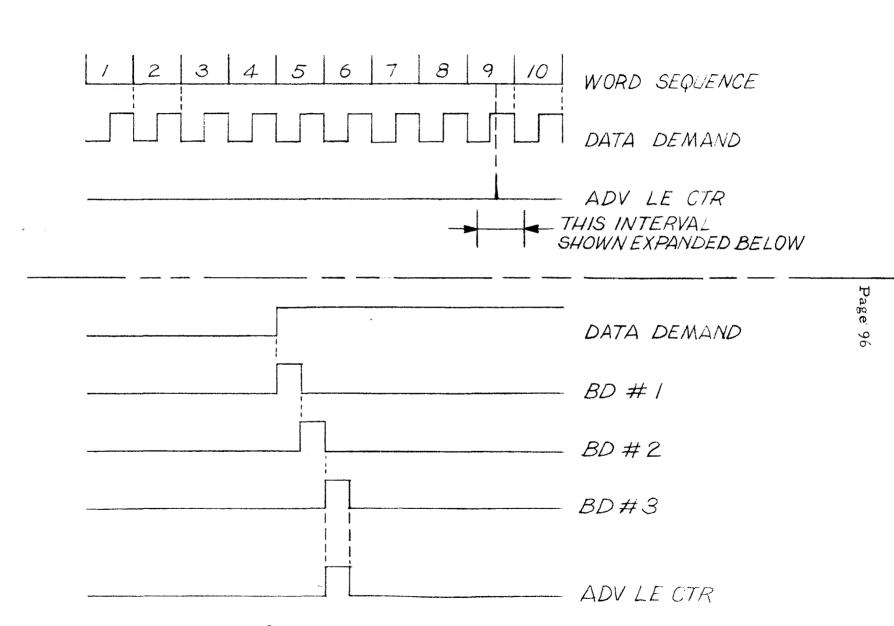

| 5.2.7-2 | Advance Low Energy Counter Timing                                   | 96   |

| 5.2.7-3 | Two Configuration of the Low Energy<br>Differential Amplifier       | 99   |

| 5.2.7-4 | Cal Cycle Timing                                                    | 100  |

| 5.2.8-1 | Velocity Filter Step Voltage Generator,<br>Simplified Block Diagram | 102  |

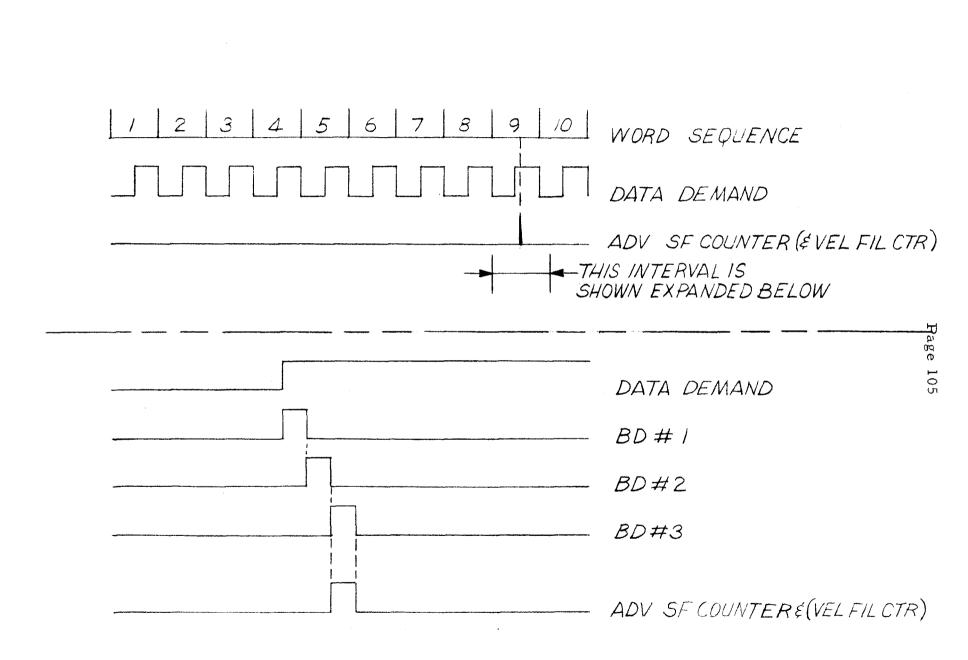

| 5.2.8-2 | Advance SIDE Frame Counter Timing                                   | 105  |

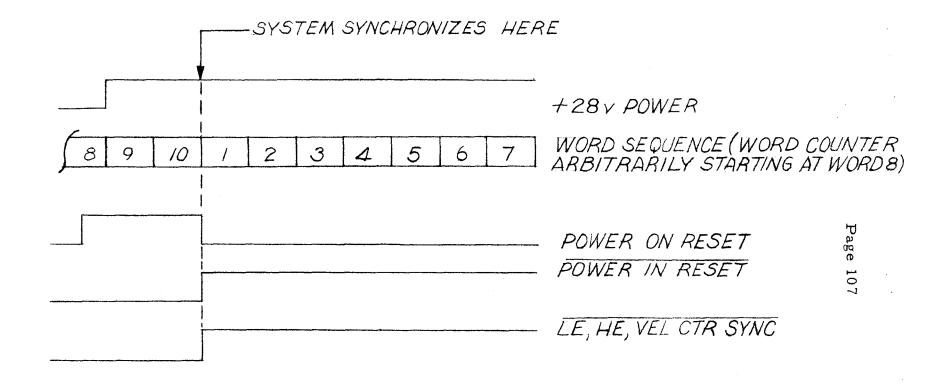

| 5.2.8-3 | Power and Low Energy Velocity<br>Counter Sync Timing                | 107  |

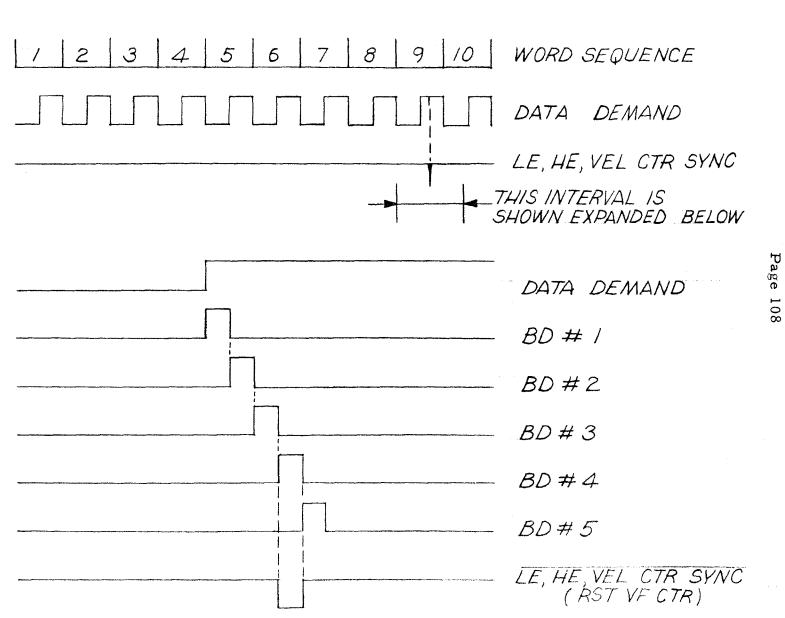

| 5.2.8-4 | Low Energy, High Energy Counter Sync<br>Timing                      | 108  |

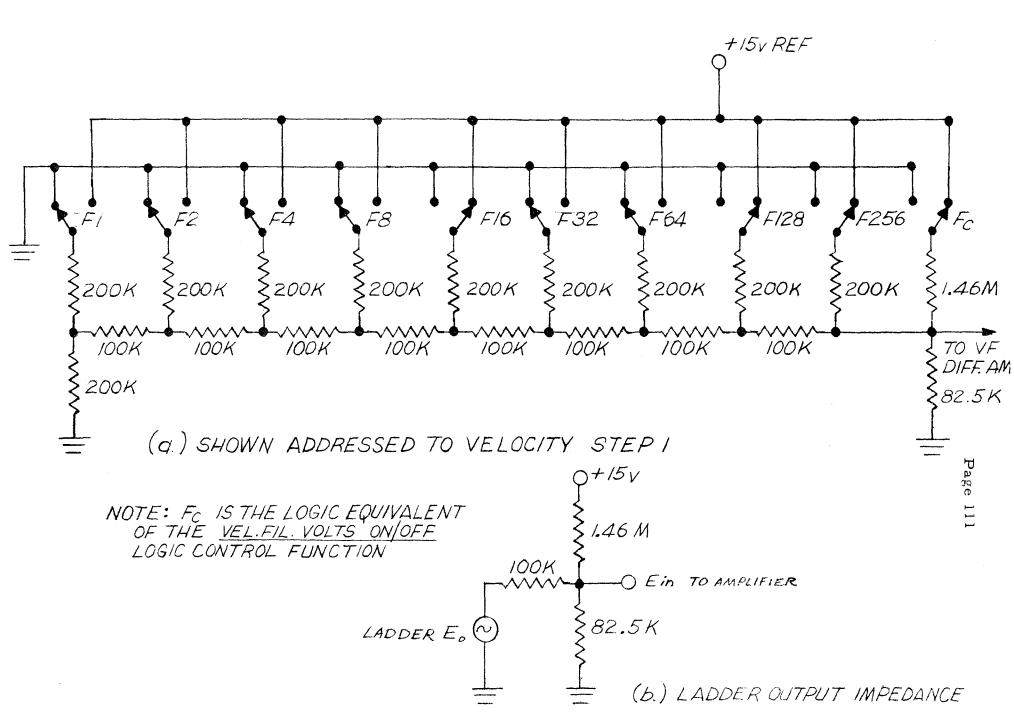

| 5.2.8-5 | Velocity Filter Ladder Network Equivalent<br>Circuit                | 111  |

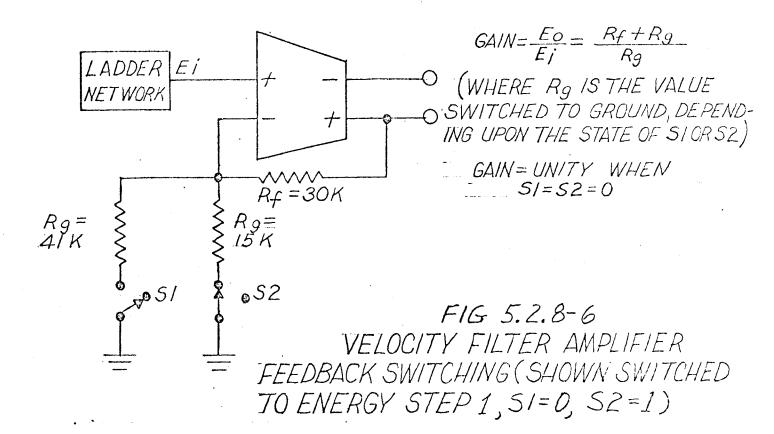

| 5.2.8-6 | Velocity Filter Amplifier Feedback Switching                        | 113  |

## Page xvii

| Figure  | Title                                                            | Page |

|---------|------------------------------------------------------------------|------|

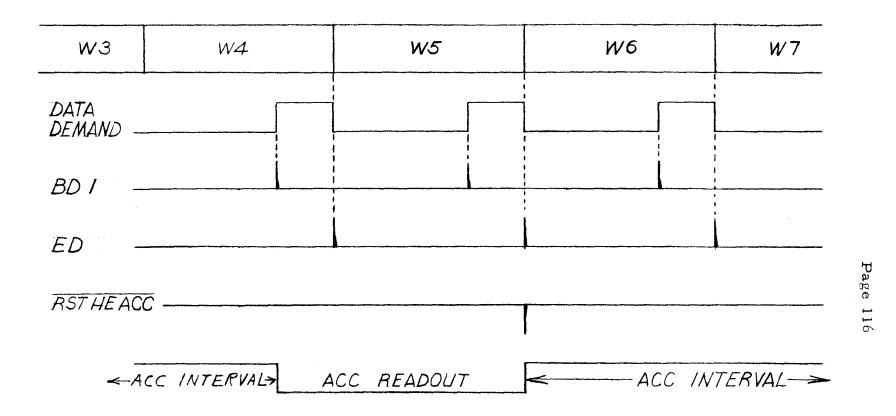

| 5.3.6-1 | High Energy Accumulator Timing Relationships                     | 116  |

| 5.3.7-1 | High Energy Step Voltage Generator Block<br>Diagram              | 118  |

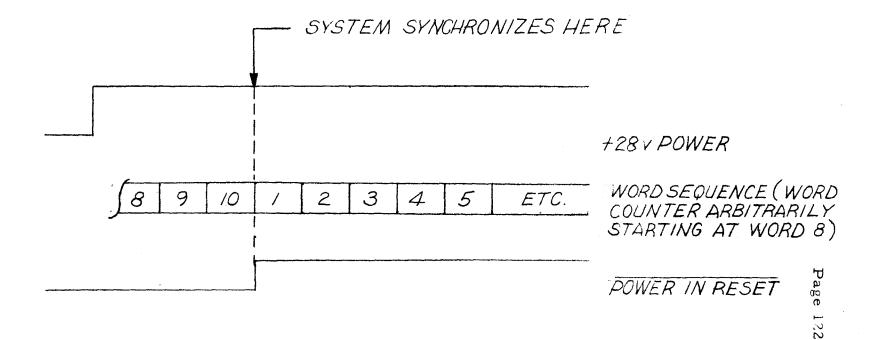

| 5.3.7-2 | Power On and Power On Reset Timing                               | 122  |

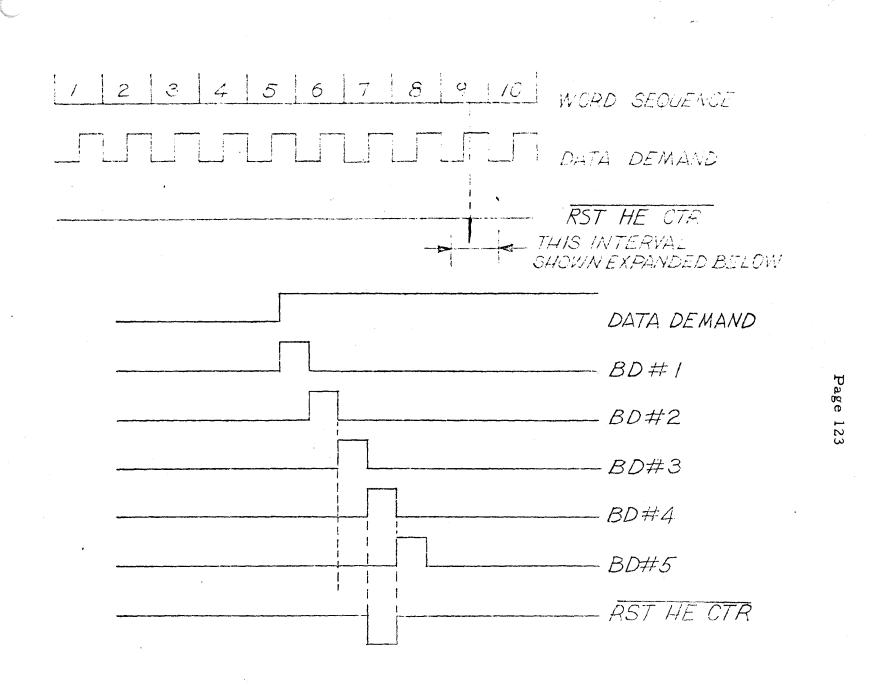

| 5.3.7-3 | Reset High Energy Counter Timing                                 | 123  |

| 5.3.7-4 | Advance High Energy Counter Timing                               | 124  |

| 5.3.7-5 | High Energy Cal Cycle Timing                                     | 126  |

| 5.3.7-6 | High Energy Ladder Equivalent Circuits                           | 127  |

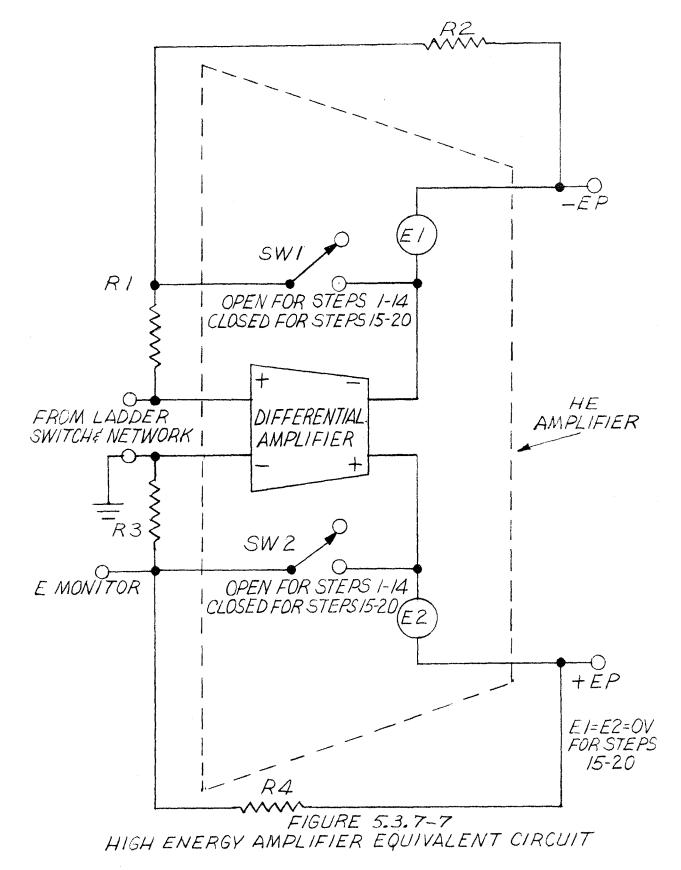

| 5.3.7-7 | High Energy Amplifier Equivalent Circuit                         | 129  |

| 5.4.1-1 | Electrometer Simplified Block Diagram                            | 132  |

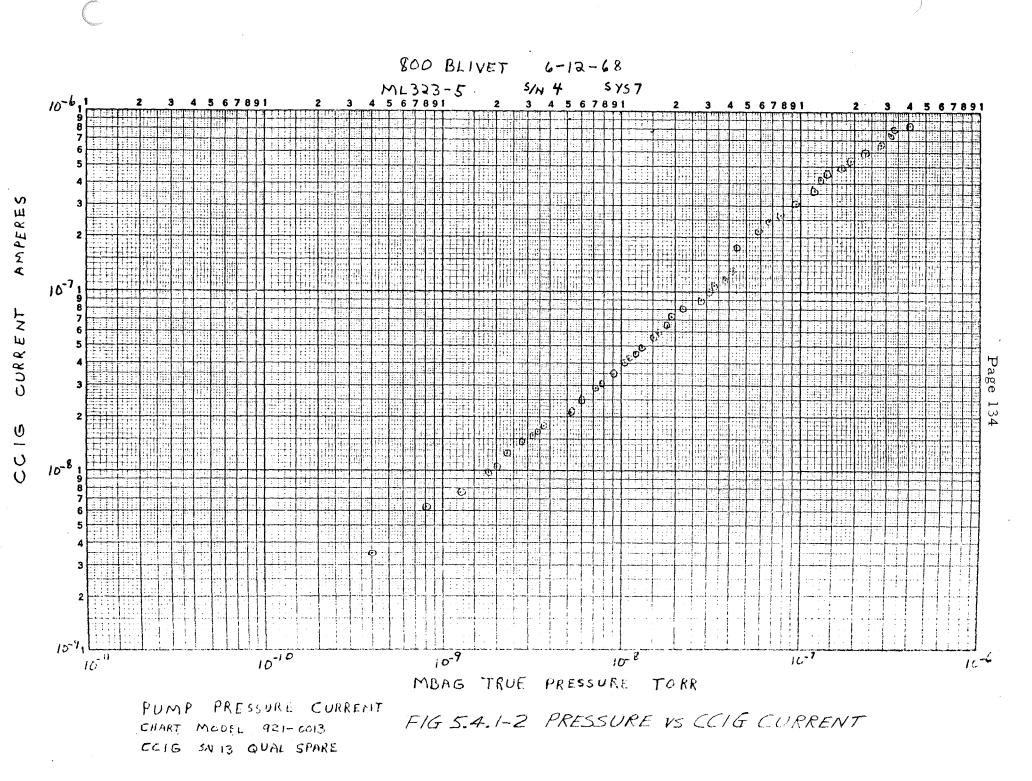

| 5.4.1-2 | Pressure vs. CCIG Current                                        | 134  |

| 5.4.1-3 | Electrometer Transfer Function                                   | 135  |

| 5.4.1-4 | Electrometer Range, Auto Zero and Calibrate<br>Switching         | 137  |

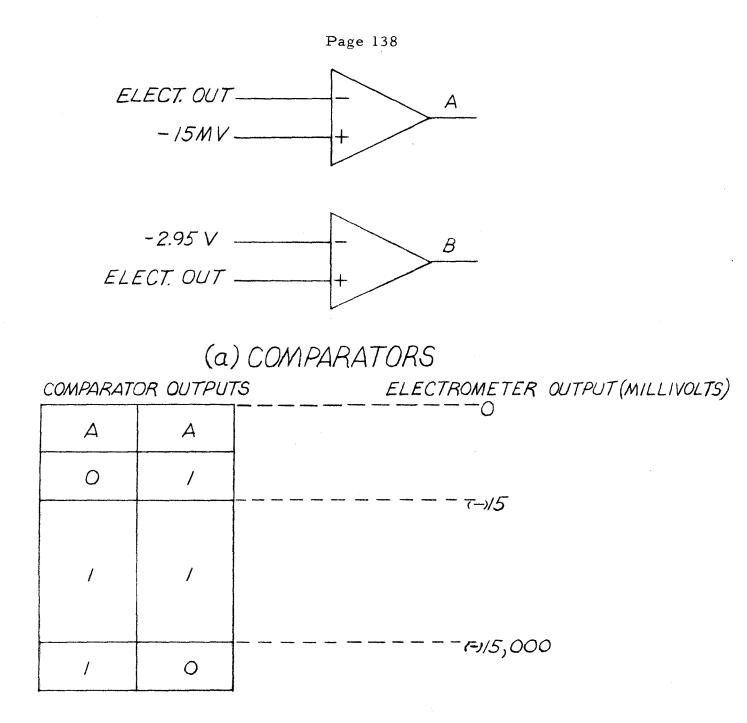

| 5.4.1-5 | Simplified Electrometer Range Logic                              | 138  |

| 5.4.1-6 | Electrometer Comparator Decoding                                 | 139  |

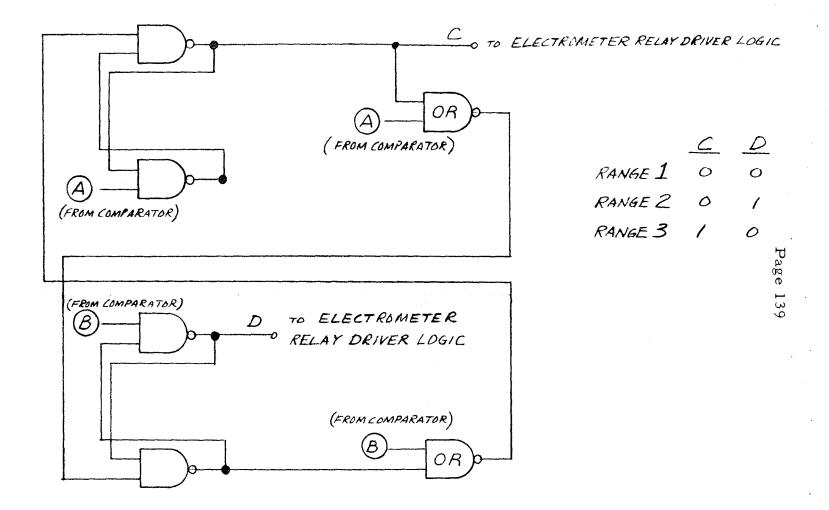

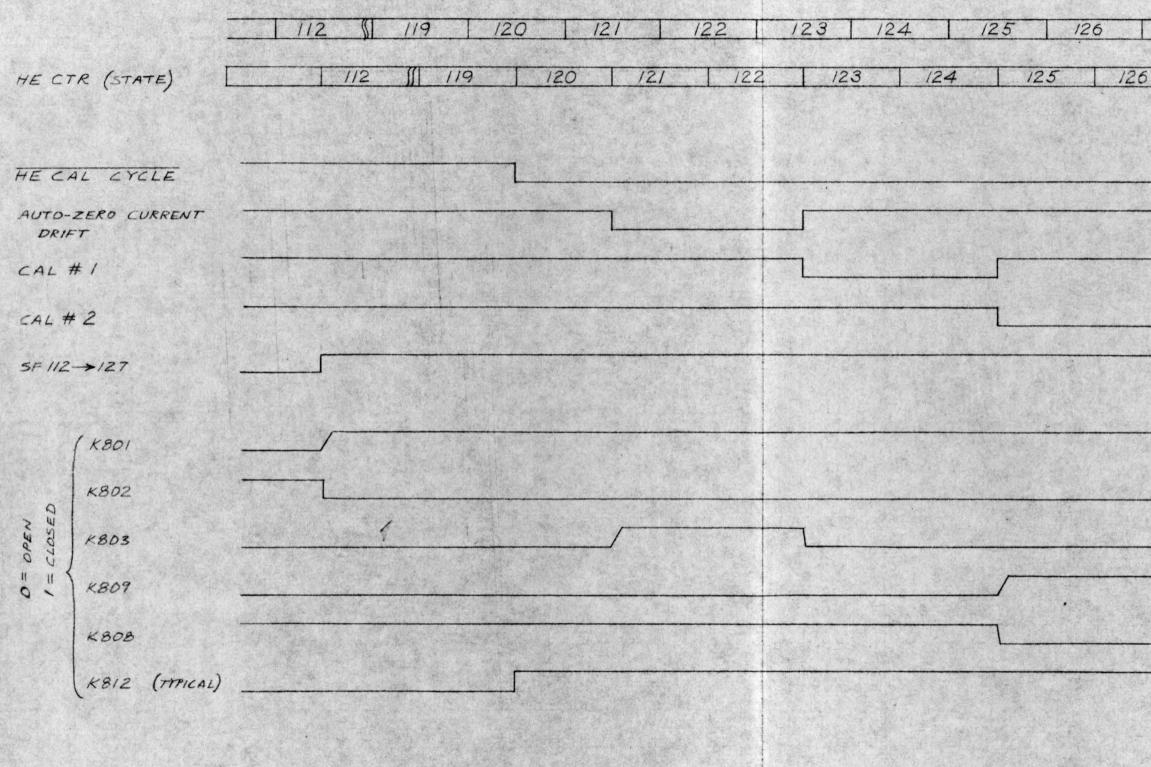

| 5.4.1-7 | Electrometer Switching Timing Diagram                            | 140  |

| 5.4.3-1 | Seal Mechanism Power Supply, Block Diagram                       | 142  |

| 5.4.5-1 | 4500V Power Supply, Block Diagram                                | 144  |

| 5.5-1   | Ground Plane Step Voltage Generator, Simplified<br>Block Diagram | 146  |

| 5.5-2   | Ground Plane Counter Advance Timing                              | 149  |

| 5.5-3   | Ladder Switch and Network Polarity Switches                      | 150  |

Page xviii

| Figure | Title                                                               | Page |

|--------|---------------------------------------------------------------------|------|

| 5.5-4  | Ground Plane Amplifier Positive<br>Configuration Equivalent Circuit | 151  |

| 5.5-5  | Ground Plane Amplifier Negative<br>Configuration Equivalent Circuit | 151  |

| 6.0-1  | ETS System Interface - Configuration 1                              | 156  |

| 6.0-2  | ETS System Interface - Configuration 2                              | 157  |

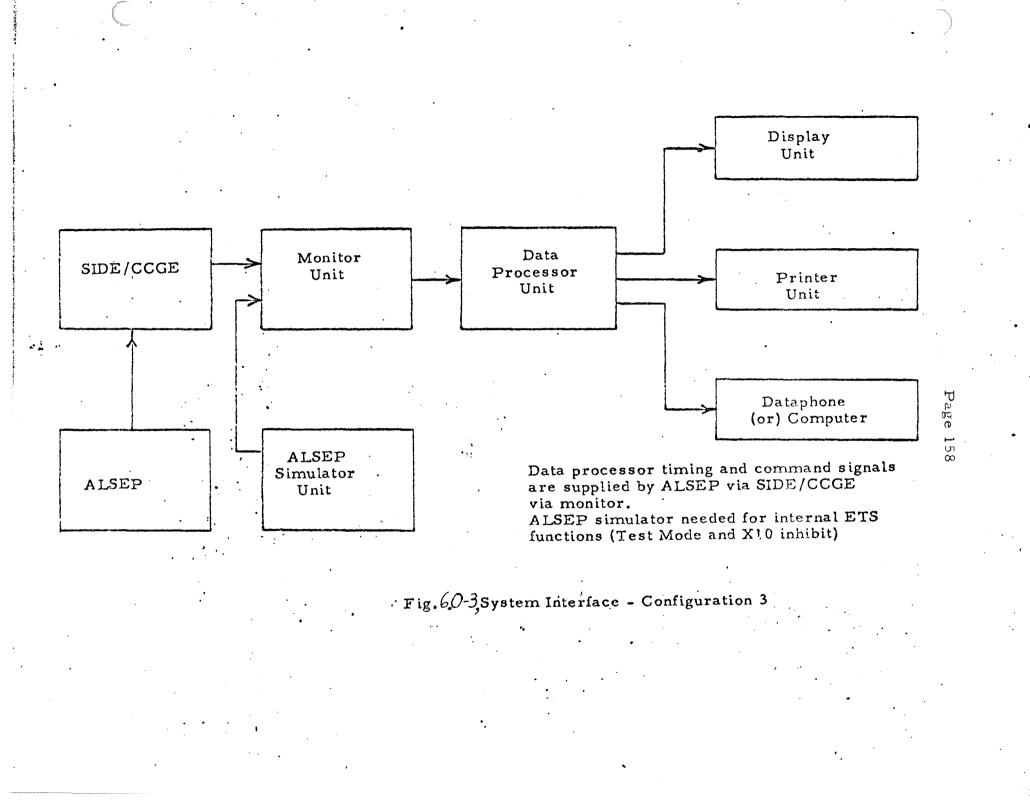

| 6.0-3  | ETS System Interface - Configuration 3                              | 158  |

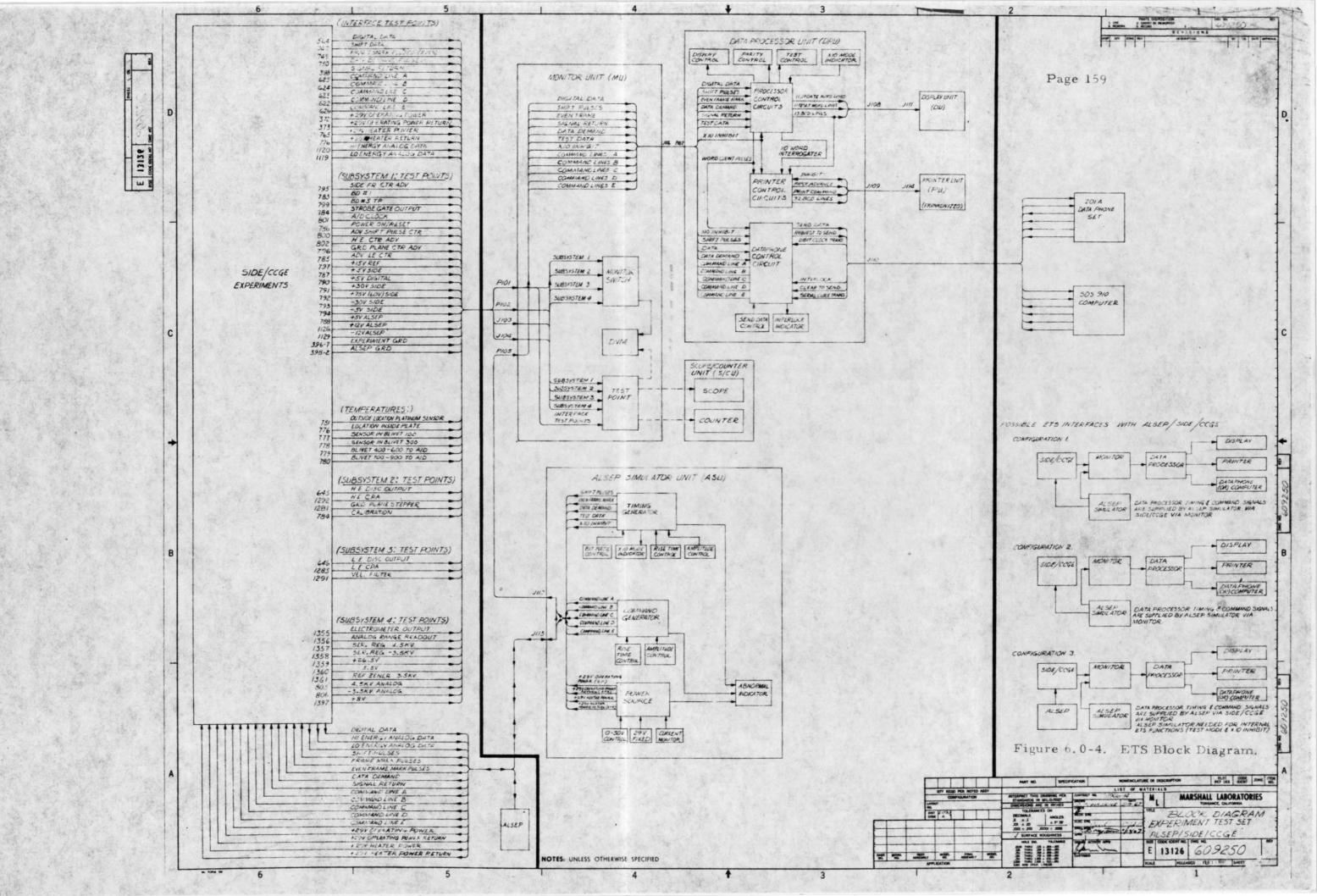

| 6.0-4  | ETS Block Diagram                                                   | 159  |

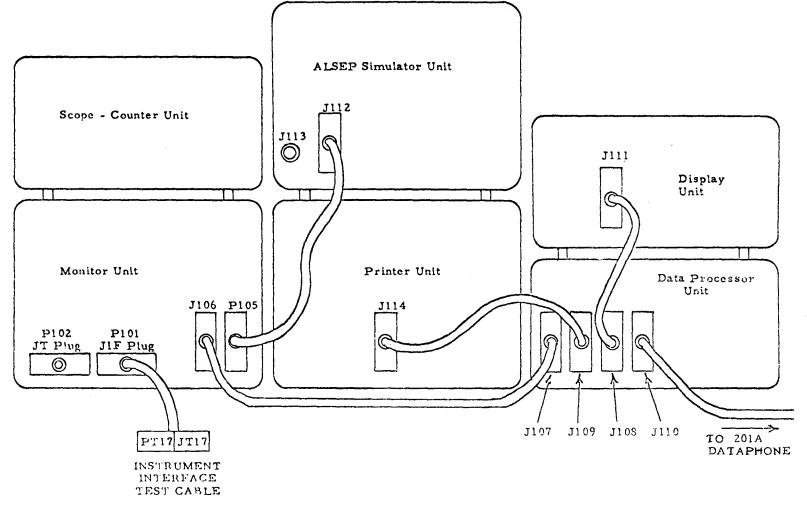

| 6.0-5  | Instrument/ETS Test Set UP (Typical)                                | 160  |

| 6.0-6  | ETS Configuration                                                   | 161  |

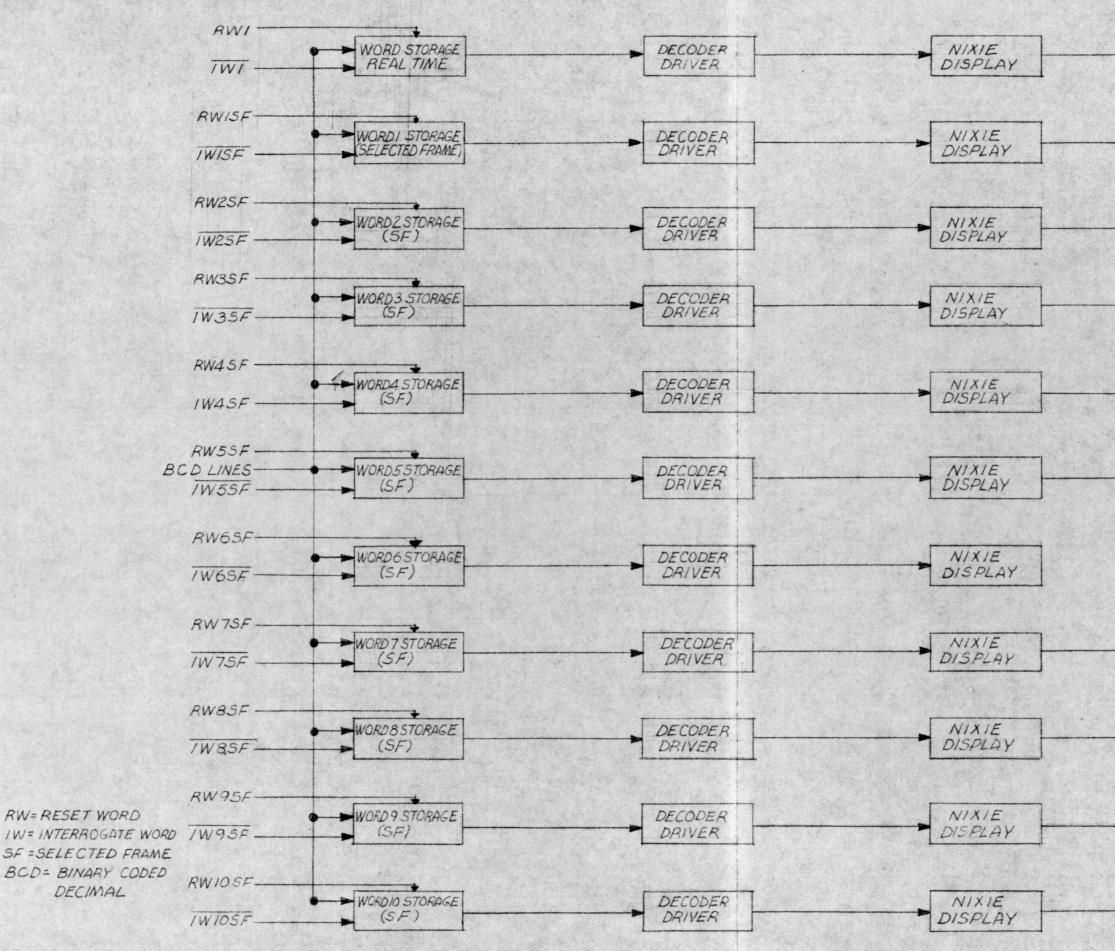

| 6.1-1  | Block Diagram - Display Unit                                        | 164  |

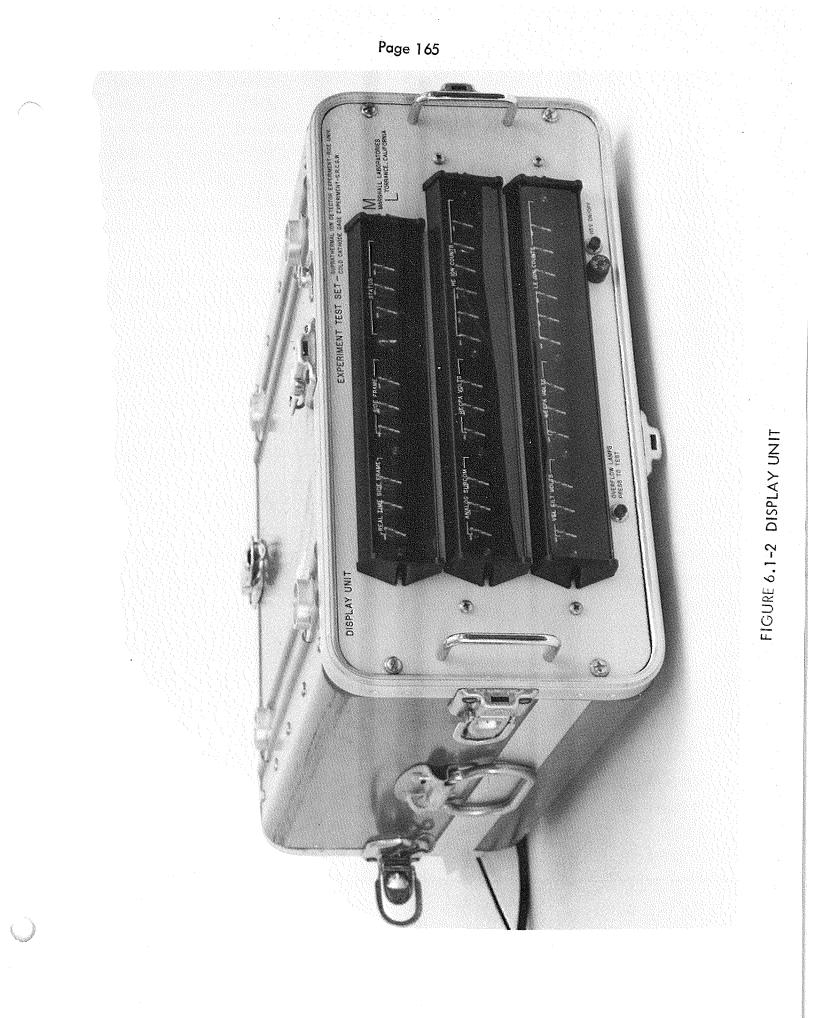

| 6.1-2  | Display Unit                                                        | 165  |

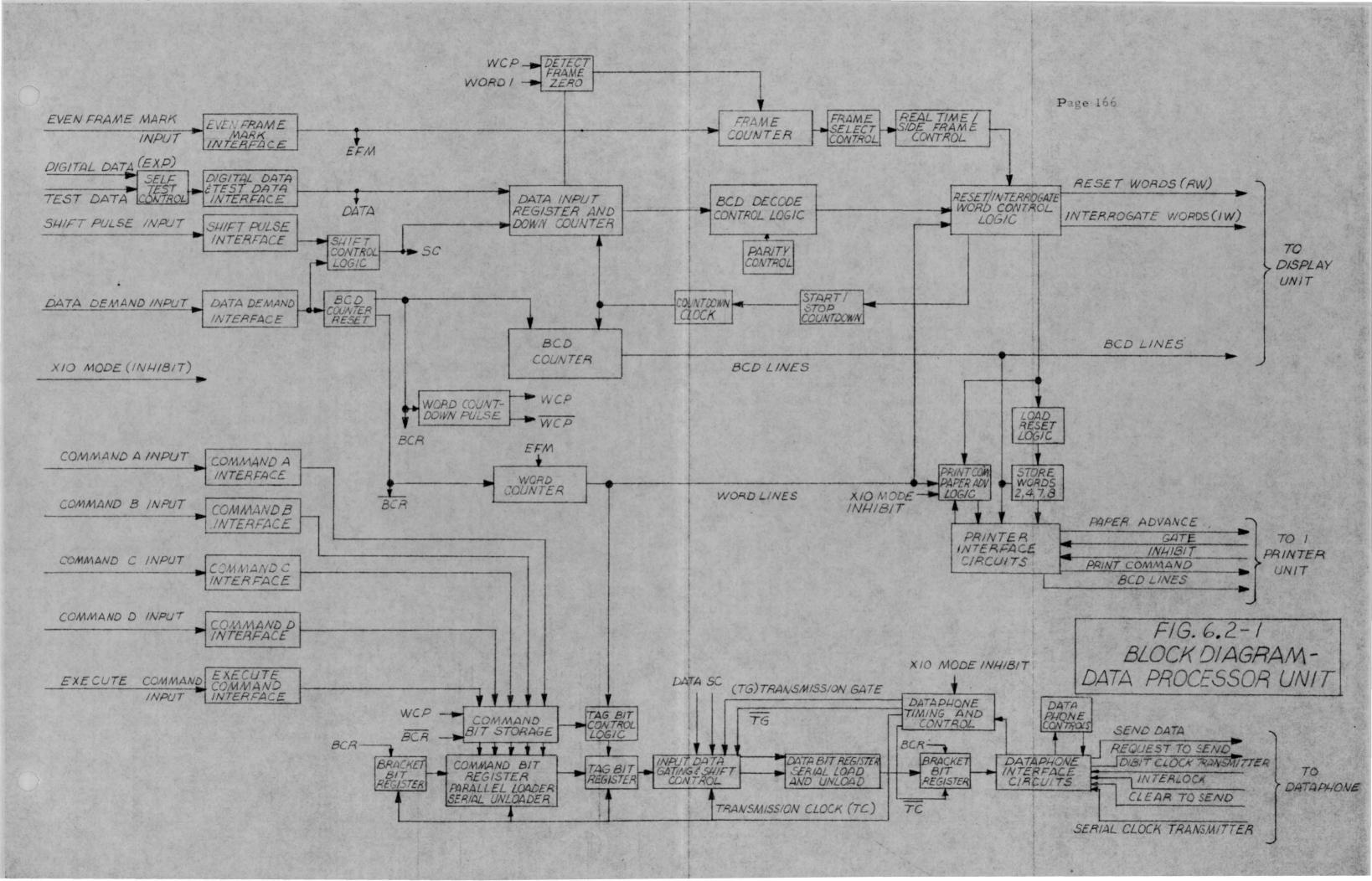

| 6.2-1  | Block Diagram - Data Processor Unit                                 | 166  |

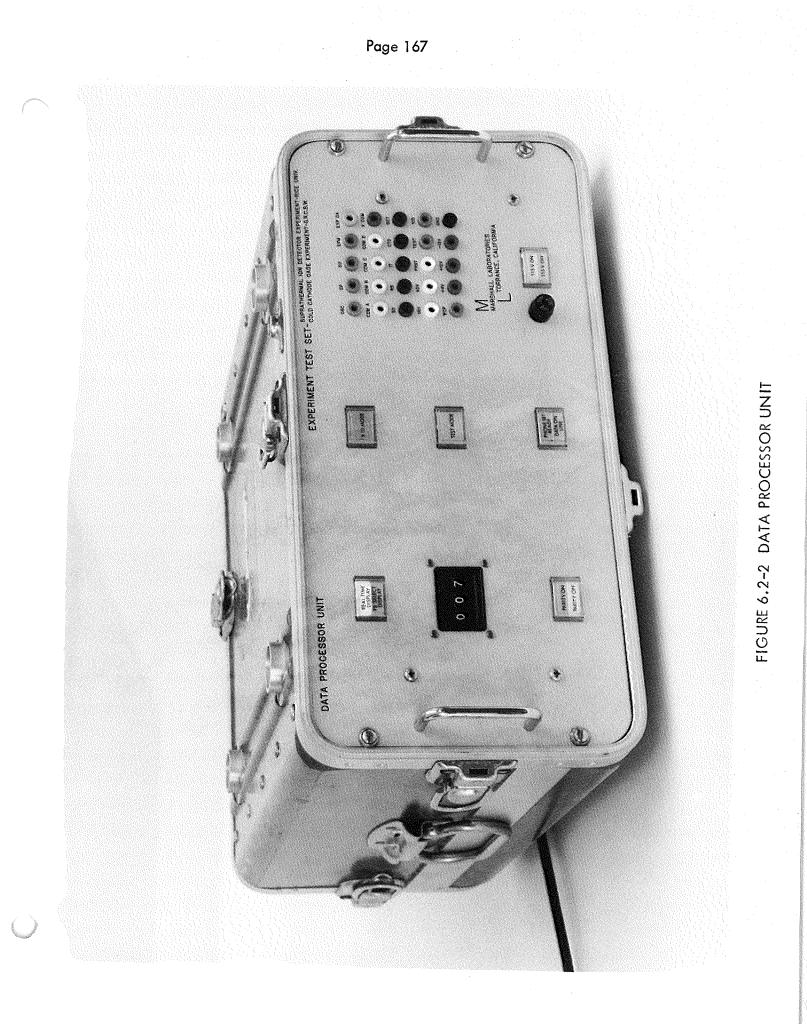

| 6.2-2  | Data Processor Unit                                                 | 167  |

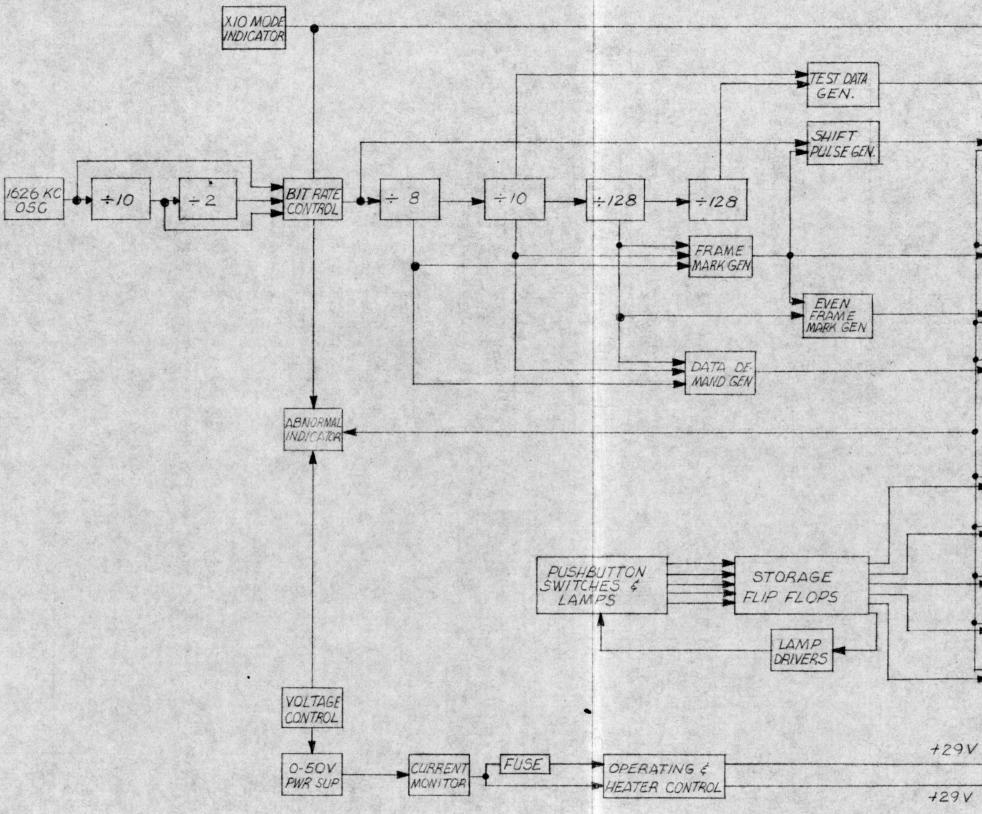

| 6.3-1  | Block Diagram - ALSEP Simulator Unit                                | 170  |

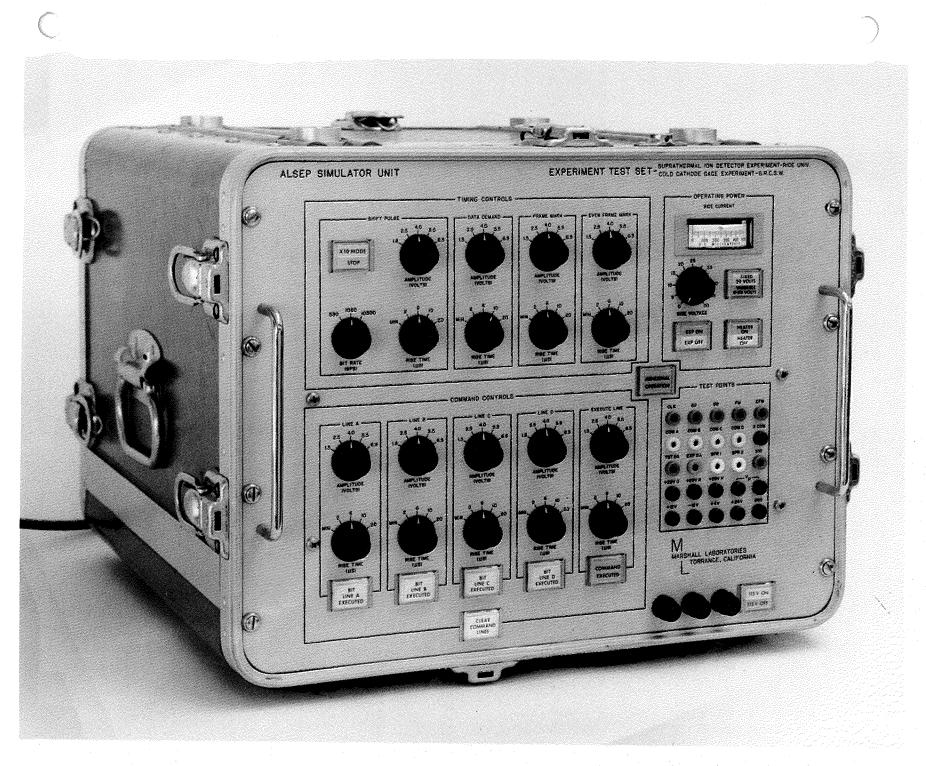

| 6.3-2  | ALSEP Simulator Unit                                                | 171  |

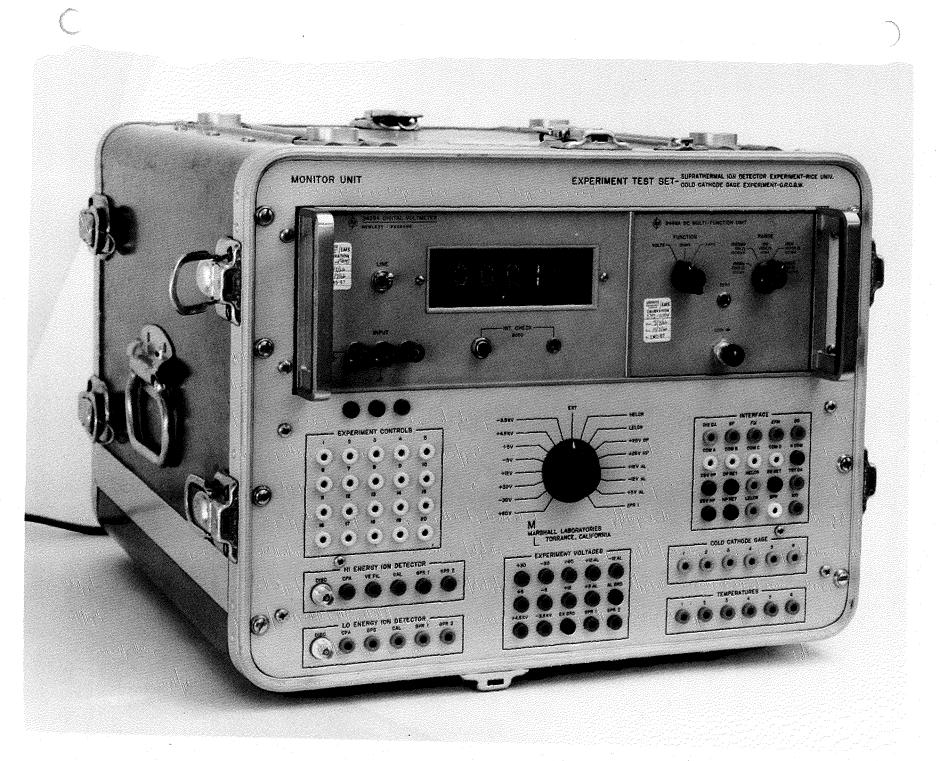

| 6.4-1  | Monitor Unit                                                        | 173  |

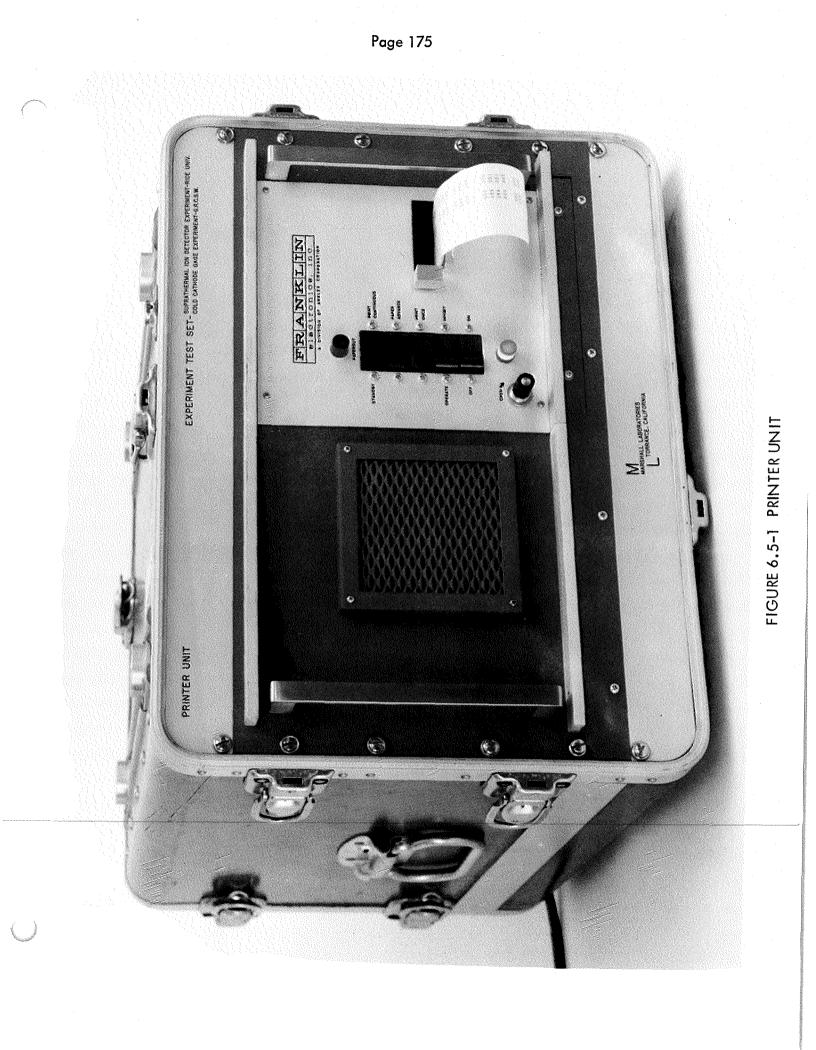

| 6.5-1  | Printer Unit                                                        | 175  |

| 6.6-1  | Oscilloscope/Counter Unit                                           | 176  |

| 7-1    | CCIG Instrument                                                     | 178  |

| 7-2    | Cables, Reels, and Connectors                                       | 179  |

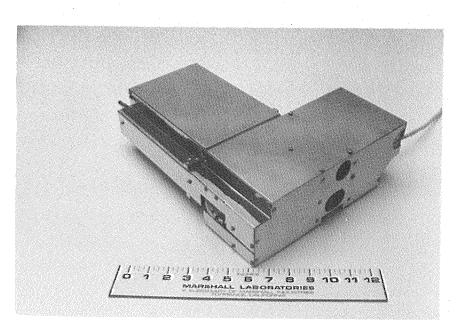

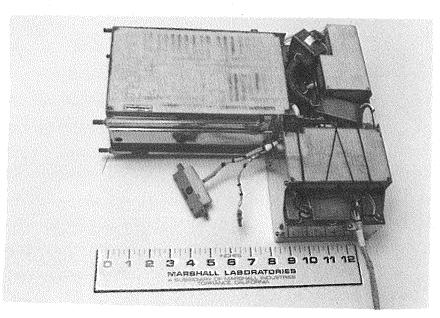

| 7-3    | Ion Detector Instrument                                             | 183  |

| 7-4    | Collapsible Leg Configuration                                       | 185  |

## Page xix

| Figure       | Title                                                          | Page |

|--------------|----------------------------------------------------------------|------|

| 7 <b>-</b> 5 | Discrete Module                                                | 186  |

| 7-6          | Package - Riser Weld                                           | 187  |

| 7-7          | Flat-pack Interconnection (Typical                             | 188  |

| 7-8          | Module Interconnect Matrix                                     | 189  |

| 7-9          | Channeltron Electron Multipliers                               | 191  |

| 7-10         | SIDE Thermal Control                                           | 199  |

| 7-11         | ALSEP/SIDE/CCGE Internal Assembly                              | 200  |

| 7-12         | Assembly Drawing, Astronaut Training Unit                      | 203  |

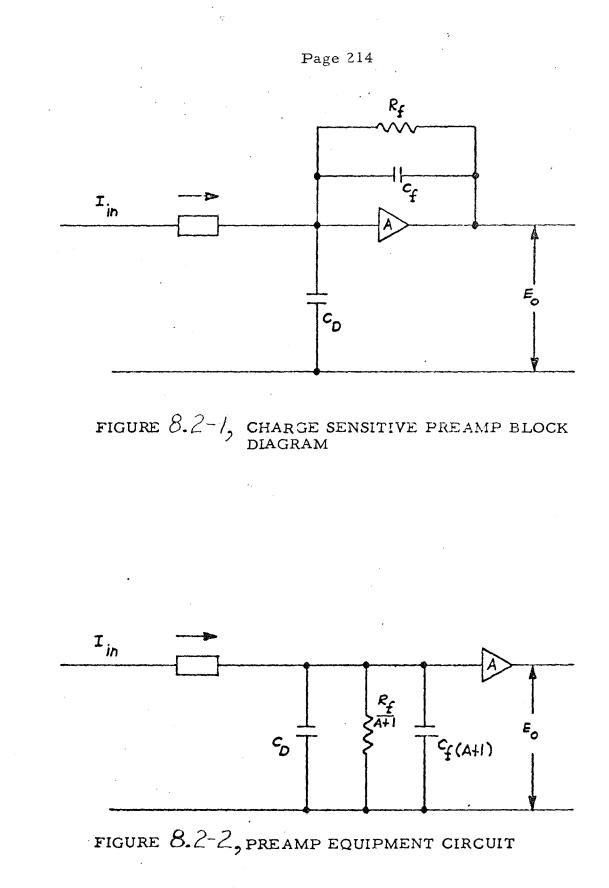

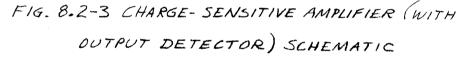

| 8.2-1        | Charge Sensitive Preamp, Block Diagram                         | 214  |

| 8.2-2        | Preamp Equipment Circuit                                       | 214  |

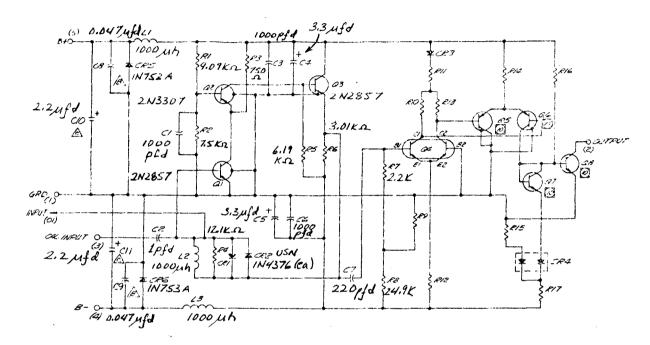

| 8.2-3        | Charge Sensitive Amplifier (with Output<br>Detector) Schematic | 215  |

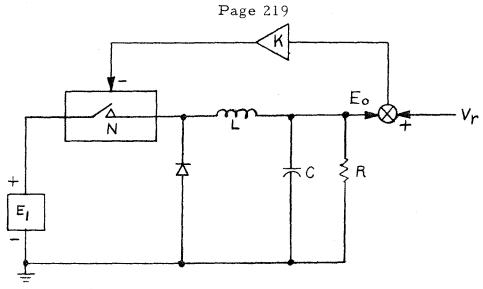

| 8.3-1        | Basic Switching-Mode Regulator                                 | 219  |

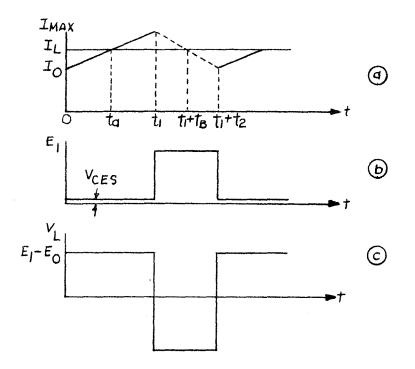

| 8.3-2        | Waveforms, Switching Mode Regulator                            | 219  |

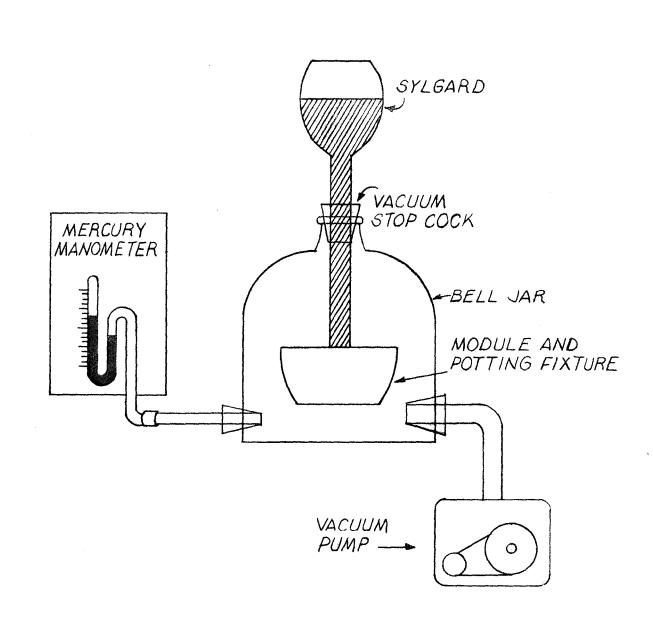

| 8.4-1        | Vacuum Encapsulation Setup                                     | 222  |

## Page xx

## TABLES

| Table   | Title                                                               | Page |

|---------|---------------------------------------------------------------------|------|

| 3.1A    | Energy Levels, Low Energy Ion<br>Detector                           | 26   |

| 3.2A    | Energy Levels, High Energy Ion<br>Detector                          | 27   |

| 3.4.2A  | ALSEP Command Table                                                 | 35   |

| 5.1.2A  | Temperature Sensor, Resistance vs<br>Temperature Characteristics    | 48   |

| 5.1.10A | Heater Power                                                        | 70   |

| 5.1.10B | Heater Control Sensor, Resistance<br>vs Temperature Characteristics | 70   |

| 5.1.13A | Break Seal-Dust Cover Monitor<br>Status                             | 77   |

| 5.2.1A  | Calibrate Frequencies                                               | 78   |

| 5.2.5A  | Log Count Rate Meter, Output<br>vs Frequency                        | 88   |

| 5.2.7A  | Low Energy CPA and A/D Monitor<br>Voltages                          | 94   |

| 5.2.7B  | Low Energy Counter Output                                           | 97   |

| 5.2.7C  | Address to Low Energy Mul <b>tiplier</b><br>Network                 | 97   |

| 5.2.7D  | Low Energy Amplifier Transfer Functions                             | 99   |

| 5.2.8A  | Velocity Filter Plate Voltages<br>(plate-to-plate)                  | 103  |

| 5.2.8B  | Velocity Filter A/D Monitor Voltages                                | 104  |

## Page xxi

| Table  | Title                                                                                                      | Page        |

|--------|------------------------------------------------------------------------------------------------------------|-------------|

| 5.2.8C | Velocity Filter Counter Output Address                                                                     | 109         |

| 5.2.8D | Velocity Filter Ladder Address                                                                             | 110         |

| 5.2.8E | Energy Range Decoding Logic Output<br>Address; Velocity Filter Amplifier<br>Gain; Output Transfer Function | 113         |

| 5.2.8F | Velocity Filter Ladder Output Voltage                                                                      | 114         |

| 5.3.7A | High Energy CPA and A/D Monitor<br>Voltages                                                                | 120         |

| 5.3.7B | High Energy Counter Output Address                                                                         | 121         |

| 5.3.7C | High Energy Ladder Output,<br>Amplifier Gain, and Nominal Plate<br>Voltages                                | 131         |

| 5.5A   | Ground Plane and A/D Monitor Voltages                                                                      | 147         |

| 5.5B   | Ground Plane Stepper Address Logic                                                                         | 152         |

| 5.5C   | Ground Plane Ladder Network Output<br>Voltage                                                              | 15 <b>3</b> |

| 7A     | SIDE Emplacement Criteria                                                                                  | 181         |

| 7B     | Specifications; Channeltron Electron<br>Multipliers                                                        | 192         |

| 7C     | ALSEP System Environments                                                                                  | 196         |

| 7D     | Envrionmental Duty Cycles                                                                                  | 197         |

## Page xxii

## ACKNOWLEDGEMENT

The authors wish to express their gratitude to all Rice University and Time-Zero Corporation (formerly Marshall Laboratories) personnel who contributed maximum assistance in the preparation of this document.

#### Page 1

### 1.0 INTRODUCTION

This engineering report describes the ALSEP/SIDE/CCGE Experiment designed, fabricated, tested, and delivered by Marshall Laboratories in accordance with Rice University Contract No. S1966-14.

The function of the experiment is to measure the flux, number density, velocity and energy per unit charge of positive ions near the lunar surface, and to detect any lunar ambient atmospheric pressure. The experiment will measure the differential energy spectrum of ions having energies from 0.2 ev to 3500 ev per unit charge.

The report covers electrical, thermal, and mechanical descriptions of the instrument. Also included is a description of the Experiment Test Set.

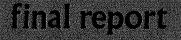

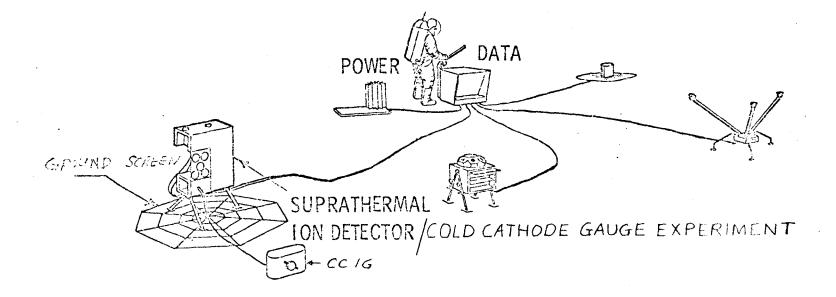

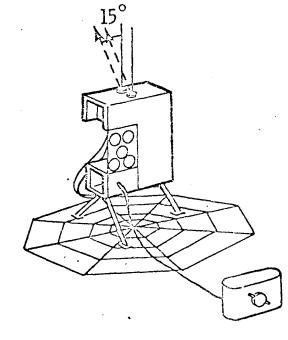

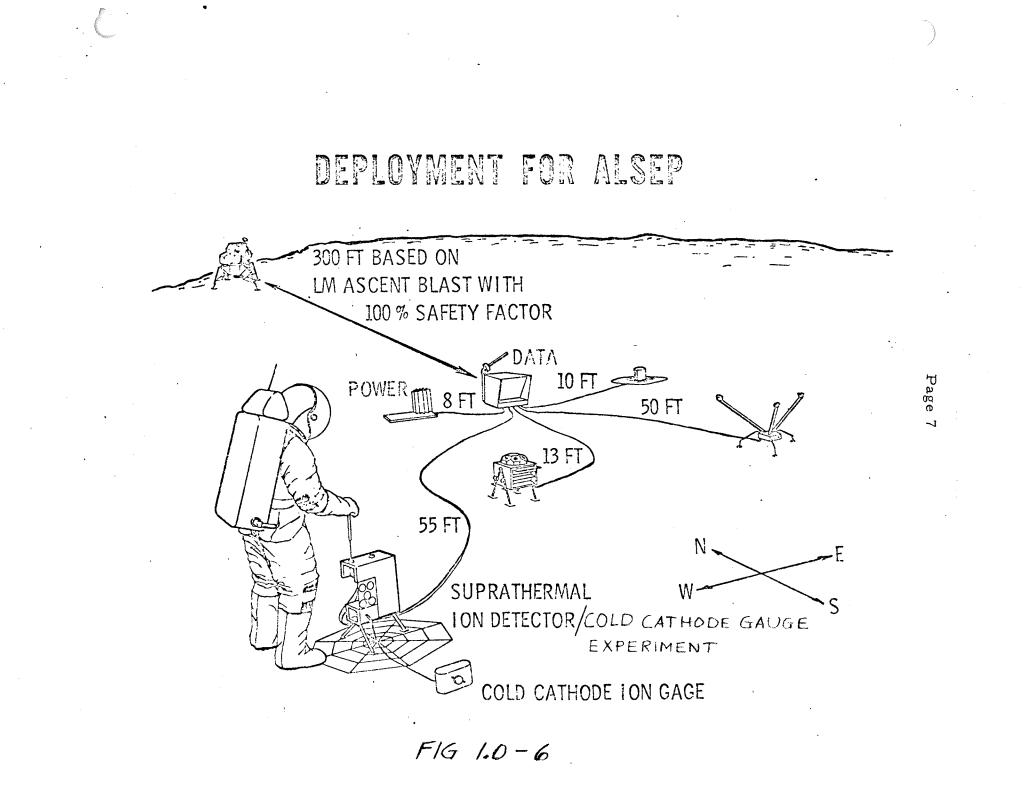

The following figures provide an introductory summary of pertinent features of the ALSEP/SIDE/CCGE Experiment:

| a) | Figure 1.0-1  | Lunar Surface Deployment       |

|----|---------------|--------------------------------|

| b) | Figure 1.0-2  | Close-Up Photograph, SIDE/CCGE |

|    | -             | in deployed Configuration      |

| c) | Figure 1.0-3  | ALSEP System Objectives        |

| d) | Figure 1.0-4  | SIDE/CCGE Objectives Summary   |

| e) | Figure 1.0-5  | Stowed Configuration           |

| f) | Figure 1.0-6  | Deployment for ALSEP           |

| g) | Figure 1.0-7  | SIDE/CCGE Deployment           |

| ĥ) | Figure 1.0-8  | ALSEP Objectives               |

| i) | Figure 1.0-9  | ALSEP Experiments              |

| j) | Figure 1.0-10 | SIDE/CCGE General Features     |

FIGURE 1.0-1 LUNAR SURFACE DEPLOYMENT

This Widely Published Illustration Features Time-Zero's Suprathermal Ion Detector Built For Rice University (Artist's Conception)

الغرب ا

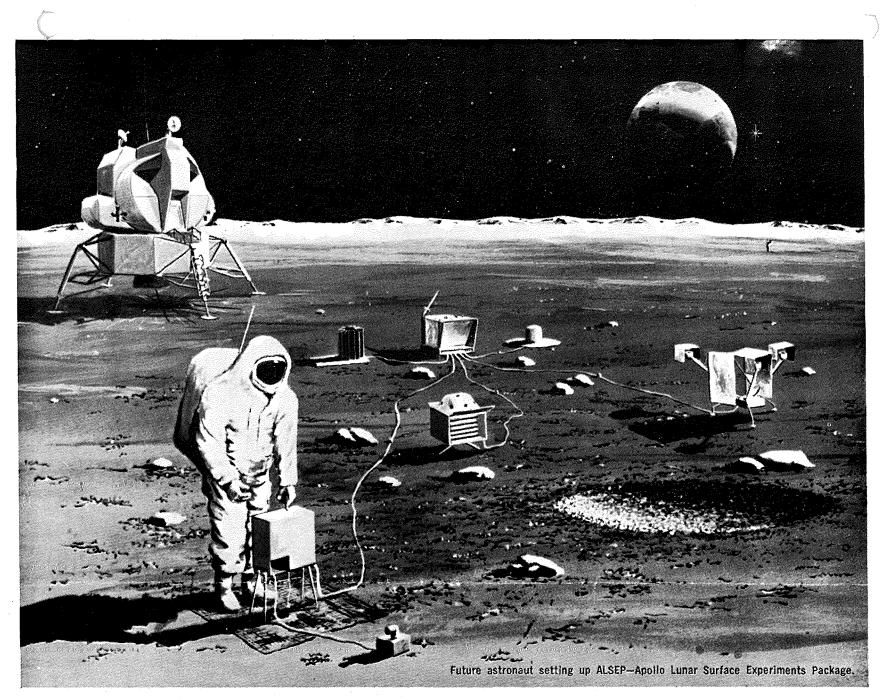

FIGURE 1.0-2 SIDE/CCGE DEPLOYED CONFIGURATION - PROTOTYPE

# ALSEP SYSTEM OBJECTIVES

DETERMINE LUNAR CHARACTERISTICS ( • INTERNAL STRUCTURE & COMPOSITION • STATE OF INTERIOR • COMPOSITION OF ATMOSPHERE • GENESIS OF SURFACE FEATURES

> THIS LUNAR INFORMATION WILL PROVIDE NEW INSIGHTS INTO THE GEOLOGY & GEOPHYSICS OF THE EARTH.

Page

FIG 1.0-3

# SUPRATHERMAL ION DETECTOR/COLD CATHODE GAUGE NASA NO. SO36 EXPERIMENT

OBJECTIVE: IONOSPHERE/ATMOSPHERE CHARACTERISTICS, POSSIBILITY OF VOLCANIC PROCESSES, AMBIENT ELECTRIC FIELD EFFECTS.

MEASUREMENT: FLUX, COMPOSITION, ENERGY, & VELOCITY OF LOW-ENERGY POSITIVE IONS; HIGH-ENERGY SOLAR WIND FLUX; TOTAL PRESSURE

EQUIPMENT: TWO CURVED - PLATE ANALYZERS (ONE WITH VELOCITY FILTER), GROUND PLANE, COLD CATHODE ION GAGE

FIG 1.0-4 SIDE COGE OBJECTIVES SUMMARY

# STOWED CONFIGURATION

δ

FIG 1.0-5

# ALSEP EXPERIMENT OBJECTIVES

| •                  |                          |             |            | OBJECTI    | VES          |

|--------------------|--------------------------|-------------|------------|------------|--------------|

| i                  | L.S.                     | MAL STRUCTU | OF OR MR   | STICN OF   | S OF HATURES |

| EXPERIMENTS        | $\sum_{l_{H_i}}^{\beta}$ | ON ST       | Or OR COMP | NOT GET SU |              |

| PASSIVE SEISMIC    | Х                        | Х           |            | Х          |              |

| ACTIVE SEIMIC      | X                        |             |            | X          |              |

| MAGNETOMETER       | X                        | X           |            | Х          |              |

| SOLAR WIND         | X                        |             | x          | Х          | 5            |

| - SUPRATHERMAL ION |                          | X           | X          | X          | <<           |

| HEAT FLOW          | x                        | X           |            | Х          |              |

| CHARGED - PARTICLE | }                        |             | X          | :          |              |

FIG 1.0-8

Page 9

# ALSEP EXPERIMENTS

| NASA NO. | EXPERIMENT          | PRINCIPAL INVESTIGATOR              |

|----------|---------------------|-------------------------------------|

| S031     | PASSIVE SEISMIC     | DR. G.V. LATHAM. COLUMBIA           |

| S033     | ACTIVE SEISMIC      | DR. R.L. KOVACH, STANFORD           |

| S034     | MAGNETOMETER        | DR. C.P. SONNETT, ARC               |

| S035     | SOLAR WIND          | DR. C.W. SNYDER, JPL                |

| S036     | SUPRATHERMAL ION    | DR. J.W. FREEMAN, RICE              |

| S037     | HEAT FLOW           | DR. M.G. LANGSETH, COLUMBIA         |

| S038     | CHARGED - PARTICLE  | DR. B.J. O'BRIEN, RICE              |

| S 0 5 8  | COLD CATHODE GAUGE* | DR. F.S. JOHNSON, U OF TEXAS DALLAS |

| S059     | LUNAR FIELD GEOL.** | DR. E.M. SHOEMAKER, USGS            |

\* INCLUDED IN SUPRATHERMAL ION ON CERTAIN FLIGHTS

Page

10

\*\* EQUIP. PARTIALLY CARRIED BY ALSEP

FIG 1.0-9

# SIDE GENERAL FEATURES

|                                                                                                                                                                                                                                                                                                                                   | MEASURE IONIC ENVIRONMENT OF MOON                                                                                                                                     |                                           |                                                                                                                                                       |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                   | FROM UV IONI-<br>THE LUNAR AT-<br>AMING &<br>ZED                                                                                                                      |                                           | DETERMINED BY CCIG:<br>• DENSITY OF LUNAR<br>ATMOSPHERE (INC<br>CHANGES WITH TIME)<br>• RATE LOSS OF CON-<br>TAMINANTS LEFT BY<br>ASTRONAUT & LM      |  |  |

| ANALYZER (HECPA)<br>• NO VELOCITY FILTER<br>• DETERMINES FLUX<br>(PARTICLES/SEC)<br>WITHIN STEPPED                                                                                                                                                                                                                                | LOW ENERGY CUR<br>PLATE ANALYZER<br>(LEC PA)<br>• PRECEDED BY V<br>FILTER (CROSSE<br>ELECTRIC & MAC<br>FIELDS)<br>• DETERMINES FLU<br>(PARTICLES/SEC<br>STEPPED RANGE | ELOCITY<br>D<br>GNETIC<br>JX<br>C) WITHIN | <ul> <li>MEASURES DENSITY OF<br/>NEUTRAL ATOMS (THIS,<br/>WITH TEMP OF GAUGE,<br/>ALLOWS CALCULATION<br/>OF LUNAR ATMOSPHERE<br/>PRESSURE)</li> </ul> |  |  |

| <ul> <li>VELOCITY &amp; ENERGY PER<br/>UNIT CHARGE</li> <li>PLACED ON GROUND PLANE (WIRE MESH SCREEN)<br/>WITH VOLTAGE APPLIED BETWEEN INSTRUMENT &amp;<br/>SCREEN TO ASSESS LUNAR SURFACE ELECTRICAL<br/>FIELD EFFECTS</li> <li>SIDE ELECTRONICS INPUT CIRCUITS PROVIDE<br/>ISOLATION FROM ALSEP (POWER &amp; SIGNAL)</li> </ul> |                                                                                                                                                                       |                                           |                                                                                                                                                       |  |  |

FIG 1.0-10

Page

## 2.0 PROGRAM HISTORY

### 2.1 Introduction

The ALSEP/SIDE/CCGE Experiment was designed, fabricated, tested, and delivered by Marshall Laboratories, Torrance, California, under contract to William Marsh Rice University, Houston, Texas. The original contract was executed on 8 June 1966; delivery of the last unit took place in December of 1968.

Designated contract number is S1966-14, under Prime Contract number NAS 9-5911.

The following presentation of program highlights includes a summary of major design and status meetings, design evolution, delivery schedules, problem areas, solutions, and improvements.

### 2.2 Program Meetings

During the course of the project, numerous program and review meetings were conducted to insure proper continuity of direction, configuration, design, and rework. Various design features and their problems were discussed in these meetings, as well as new designs implemented to further improve the instrument. Progress of the program was periodically reviewed.

Typical of the major design reviews held are the following:

In November of 1966, an ALSEP Preliminary Design Review was held at Bendix Aerospace Systems Division to review the Bendix system design, with emphasis given on the interfaces between the various experiments. Particular attention was given to vibration and shock problems, and to power system interface problems.

A major Experiment Status Review meeting was held at Marshall Laboratories in December, 1966. Major topics included program management, scheduling, staffing, and costing; status of design, fabrication, parts procurement, and other technical aspects of the program were discussed in depth.

Typical of the Program Review Meetings was the meeting held at Marshall Laboratories in June, 1967. Design status was reviewed including electrical, thermal, and mechanical design features. Costs and schedules were analyzed in depth. In addition to Rice University and Marshall Laboratories participants, attendees included representatives from NASA/MSC, SCAS and Bendix Corporation.

The Critical Design Review (CDR) was conducted at Marshall Laboratories in August, 1967. The purpose of the meeting was to cover problem areas brought to light by the engineering and prototype models. The CDR also set up as a baseline for configuration control. Various faults and virtues of the experiment design

#### Page 13

were discussed, and recommendations for further improvements were introduced. The presentations covered both the electrical and mechanical aspects of the equipment. A major ALSEP Interface Meeting was held at Bendix in September (1967), with the Principal Investigators of each ALSEP experiment in attendance. Topics of interest were organizational status reports, overall schedule status, accomplishments to date, and problem areas.

Another major Program Review Meeting took place at Rice University in February of 1968. Items reviewed were the CCGE status (including fabrication, delivery schedule, and calibration). SIDE status and discrepancy reports were covered in addition to interface and technical problem areas. Astronaut deployment problems were reviewed.

The forlegoing were typical of the main review meetings which were held periodically to insure smooth progress of the program and successful attainment of its goals.

### 2.3 Design Evolution

The initial design concept of the experiment was an extension of the Suprathermal Ion Experiment for the Advanced Technology Satellite (ATS) - B spacecraft, with the addition of a crossed field analyzer to serve as a velocity filter. This concept was later modified to include a second detector to measure higher energy ions, with open retarding grids for particle deflection. The addition of the CCGE experiment was anticipated early in the program but parameter definitions and corresponding contractual documentation were not available until after the preliminary design phases of the program.

Significant design changes were introduced which produced a radically different instrument than that originally conceived, making it much more valuable as a scientific instrument. These changes were implemented successfully in spite of demanding schedule requirements. With an intensive design effort, Marshall Laboratories succeeded in producing a complex, highly sophisticated instrument incorporating over 500 transistors and a similar number of integrated circuits.

A summary review of the major design changes follows:

Instead of the proposed time-shared retarding potential analyzer system with a 39 bit digital readout, the design of the instrument evolved into two simultaneously operating curved plate analyzer ion detectors with 100-bit digital readout. As mentioned previously, the Cold Cathode Gauge was incorporated including a separate +4.5 kV power supply and a five decade multi-ranging electrometer. The CCGE sensor had a major impact on form factor and thermal design constraints. The original velocity filter concept was to sequentially step

#### Page 14

through one to five different energies in order to gather data in each of the selected velocity bands. The velocity filter redesign incorporated sequencing steps which tracked a parabolic curve of voltage versus time. This introduced many additional voltage steps with a corresponding increase in design complexity.

During the design of the ALSEP Experiment, it was suggested that a backup (analog) data link be established between the experiment and the analog signal processing circuitry of the ALSEP. Rice University agreed that the addition of this circuitry was a benefit to the experiment and authorized the addition of the log count rate meters to the experiment design. In effect, the addition of this circuitry improved total system reliability by providing a redundant, though less precise, path around much of the circuitry of the instrument.

The decision to include a magnetic shield for the CCIG had considerable impact upon weight problems and subsequent weight reduction efforts. Similarly, a larger size cable reel for the flattape cable resulted in problems involving weight and thermal control considerations.

These challenges were met in major mechanical and thermal redesign efforts to produce an instrument which would survive the specified environmental design constraints. Refer to Section 7.0 for details on mechanical and thermal design.

#### 2.4 Test and Delivery Schedules

Successful integration of the experiment breadboard with the breadboard ALSEP Central Station was accomplished at Bendix Systems Division in December, 1966. Interface tests on the CCIG with the electrometer and high voltage power supply breadboards were performed the following month at NRC, Boston, Massachusetts. Acceptance tests for the SIDE and CCGE breadboards, were conducted in February, 1967. At this time, ETS (Experiment Test Set) acceptance tests were also performed. All test objectives were satisfactorily completed.

Severe schedule pressure characterized much of the program's activities. This was necessitated by the need to conform to overall ALSEP Program schedule requirements. Early in 1968, an incentivized redefinition of the contract provided for a new delivery schedule in which delivery of instruments would be accomplished at six week intervals. Marshall Laboratories successfully met all schedules and thus qualified for the incentive fee as provided for in the modified contract.

The following is a brief summary of the required delivery dates for incentivized purposes and actual delivery dates.

| System                                  | Incentivized<br>Contractual Delivery<br>Date | Actual Delivery<br>Date | Remarks<br>(See Section<br>2.5 for details)  |

|-----------------------------------------|----------------------------------------------|-------------------------|----------------------------------------------|

| ML322-1                                 | N/A                                          | May 1967                | Shipped with<br>authorized<br>tolerance dis- |

| (Engineering<br>Model 1)                |                                              |                         | crepancies                                   |

| ML322-2                                 | N/A                                          | July 1967               |                                              |

| (Engineering<br>Model 2,<br>prototype)  |                                              |                         |                                              |

| ML323-1                                 | N/A                                          | Sept. 1967              | HV arcing at                                 |

| (Qual Model2)                           | *                                            |                         | Rice, Nov. 1967                              |

| ML323-2<br>(Qual Model 1)<br>(Flight 1) | N/A                                          | Jan. 1968               | HV arcing,<br>Feb. – March<br>1968 at Rice   |

| ML323-3<br>(Flight 2)                   | April 1968                                   | March 1968              | -3.5KV and<br>Elect. problems<br>at Rice     |

| ML323-4<br>(Flight 1 <b>) (S</b> par    | May 1968<br>e)                               | May 1968                |                                              |

| ML323-5<br>(Flight 3),                  | July 1968                                    | July 1968               |                                              |

| ML323-6<br>(Qual. 2)                    | August 1968                                  | August 1968             |                                              |

| ML323-7<br>(Flight 3) (Spar             | Sept. 1968<br>                               | Sept. 1968              |                                              |

| ML323-8<br>(Flight Spare)               | Nov. 1968                                    | Nov. 1968               |                                              |

| ML323-9<br>(Flight Spare)               | Dec. 1968                                    | Dec. 1968               |                                              |

See Appendix III for a system test procedure and typical test results.

\* The Qualification Model No. 1 instrument had been reidentified as Qualification Model No. 2. Therefore all data acceptance documentation prior to 2 January 1968 referenced to Qualification Model No. 1 is now applicable to the re-identified Qualification Model No. 2 instrument.

Two Astronaut Training Units (ATU) were developed and delivered to the customer. The ATU's provide a means for accurate physical simulation of the actual instrument. The development of the ATU's was influenced by human interface requirements involving the astronauts' training needs.

ATU serial number 1 was completed and shipped to Bendix in May of 1967. It was subsequently returned to Marshall Laboratories for modifications in September, 1967. After updating, ATU No. 1 was then shipped to MSC in December of the same year.

ATU No. 2 was completed and delivered in February,

1967.

2.5 Problem Areas and Solutions

Engineering Model 1 (EM 1, ML 322-1), was tested and shipped with minor tolerance discrepancies due to non-screened, lower precision substitute components used in the system. These lower precision parts were authorized for EM 1, a non-flight configuration, and applied only to EM 1. Blivet 800 (see Sect. 3.0 for description) not in final configuration, was to be retrofitted at a later date, as was the 700 Blivet.

A failure was observed in the instrument ML 323-1 during tests at Rice University in November of 1967. Failure occurred when the + 4.5 kV power supply was turned on in the vacuum chamber (at pressure of  $2 \times 10^{-6}$  torr). All negative power supply voltage readings were 255 (on ETS data display readout unit) except for the -5 volt supply. All internal temperatures read out 000.

The problem was traced to damage caused by high voltage arcing. Rerouting of critical ground connections and the addition of arc protective devices in the applicable modules corrected the problem. The -3.5 kV high voltage to the channeltrons was originally an independent connection from the 700 blivet. It now encompasses two connections, one from the 700 blivet to the low energy channeltron and one connecting the low energy channeltron to the high energy channeltron. Refer to Engineering Change Proposals (ECP) 116 through 122 (Appendix III). The instrument was shipped back to Rice University in December.

Qual Model 1, ML 323-2 was returned to Marshall Laboratories in February 1968 for the following repairs and modifications:

- o Installation of Ground Screen Spring

- o Installation of Latch Pin Lanyard

- o Modification of CCIG Lanyard Wire to Stainless Steel Wire

- o Retrofit Dust Cover Springs

- o Addition of two (2) Apertures to LECPA

- o Addition of two (2) Pole Straps to LECPA Magnet Assembly

- Repair of 600 Blivet Assembly to Correct the Following Conditions:

- a) Temperature Monitor No. 6

- b) -3.5 kV Arcing

- c) -3.5 kV Monitor

- o Repair of 700 Blivet Assembly to Correct the Following Conditions:

- a) -3.5 kV Monitor

- b) 4.5 kV Command Sequence

- c) -3.5 kV Arcing

Refer to ECP's 187 and 188 for changes involving protective circuitry to prevent damage due to high voltage arcing (Appendix III).

This instrument was retested and shipped to Rice University in March, 1968.

In the same month, ML 323-2 (Qual Model 1) was subjected to massive high voltage arcing and the instrument was returned to Marshall Laboratories. Investigation showed damage to a number of modules due to the arcing. Various changes were initiated to prevent further failures of this type. Refer to ECP's 210 and 218 (Appendix III). The instrument was repaired, final tested, and returned to Rice University in April, 1968.

The Qual Model spare (ML 323-3) was final tested and shipped to Rice University in March (1968). During system vacuum tests at Rice, the -3.5 kV supply would turn on and off intermittently. An electrometer failure was also observed, apparently due to a ground loop problem in the Rice University system test configuration. After the instrument was returned to Marshall Laboratories, repairs were performed on the equipment; final re-test and shipping occured in May.

In April, 1968, instrument number ML 323-1 (Qual Model 2) reportedly exhibited a power short during tests at Bendix. The instrument was subsequently returned to Marshall Laboratories.

Upon receipt of the SIDE/CCGE instrument at Marshall Labs, a thorough investigation of the reported power short was performed. A variety of turn on sequences and operations were tested in addition to physical movement of the package and associated cables. It was impossible to induce a short circuit failure. After disassembly of the instrument, a visual inspection of potential areas of short circuits was performed and no defects were found.

ML did not have a suitable adapter cable to test the instrument in the same cable configuration as at Bendix. From the evidence provided, it appeared that a short circuit existed at the power input to the instrument due to an intermittent condition in either the SIDE/CCGE, the ETS, the cables, or cable connectors. From the information provided, it was not possible to isolate the particular cause of the short.

During vacuum tests of ML 323-1 at Bendix in August (1968), the environmental chamber had a port window implode, resulting in loss of vacuum and causing oil to spew over the instrument. Debris was also thrown on the instrument due to this port failure. During the time of the implosion, the SIDE high voltage was on, causing damage of an A/D converter. The instrument was subsequently returned to Marshall Laboratories, and was repaired and shipped out in September, 1968.

In summary, the major problems associated with early systems were damages resulting from high voltage arcing. Investigations concluded that arcing resulted from a combination of circumstances including insufficient gap distances, outgassing, improper cable routing in test chamber, etc. These problems were subsequently corrected and the SIDE/CCGE circuitry was modified to provide a greater degree of arc protection to sensitive circuits. The success of these efforts is evidenced by the virtual elimination of arc damage during tests conducted on later systems after Serial Number 4.

# 3.0 EXPERIMENT DESCRIPTION

This section describes the overall operation of the SIDE and CCGE experiments. A general description of the experiment, plus references to the appendix of typical test procedures and results, design notes, and other pertinent data is included in this and other appropriate sections.

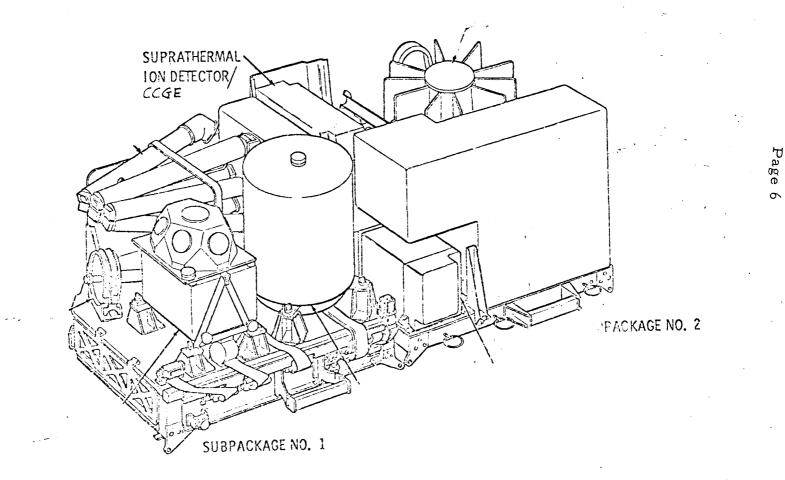

Physically, the SIDE/CCGE experiment consists of three major sections:

- a) Sensors

- b) Electronics

- c) Housing

The sensors portion includes the Low Energy ion detector, the High Energy ion detector, and the Cold Cathode Ion Gauge (CCIG). The electronic portion consists of nine subassemblies or blivets numbered 100 to 900 and two channeltron preamplifiers. The housing portion is in two parts - the internal chassis and the external chassis (Refer to Section 7.0 - Mechanical and Thermal Design). The internal chassis contains the sensors and the electronics, while the external chassis provides protection and thermal insulation to the internal chassis assembly. Each subassembly, or blivet, is tested in house over the applicable temperature range.

The following is a summary of the SIDE/CCGE subassemblies (blivets) and their major functions:

| a) | Blivet 100          | Logic Timing, Command System, Strobe<br>Gates, SIDE Frame Counter, Accumulators.                                                                            |

|----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b) | Blivet 200          | A/D Converters, ALSEP/SIDE Interface<br>Networks, Logic Timing, Sub-commutators,<br>CCGE Cal Command Generator, Dust Cover<br>Removal Circuit, Cal Dividers |

| c) | Blivet 300          | Step Voltage Counters & Generators, Cal<br>Pulse Generator                                                                                                  |

| d) | Blivets 400/<br>500 | Low Voltage Power Supply                                                                                                                                    |

| e) | Blivet 600          | Cal Shapers, Deadtime Circuits, Log Count<br>Rate Meters, -3.5 kV Regulator                                                                                 |

| f) | Blivet 700          | -3.5 kV Converter & Multiplier, 4.5 kV<br>Multiplier and Output Divider                                                                                     |

| g) | Blivet 800 | Electrometer for CCGE                                                                                            |

|----|------------|------------------------------------------------------------------------------------------------------------------|

| h) | Blivet 900 | 4.5 kV Regulator and Converter, Electro-<br>meter Range Relay Drivers & Power Supply,<br>CCGE Seal Break Circuit |

See Section 7.0 Mechanical and Thermal Design, for the physical configuration of the blivets within the experiment package.

Since the experiment is thermally insulated and heated by an automatic heater control circuit, it will operate throughout the range of the lunar temperatures  $(-157^{\circ}C \text{ to } +121^{\circ}C)$  while the temperature inside the unit is maintained between  $-10^{\circ}C$  and  $+60^{\circ}C$ .

Electrically, the system is completely isolated from the ALSEP to achieve an ideal floating ground configuration. The direct-current isolation resistance is greater than 10 M $\Omega$ . The isolation voltage is greater than  $\pm$  50 volts.

A Ground Plane screen is placed beneath the instrument as it is deployed on the lunar surface (See Figures 1.0-2, 1.0-3 and 1.0-7, and Section 7.1.8). A stepped voltage is applied to the Ground Plane to modify the ambient lunar surface potential.

The system is linked to the ALSEP Central Processing Station by a flat-tape cable. Power, commands, timing signals, and data are transmitted through this cable.

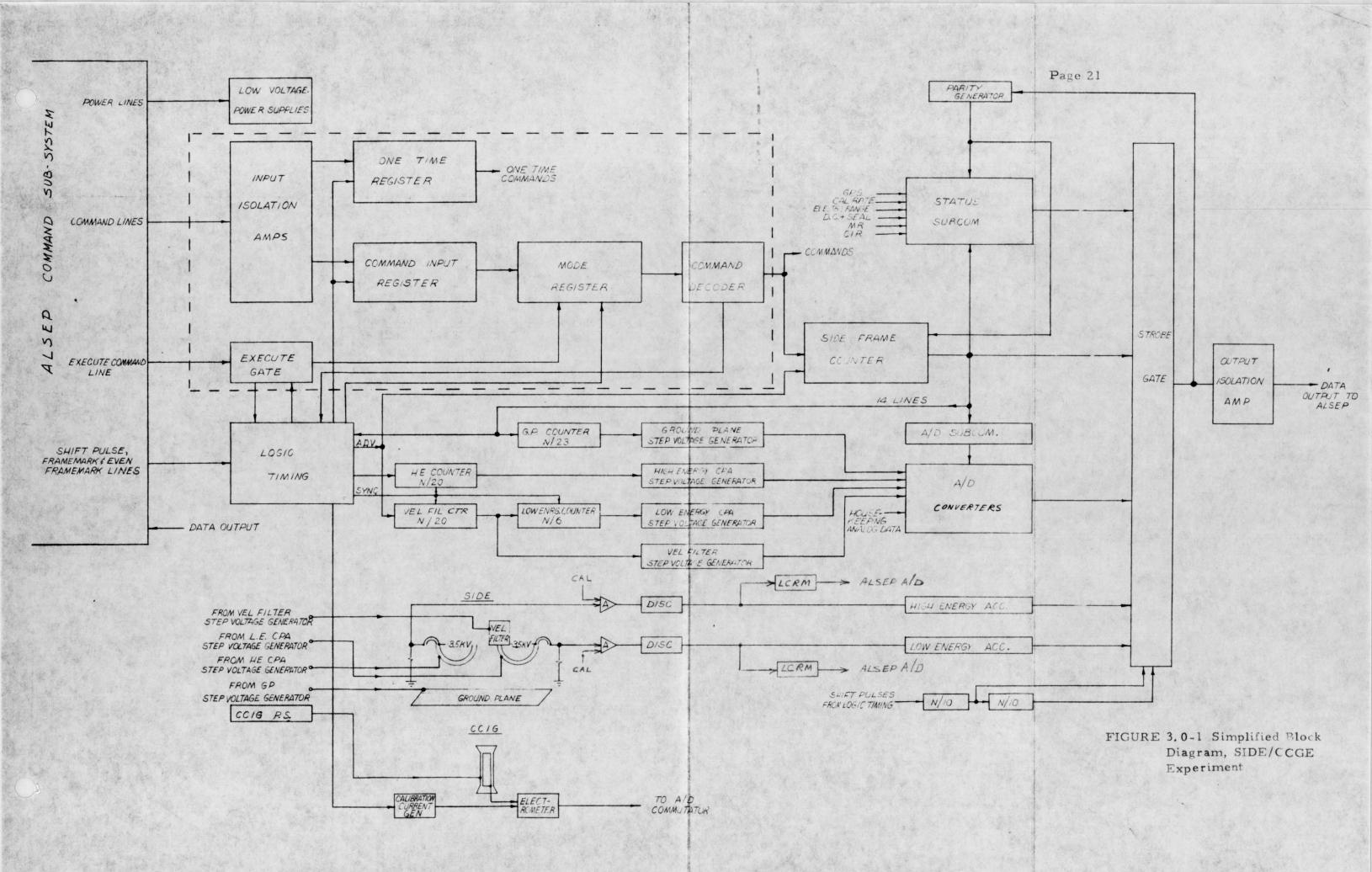

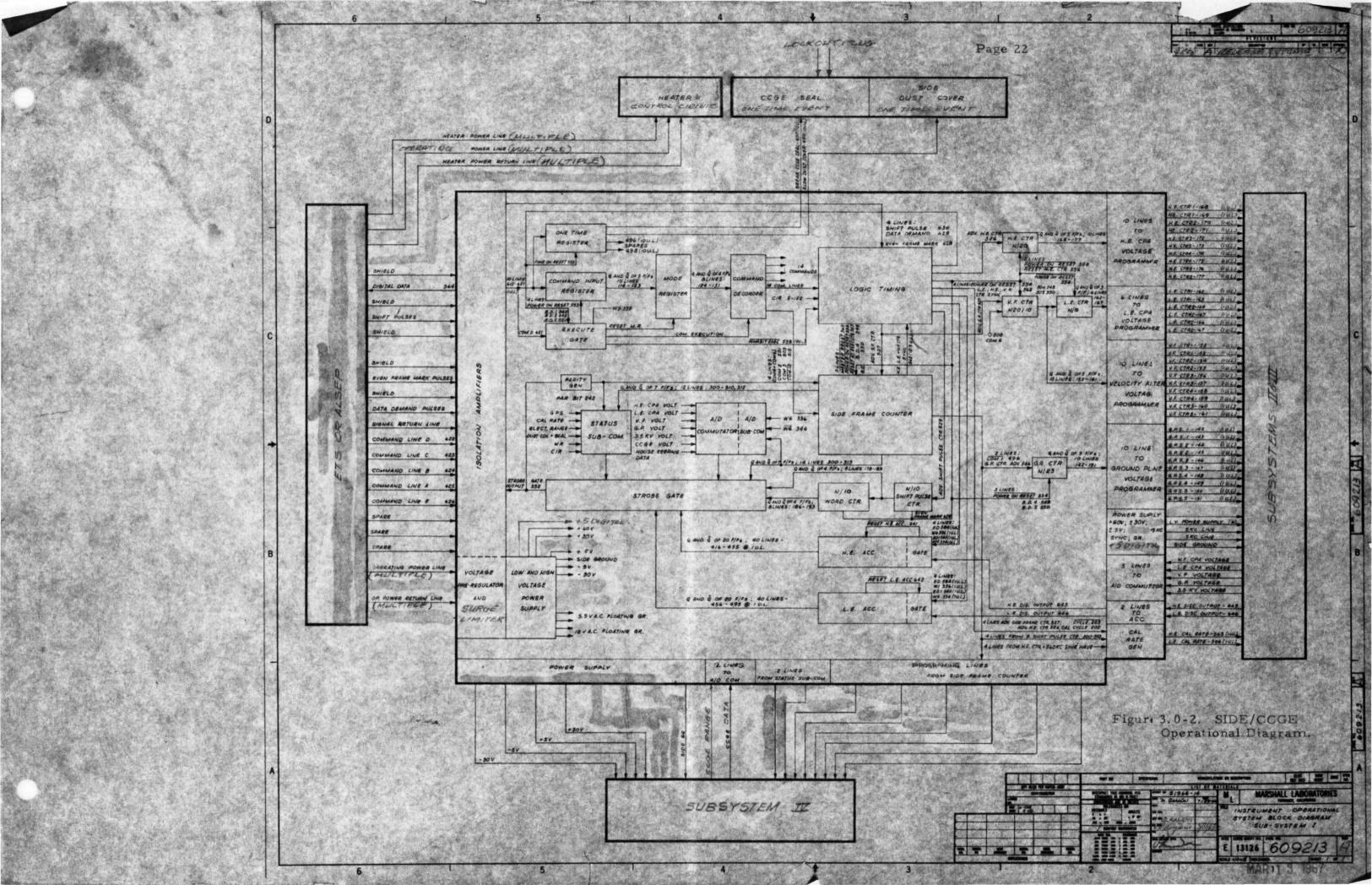

Refer to the following figures for the system block diagram and data formats:

| a) | Figure 3.0-1, | Simplified Block Diagram, SIDE/CCGE Experiment |

|----|---------------|------------------------------------------------|

| b) | Figure 3.0-2, | SIDE/CCGE Operational Diagram                  |

| c) | Figure 3.0-3, | A/D & Status Sub-Com Sequence                  |

| d) | Figure 3.0-4, | Data Format                                    |

Functionally, the instrument consists of four major portions: a) a low energy ion detection system, b) a high energy ion detection system, c) the CCGE, and d) the support electronics. Provisions are also made for in-flight calibration. A calibration pulser drives through logic controlled by the Master Timing Generator (SIDE Frame Counter and associated logic timing circuits), and provides calibration signals to the Channeltron Preamplifiers during the experiment's calibration cycle.

| FIA. | 10           | 8 | LU . |

|------|--------------|---|------|

| 609  | 13156 000    |   | 200  |

|      | 13150 men un |   | PO0  |

|      | 1315         |   |      |

----

. 6

|                 | <u> </u>                   | 5            |                             | 1                                       |                             | 4           |                             | 19 38                       | 3                      |            | 1                     | 2                                        | 2                   |              | AUTE DEPAITON<br>CONNECT IN INCOMED                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|----------------------------|--------------|-----------------------------|-----------------------------------------|-----------------------------|-------------|-----------------------------|-----------------------------|------------------------|------------|-----------------------|------------------------------------------|---------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                            |              |                             |                                         |                             |             |                             |                             |                        | Page       | e 23                  |                                          |                     | 4 800 A      | A EVIEL<br>CHANSES NELC M<br>SIDE PEAMES 1<br>24,27,30,37,35<br>54,58,59,60,4<br>78,67,86,40,44<br>103,110,113 21                         | B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B         B |

|                 |                            |              |                             |                                         |                             |             |                             |                             |                        | 1          |                       |                                          |                     | 4 800 C      | FRAME 28 WAS + 15 V<br>B +1 MAS (CIG, FRAME 4<br>RANGE, ADLED CA. 20<br>C & BO AMLOS IN A 31.44.<br>D REVISE DWG.<br>E REVISE DWG + 82. W | 42 NAS CCIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0               | GP3                        | 16<br>GP3    | 305                         | 32                                      | 40<br>6=5                   | 48<br>6P5   | GPS 56                      | 64<br>GPS                   | GPS 72                 | 80<br>925  | 88<br>975             | 96<br>GP3                                | 0-5                 | 1/2<br>GPS   |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AVALOG          | +45 **                     | + 60 YOUTS   | CCGE RANJE                  | + & VOLTS<br>ANALOG                     | + 4.5 xr                    | +60 10175   | CCGE RANGE                  | ANALOG                      | - 4.6 Kr               | + 60 VOLTS | CEGE ANNUE            | + 5 VOLTS<br>ANALOG                      | *** **              | +60 10255    |                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1               | 9<br>ELECTRONITIK<br>RANGE | 17<br>C/R    | 25<br>ELECTROMETER<br>RANGE | 33                                      | 41<br>ELECTROMETER<br>RANGE | 49<br>C/R   | 57<br>ELECTROMETER<br>RAVAS | 65<br>E/R                   | 73<br>ELECTROMETER     | 81         | 89<br>FLECTAOMETER    | 97<br>c/A                                | 105<br>ELECTHOMETER | 113<br>CIR   | Contraction of the second s                           | La april                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| cess            | CCOS                       | + 30 VOLTS   | + 30 41 CAL                 | ONE THE COMMUND<br>RES STER SATUS       |                             | + 30 YOLTS  | 120.000 640                 | PRE-REG<br>DUTY PACTON      | CCGE                   | + 30 VOLTS | AANGE<br>+ 30 ANV CAL | CHE TIME CONVENE<br>MEGISTER STATUS      | ccar                | + 30 VOLTS   | ccor                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2               | ID<br>GPS                  | = 18<br>spz  | 26<br>3F5                   | 34                                      | 42                          | 50<br>805   | 58<br>8#5                   | 66<br>GFS                   | 74<br>GP5              | 82         | 90<br>GPS             |                                          | 106<br>5=5          | 114<br>GPS   | 122<br>CAL RATE 3                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

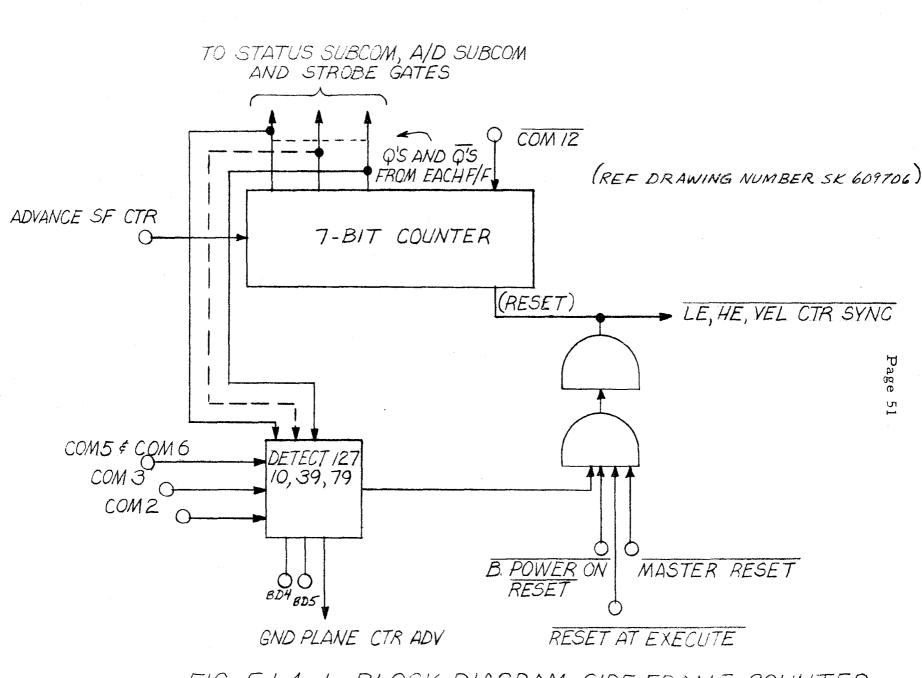

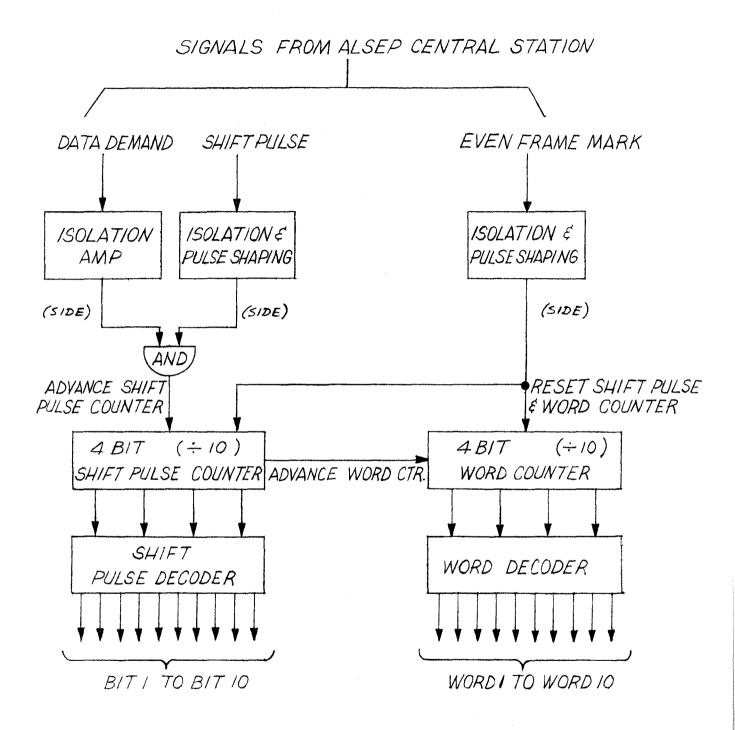

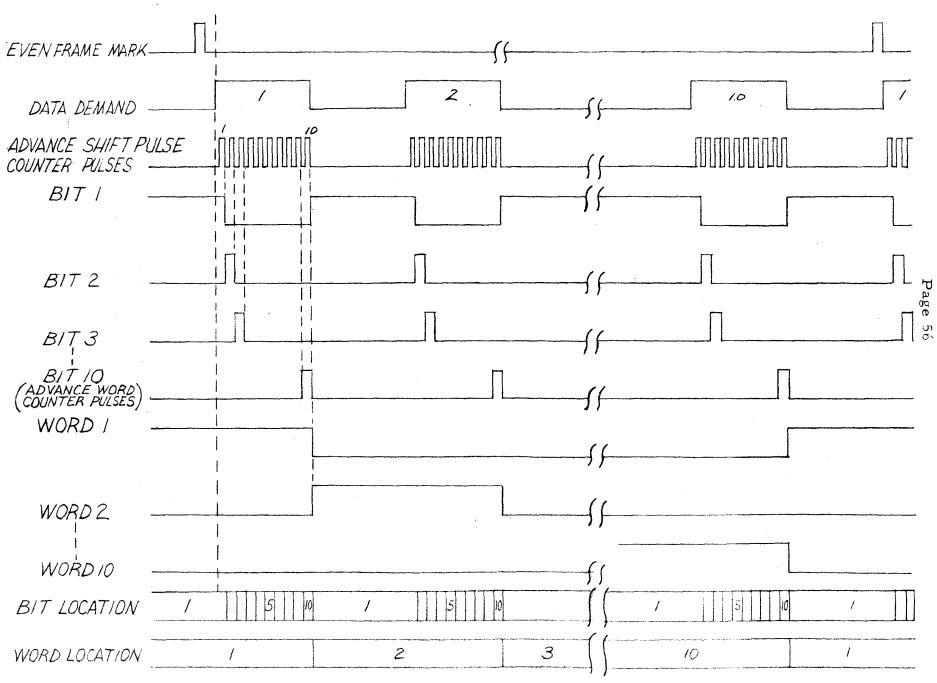

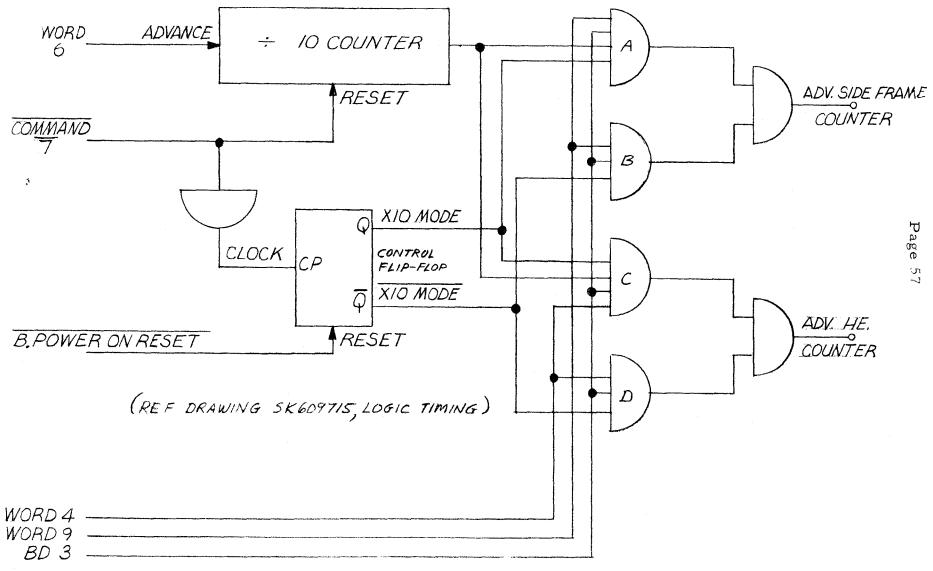

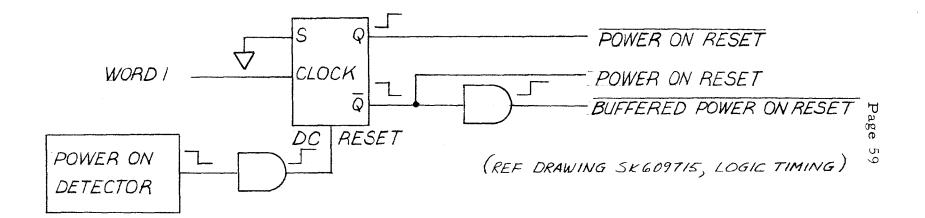

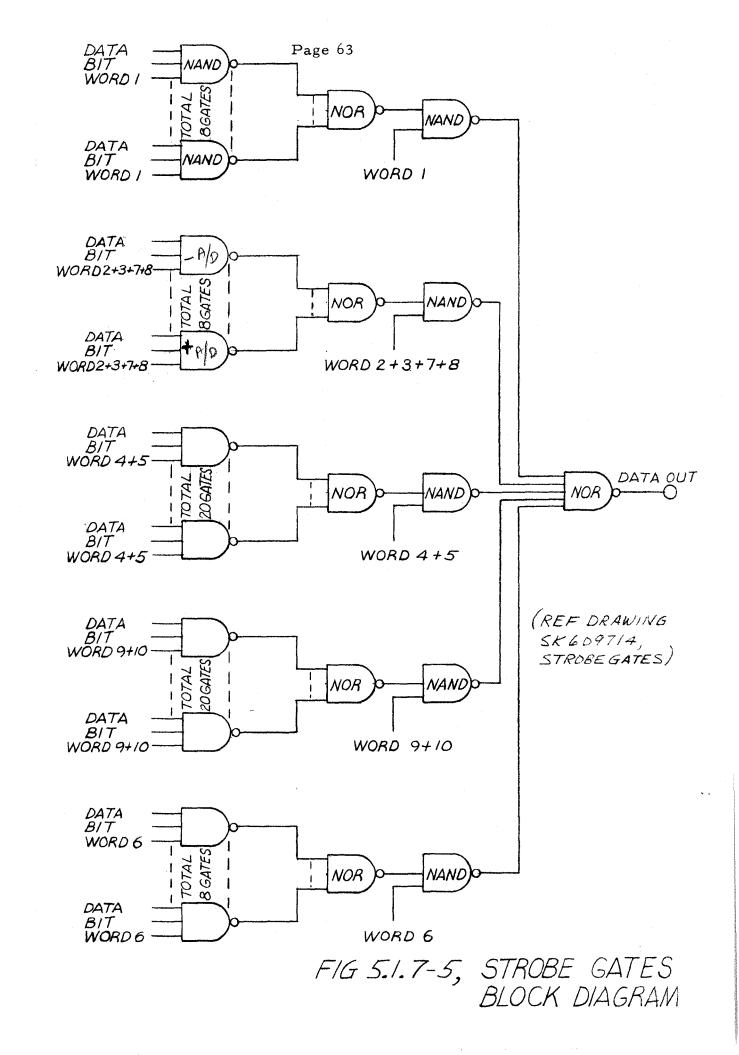

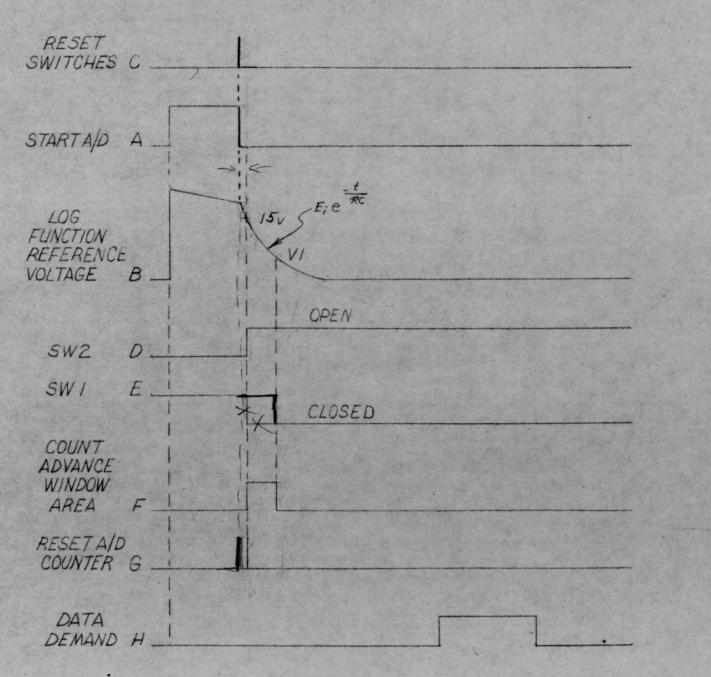

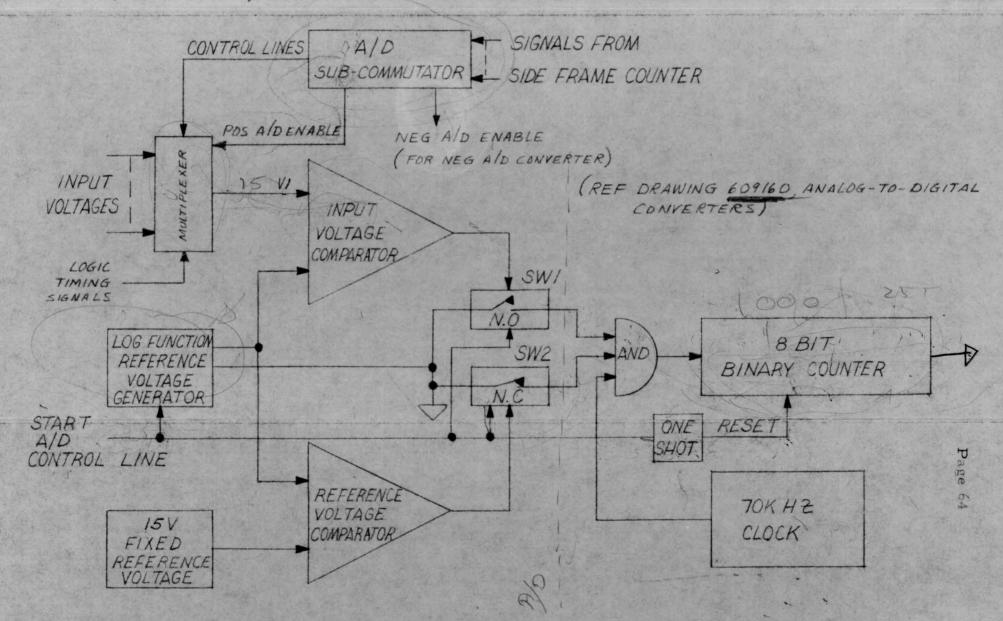

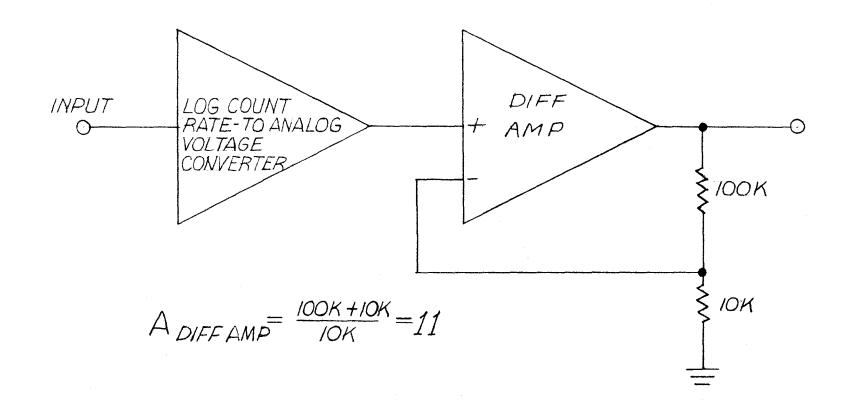

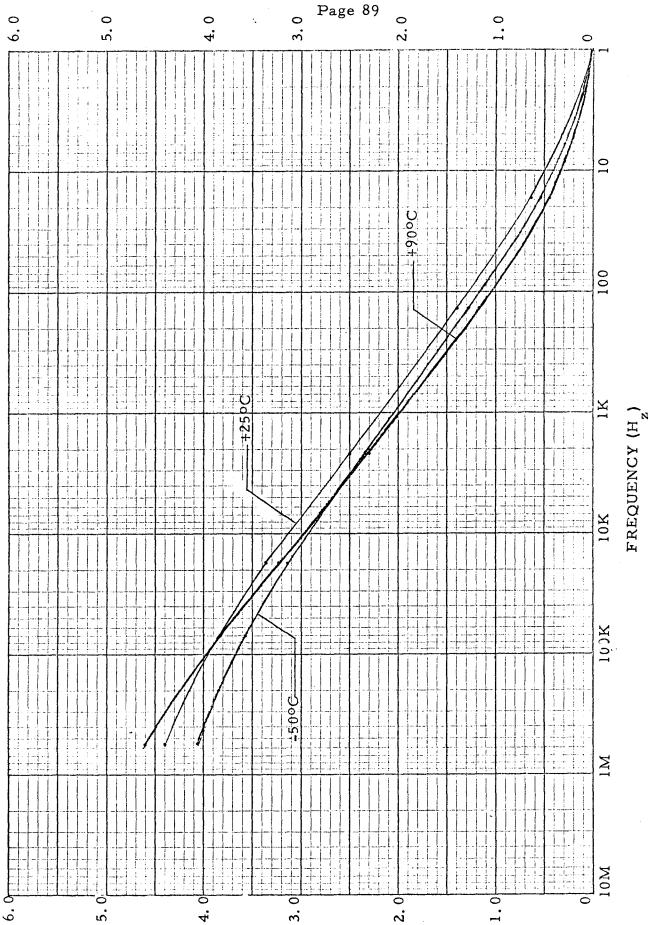

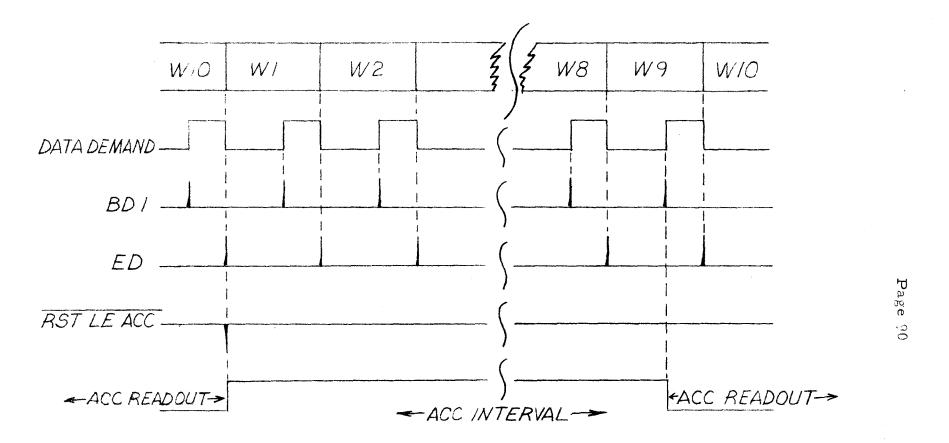

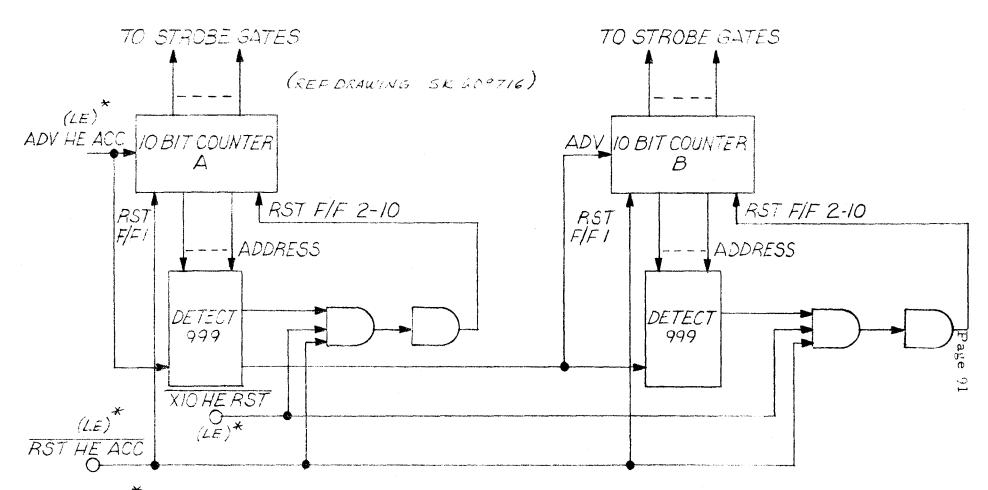

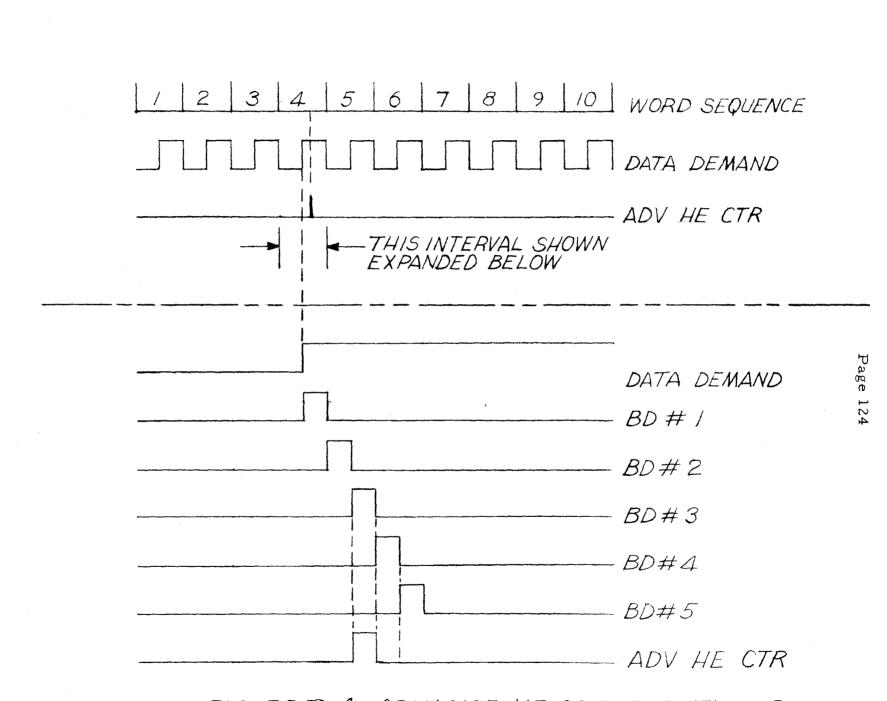

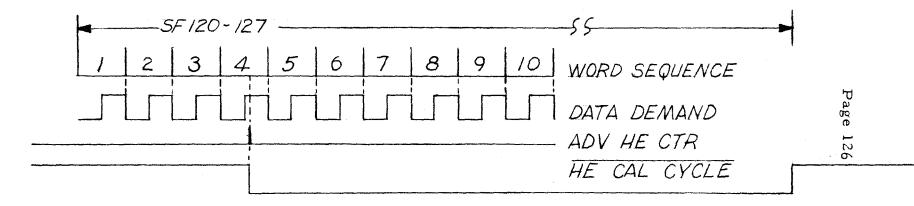

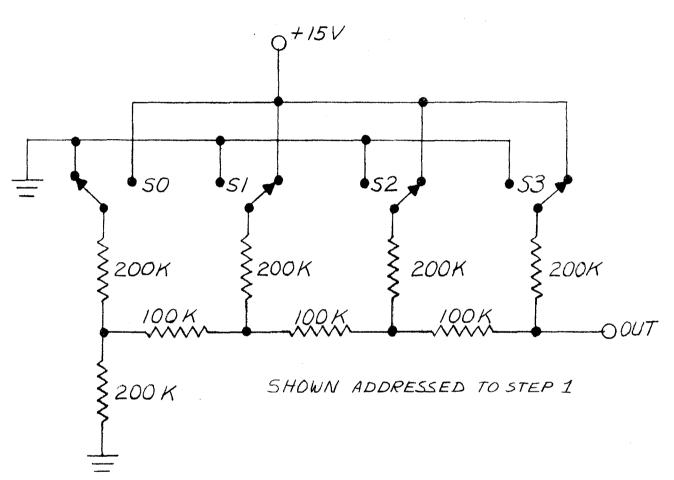

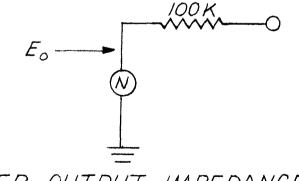

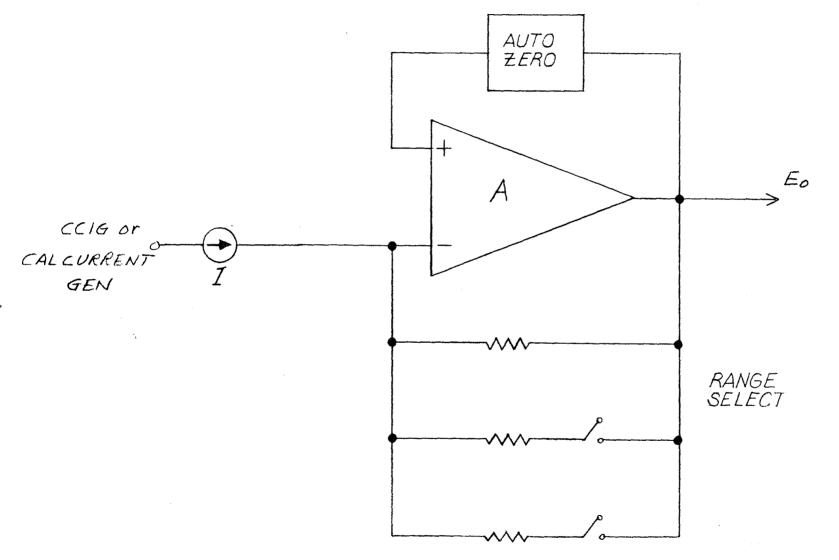

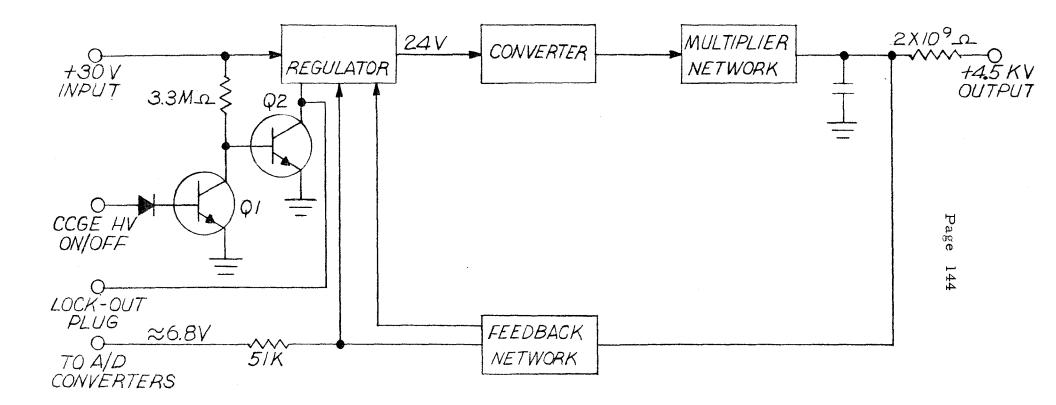

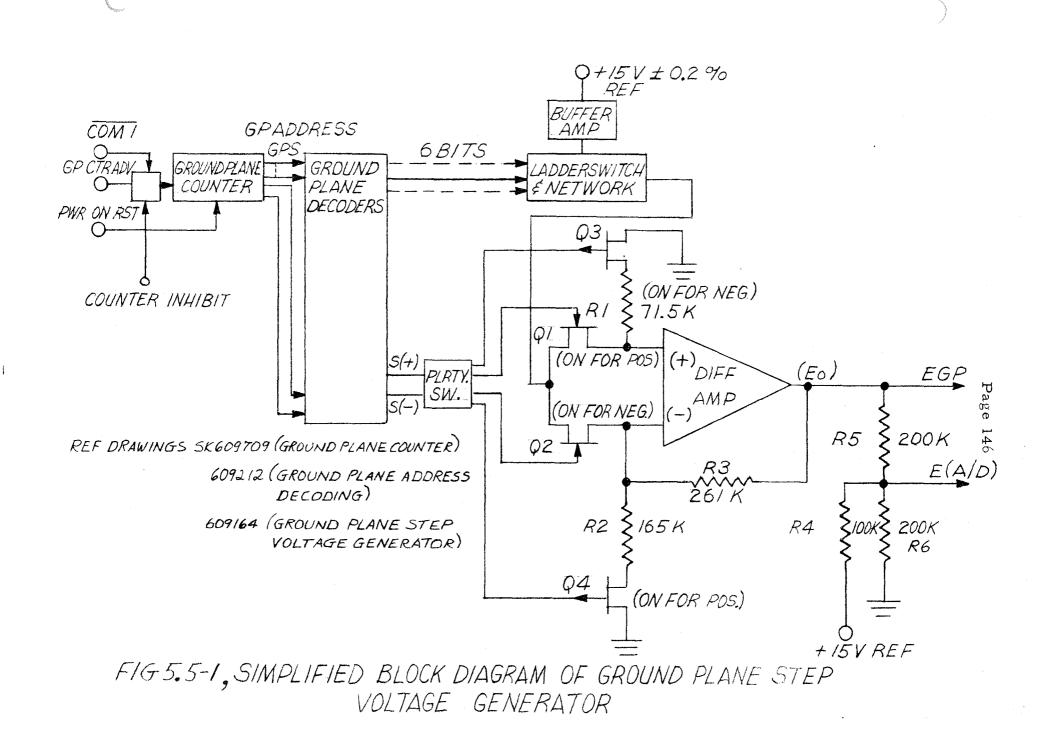

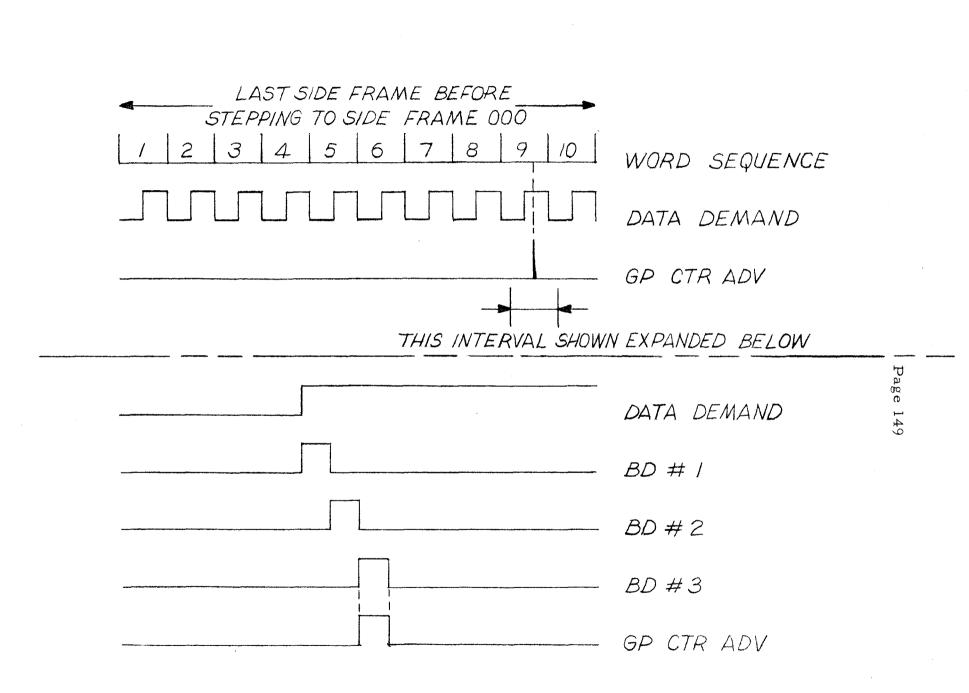

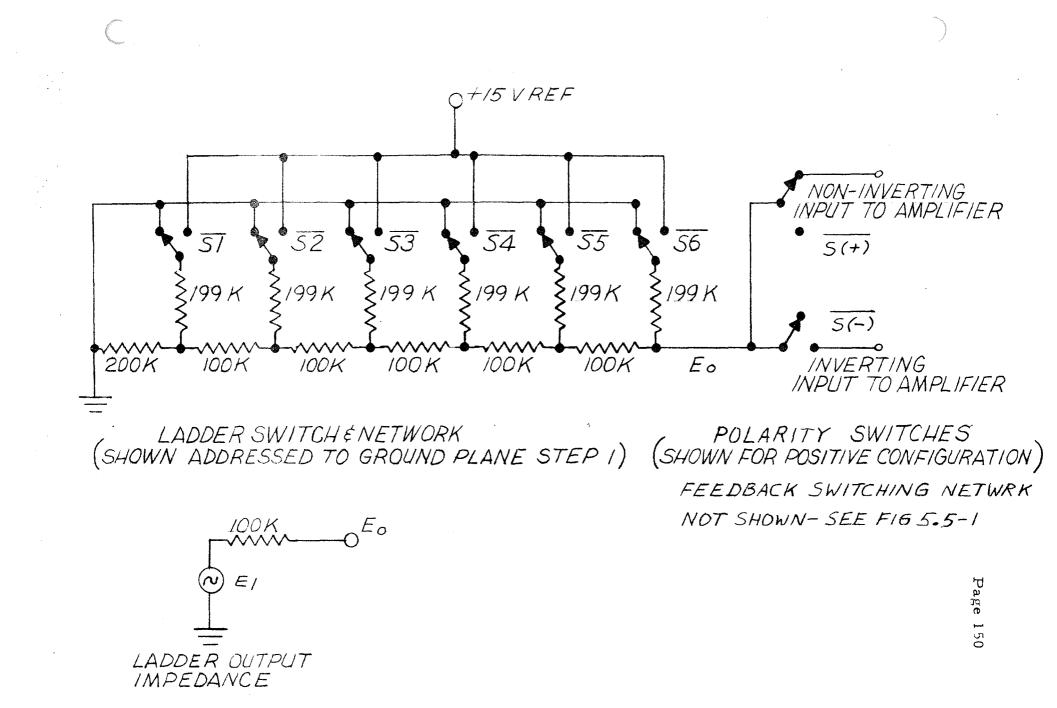

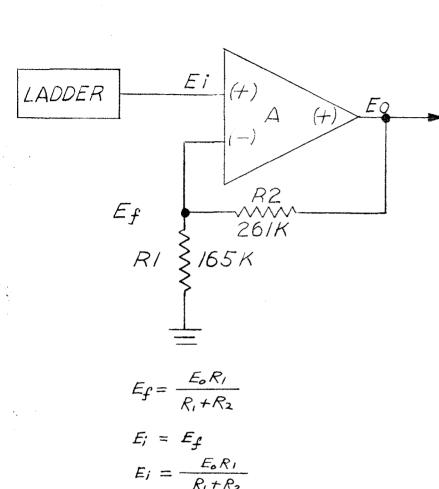

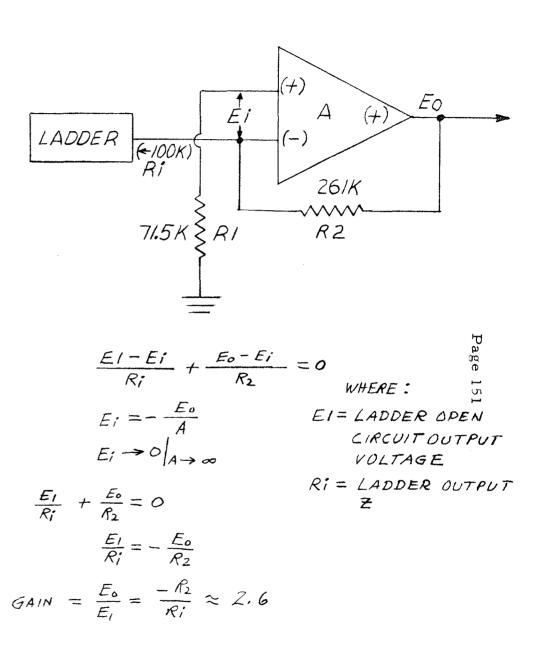

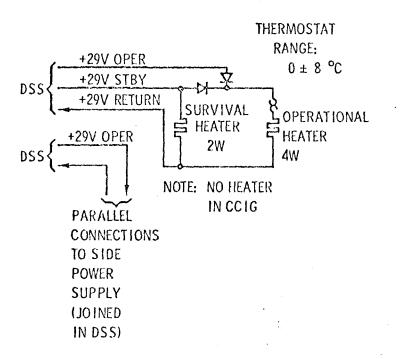

| TEMP = 1        | CEGERANDE A                | +5 V DIGITAL | + AID REP VOLTS             | TEMP 9                                  | CCGE HANSE                  | +5V DIGITAL | + AID REF 18275             | TEND = ;                    | CC 68 44185            | + 5 -OLTS  | + AID REF VOLTS       | TEMD = 1                                 |                     | + 5Y DIGITAL | ccas                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |